勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### 28F400BV/CV/CE 28F004BV/BE SPECIFICATION UPDATE

Release Date: February 1997

Order Number: 297595-013

# int<sub>e</sub>l. WWW.100Y.COM.TW

28F004/400BV/BE/CV/CE SPECIFICATION UPDATE

### CONTENTS

| REVISION HISTORY             | 勝特力材料 886-3-5753170                                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------------------|

| PREFACE                      | 胜特力电子(上海) 86-21-54151736<br>胜特力电子(深圳) 86-755-83298787                                                            |

| SUMMARY TABLES OF CHANGES    |                                                                                                                  |

| IDENTIFICATION INFORMATION   | COM 1                                                                                                            |

| ERRATA                       | N. W.W. LOOK.COM. TW                                                                                             |

| SPECIFICATION CHANGES        | N WWW. 1001.COMPTH                                                                                               |

|                              |                                                                                                                  |

| SPECIFICATION CLARIFICATIONS | and the second |

### REVISION HISTORY

| Date of Revision                                                    | Version           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01/16/95                                                            |                   | Initial release of this document. Includes the following:<br>Limited V <sub>CC</sub> Voltage, Reduced V <sub>LKO</sub> (Commercial/Automotive),<br>3.3V V <sub>CC</sub> /12V V <sub>PP</sub> Programming Erratum, t <sub>PHWL</sub> /t <sub>PHEL</sub> Pushout,<br>CE# delay from RP# High, t <sub>PLPH</sub> Reset Pulse Width, Erroneous<br>Erase Fail Flag Operation.                                                                                                                                                                                                                                                                                                                                                                                                                     |

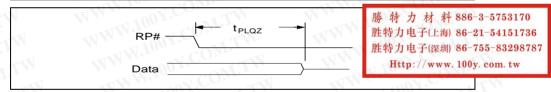

| 02/08/95                                                            | -002              | New erratum: $t_{PLQZ}$ - New Spec, False V <sub>PP</sub> Flag, Access Time.<br>Additional ID and erratum information for Erroneous Erase Fail<br>Flag erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 03/07/95                                                            | -003              | New erratum: t <sub>WHEH</sub> - CMOS Control Signals, CE# Timing<br>Erratum/ A <sub>-1</sub> Timing Erratum. Addition to False V <sub>PP</sub> Flag<br>Erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 03/22/95                                                            | -004              | Errata summary format changed to include more information.<br>Automotive $V_{LKO}$ erratum: spec changed from 3.5V to 2.0V.<br>Erase Fail Flag: Re-issue erase option added to resolution.<br>Address Timing: Erratum error corrected Affected pin is $A_{10}$ for<br>28F004, not $A_0$ as listed in Rev 003. Title also changed to<br>"Address Timing Erratum" from " $A_{-1}$ Timing Erratum."                                                                                                                                                                                                                                                                                                                                                                                             |

| 03/31/95                                                            | -005              | Access time erratum removed: no material ever affected by this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 04/13/95                                                            | -006              | CMOS Control Signals erratum title changed to TTL-Level<br>Control Signals erratum. Erratum spec also changed from<br>requiring $V_{CC} \pm 0.2V$ to 4.0V (min), $V_{CC} + 0.2V$ (max) on control<br>pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 08/09/95                                                            | -007              | Table format identification criteria added to most items.         t <sub>PHWL</sub> /t <sub>PHEL</sub> Pushout Erratum: Improved for B-step.         CE# Delay from RP# High: Changed to apply to A-step only and not to B-step.         t <sub>PLPH</sub> Reset Pulse Width: Changed to reflect B-step improvements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 材料 886-3-57<br>子(上海) 86-21-54<br>子(深圳) 86-755-8<br>//www. 100y. con | 151736<br>3298787 | <ul> <li>Erroneous Erase Fail Flag Operation: Command reissue clarified.</li> <li>t<sub>PLQZ</sub> Specification: Changed to reflect B-step improvements.</li> <li>V<sub>PP</sub> Low Flag: Title changed from "False V<sub>PP</sub> Low Flag<br/>Operation" to "V<sub>PP</sub> Low Flag Operation." Separated into 2<br/>parts: False V<sub>PP</sub> Low Flag Operation and No V<sub>PP</sub> Flag<br/>Operation.</li> <li>TTL-Level Control Signals: Changed to reflect B-step fix.</li> <li>t<sub>WHEH</sub> /Address Timing: Changed to reflect B-step fix</li> <li>New erratum: t<sub>WHWL</sub>/ t<sub>EHEL</sub> for third Write Erratum added.</li> <li>New addenda: Input Slew Rate and Capacitance Specs added.</li> <li>New erratum: Extended Temp Cold Program added.</li> </ul> |

| EVISION HISTOR         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date of Revision       | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 08/22/95               | -008    | Identification criteria for A-Step sample, A-Step Prod, and B-step<br>changed to use top-side FPO mark for easier access and better<br>accuracy.<br>Max Erase Time Addendum added.<br>Low-Voltage Erase Time Erratum added.                                                                                                                                                                                                                                                                                                                                                      |

| 05/01/96               | -009    | This document has been converted to the new Specification Update format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WWW.1                  |         | Errata on extremely early -BR/CR sample material has been removed from this errata listing. This material was never put into production. The two errata removed were: "Limited V <sub>CC</sub> supply Voltage" and "Reduced V <sub>LKO</sub> (Commercial Temp)."                                                                                                                                                                                                                                                                                                                 |

| WWW                    |         | Access Time Erratum, which was previously removed in revision -005, has dropped from this revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                        |         | V <sub>CC</sub> Ramp Time (Datasheet Clarification) rewritten.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        |         | Automotive $V_{LKO}$ Spec Change removed, incorporated into datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 06/11/96               | -010    | New Erratum: BE/CE 5V Extended Temperature Limitation         C-step and D-step information added to:         tpHWL/tpHEL       Pushout (new spec values, status)         Third-Write Pulse (affected prod)         Ext Temp Programming Limitations (Status, affected products)         Low-Voltage Erase Time/Current Erratum (status, affected prod)         Spec Changes:         IoH/IoL Spec Change in 2.7V and 3.3V Ranges (new)         Documentation Changes:         Datasheet Erratum - WP# Description (new)         Max Byte/Word Program Time Specifications (new) |

| 7/26/96                | -011    | BE/CE 5V Extended Temperature Limitation erratum modified to include BV/CV products.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12/6/96                | -012    | E-step information added to:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CONTRACTION CONTRACTOR |         | Errata - t <sub>PHWL</sub> /t <sub>PHEL</sub> Pushout (new spec values)<br>Errata - Third-Write Pulse (affected prod)<br>Spec Changes - 001 thru 003<br>Spec Clarifications - 001                                                                                                                                                                                                                                                                                                                                                                                                |

| COM.1                  | ſ       | New Spec Change: t <sub>EHQZ</sub> and t <sub>GHQZ</sub> specs improved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2/3/97                 | -013    | Errata - t <sub>PHWL</sub> /t <sub>PHEL</sub> Pushout (new C & D-step spec values 2 μs to<br>8 μs)<br>New Spec Change : Removal of Max Byte/Word Write<br>Specification.                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **REVISION HISTORY.** Continued

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw WWW.100Y.COM.TW

WWW.100Y.

#### PREFACE

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This is the thirteenth release of the 28F400BV/CV/CE and 28F004BV/BE Specification Update. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain additional information that was not previously published. Functional descriptions for this product are found in the 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet.

#### Affected Documents/Related Documents

| Title                                                                                 | Order  |

|---------------------------------------------------------------------------------------|--------|

| 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family<br>Datasheet | 290530 |

#### Nomenclature

**Errata** are design defects or errors. These may cause the 28F400BV/CV/CE and 28F004BV/BEs' behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

Specification Changes are modifications to the current published specifications.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation.

**Documentation Changes** include typos, errors, or omissions from the current published specifications.

#### 28F004/400BV/BE/CV/CE SPECIFICATION UPDATE

#### NOTE:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

#### SUMMARY TABLES OF CHANGES

The following tables indicate the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the 4-*Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet*. Intel may fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or specification changes as noted. These tables use the following notations:

Codes Used in Summary Tables

Steps

胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

料 886-3-5753170

Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping.

This erratum is fixed in listed stepping or specification change does not apply to listed stepping.

#### Page location of item in this document.

Document change or update will be implemented.

This erratum is intended to be fixed in a future step of the component.

This erratum has been previously fixed.

There are no plans to fix this erratum.

Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

X:

(No mark) or (Blank box):

#### Page

(Page):

Status

Doc: Fix:

Fixed: NoFix:

Eval:

| Number | 100 | St  | eppir        | ngs | 11  | Page | Status | Errata                                                                                                                                            |

|--------|-----|-----|--------------|-----|-----|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| WWW    | Α   | В   | C            | D   | E   | N    |        | WW. CONTON                                                                                                                                        |

| 1      | Х   |     |              | DN  | - × | 9    | Fixed  | No prog/erase when $V_{CC} = 3V$ , $V_{PP} = 12V$ .                                                                                               |

| 2      | x   | X   | x            | X   | x   | 10   | NoFix  | t <sub>PHWL</sub> /t <sub>PHEL</sub> out of spec at 3V. B, C & D-step<br>fixed at 5V. E-Step pushes out to 25 μs and<br>2.7V added for all steps. |

| 3      | Х   |     | N            | .C. | 121 | 11   | Fixed  | Must wait 100 ns after reset before read.                                                                                                         |

| 4      | Х   | 1.1 |              | 7 6 | OV  | 12   | Fixed  | Erase status flag may erroneously indicate fail.                                                                                                  |

| 5      | Х   |     | 00           | 1.  |     | 13   | Fixed  | Erase resume fail may falsely indicate VPP-low.                                                                                                   |

| 6 <    | X   |     | 10           | N.  |     | 14   | Fixed  | A-step production has VPP-low flag disabled.                                                                                                      |

| 7      | Х   | N   |              |     | C   | 15   | Fixed  | TTL-levels require VIHMIN = 4.0V on control pins                                                                                                  |

| 8      | Х   |     | $\mathbf{N}$ | 90, |     | 16   | Fixed  | Write or address timing changes for A-step.                                                                                                       |

| 9      | Х   | Х   | Х            | X   | Х   | 20   | NoFix  | $t_{WHWL}\!/t_{EHEL}$ out of spec after 2-write sequence.                                                                                         |

| 10     | X   | x   |              | 10  | Vo  | 22   | Fixed  | Ext temp, $V_{CC} = 3.3V \pm 0.3V$ must program within T = 0°C - +85°C.                                                                           |

| 11     |     | x   |              | N.1 | 00  | 22   | Fixed  | Erase time and current may increase when $V_{CC} = 3.3V \pm 0.3V$ , $V_{PP} = 5V \pm 10\%$ .                                                      |

| 12     |     | V   | N            | Х   | 10  | 23   | Fixed  | Early D-step ext temp BE/CE/BV/CV material limited to $0^{\circ}C-85^{\circ}C$ when using $V_{CC} = 5V$ .                                         |

#### Specification Changes

| Number | Steppings |   |   |   |   | Page | Status | Specification Changes                                                 |

|--------|-----------|---|---|---|---|------|--------|-----------------------------------------------------------------------|

|        | Α         | в | С | D | E | .100 | J CC   | M WWW. LO.                                                            |

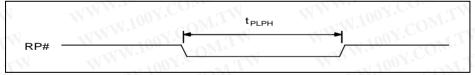

| 11.1   | Х         | Х | Х | Х | Х | 25   | Perm   | New tPLPH spec defined with values for A-, B-step                     |

| 2      | X         | Х | Х | Х | Х | 26   | Perm   | New tPLQZ spec defined with values for A-, B-step                     |

| 3      | Х         | Х | Х | X | Х | 27   | Perm   | I <sub>OH</sub> /I <sub>OL</sub> Spec Change in 2.7V and 3.3V Ranges. |

| 4      |           | Х | Х | Х | Х | 28   | Perm   | tEHQZ and tGHQZ specs improved.                                       |

## WWW.100

| A         B         C         D         E           1         X         X         X         X         29         Doc         Clarifies V <sub>CC</sub> ramp rate requirements. |                                               |      |    |   | ys | Steppin |   |   | Number |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|----|---|----|---------|---|---|--------|--|

| 1 X X X X X 29 Doc Clarifies V <sub>CC</sub> ramp rate requirements.                                                                                                           | X 29 Doc Clarifies Veg ramp rate requirements | N.10 |    | Е | D  | С       | в | A |        |  |

|                                                                                                                                                                                | X 23 Doc Clarines VCC ramp rate requirements. | Doc  | 29 | Х | Х  | Х       | Х | Х | 09.    |  |

| CONTRACTION WITH WITH WITH WITH WITH WITH WITH WITH                                                                                                                            | X 23 Doc Claimes V(Claimp rate requirements.  | Doc  | 29 | ~ | ^  | ^       | X |   | 1      |  |

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw WWW.100Y.COM.TW

V COM.TW

X.COM.TW

OY.COM.TW

#### **Documentation Changes**

WWW.100

WWW.10

| Number | Document Revision | Page | Status | Documentation Changes                                       |

|--------|-------------------|------|--------|-------------------------------------------------------------|

| 1      | -001              | 30   | Doc    | Input rise/fall times added to datasheet.                   |

| 2      | -001              | 30   | Doc    | Input/output capacitance specs added.                       |

| 3      | -001              | 31   | Doc    | Max block erase times added to datasheet.                   |

| 4      | -002/-003         | 31   | Doc    | Editing mistake in Revisions -002/-003 of datasheet.        |

| 5      | -003              | 32   | Doc    | Removal of Maximum Byte/Word Program time<br>specifications |

WWW.100Y.COM.TW WWW.100Y.COM.TW WWW.1007.COM.TW 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 WWW.100Y.COM.TW Http://www. 100y. com. tw WWW.100Y.COM.TW WWW.100 WWW.100Y.COM.T

#### 28F004/400BV/BE/CV/CE SPECIFICATION UPDATE

### int<sub>el</sub>.

### **IDENTIFICATION INFORMATION**

#### Markings

| Stepping                  | Identifier                                                                             | V.CUTTW            |

|---------------------------|----------------------------------------------------------------------------------------|--------------------|

| A-Step Engineering Sample | <ol> <li>"ES" on topside mark.</li> <li>No ninth digit on topside FPO mark.</li> </ol> | OX.COM.            |

| A-Step Production         | 1. Ninth digit of topside FPO mark = "A" or "F" or                                     | "C"                |

| B-Step Production         | 1. Ninth digit of topside FPO mark = "D" or "E"                                        | On y. COM'T,       |

| C-Step Production         | 1. Ninth digit of topside FPO mark = "G" or "Q"                                        | 勝特力材料 886-3-57     |

| D-Step Production         | 1. Ninth digit of topside FPO mark = "J" or "T"                                        | 胜特力电子(上海) 86-21-54 |

| E-Step Production         | 1. Ninth digit of topside FPO mark = "Y"                                               |                    |

| NOTE                      |                                                                                        | 胜特力电子(深圳) 86-755-8 |

#### NOTE:

C-Step and D-step production material reflect the same schematic revision level

#### ERRATA

#### 1. 3.3V V<sub>CC</sub>/12V V<sub>PP</sub> Program/Erase Limitation

**PROBLEM:** Affected material will not program and erase consistently using  $V_{CC} = 3.3 \pm 0.3V$  and  $V_{PP} = 12V \pm 5\%$ . This is limited to a few groups of early A-step material. All other voltage combinations are not affected. The affected modes are summarized in the table below.

| Vcc        | V <sub>PP</sub> | Read<br>Operation | Program<br>Operation | Erase<br>Operation |

|------------|-----------------|-------------------|----------------------|--------------------|

| 3.3 ± 0.3V | 5.0V ± 10%      | V                 | N.                   | CON.               |

| 5.0V ± 10% | 5.0V ± 10%      | $\checkmark$      | 100                  | V                  |

| 3.3 ± 0.3V | 12V ± 5%        | V                 | NO                   | NO                 |

| 5.0V ± 10% | 12V ± 5%        | V                 | V                    |                    |

NOTE:

$\sqrt{1}$  = mode functional.

**IMPLICATION:** Applications using  $V_{CC} = 3.3 \pm 0.3V$  and  $V_{PP} = 12V \pm 5\%$  will not be able to program or erase using these voltage ranges.

**WORKAROUND:** For affected material, if using 3.3V V<sub>CC</sub>, use V<sub>PP</sub> = 5V instead of V<sub>PP</sub> = 12V. In a PROM programmer (5V V<sub>CC</sub>), use 5V or 12V programming.

**STATUS:** This erratum has been fixed. Refer to Summary Table of Changes to determine the affected stepping.

AFFECTED PRODUCTS: Early A-step material using V<sub>CC</sub> =  $3.3 \pm 0.3$ V and V<sub>PP</sub> =  $12V \pm 5\%$  is affected.

| Thes                                                                     | e products | are affe | ected                                                                                                                                   | under ti   | hese operation  | ng conditions |

|--------------------------------------------------------------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|---------------|

| Name                                                                     | Package    | Step     | Marking                                                                                                                                 | Vcc        | V <sub>PP</sub> | Temp          |

| TE28F004BV-T/B,<br>TB28F400BV-T/B,<br>TE28F400CV-T/B,<br>TE28F400BV-T/B, | All        | A        | Third line of top mark<br>equals<br>T4410002C,<br>T4430001,<br>T4430002,<br>T4430003,<br>T4440003,<br>T4440004,<br>T444005Q,<br>T444020 | 3.3 ± 0.3V | 12V ± 5%        | All           |

#### 2. tPHWL/tPHEL Pushout

**PROBLEM:** Affected material does not meet its  $t_{PHWL}/t_{PHEL}$  specification for write operations in 2.7V, 3.3V and 5V V<sub>CC</sub> operations. This problem has been improved in the B, C and D-step versions of the product so that it meets specification at 5V, but the parameter does not meet its specification in 2.7V and 3.3V operations. The spec in 2.7V and 3.3V operations has been further pushed-out on the E-stepping. The erratum specifications are below:

| Specification                                             | $V_{CC} = 3.3 \pm 0.3V$<br>$V_{CC} = 2.7V - 3.6V$ | V <sub>CC</sub> = 5V ± 10% | Units |

|-----------------------------------------------------------|---------------------------------------------------|----------------------------|-------|

| t <sub>PHWL</sub> /t <sub>PHEL</sub> (Datasheet)          | 0.8                                               | 0.45                       | μs    |

| t <sub>PHWL</sub> /t <sub>PHEL</sub> (A-step Erratum)     | 8                                                 | 6                          | μs    |

| t <sub>PHWL</sub> /t <sub>PHEL</sub> (B-step Erratum)     | 8                                                 | meets spec                 | μs    |

| t <sub>PHWL</sub> /t <sub>PHEL</sub> (C-, D-step Erratum) | 8                                                 | meets spec                 | μs    |

| t <sub>PHWL</sub> /t <sub>PHEL</sub> (E-step Erratum)     | 25                                                | meets spec                 | μs    |

The specification  $t_{PHWL}$  (RP# High Recovery to WE# Going Low) is the minimum time between the RP# signal going high to WE# going low. The specification  $t_{PHEL}$  (RP# High Recovery to CE# Going Low) is the minimum time between the RP# signal going high to CE# going low.

**IMPLICATION:** The erratum affects the delay from coming out of a reset until a command write can be executed on the part (affects both WE#-controlled and CE#-controlled command sequences). Although the read specification  $t_{PHQV}$  (RP# going high to data valid) Is less than the  $t_{PHWL}/t_{PHEL}$  errata, the full time for  $t_{PHWL}/t_{PHEL}$  must be completed prior to WE# going low.

WORKAROUND: Verify system timings to ensure this does not impact your design.

**STATUS:** This erratum has been improved from the A-step to the B-, C- and D-steps. The errata has been pushed-out further on the E-stepping. It now meets specification when operating at 5V, but does not meet specification for 2.7V and 3V operations. No fix or further improvement is planned. Refer to Summary Table of Changes to determine the affected steppings.

**AFFECTED PRODUCTS:** This erratum applies to all A-, B-, C-, D- and E-step material with some improvements depending on the stepping.

| Thes                                                                                                                                                                                  | These products are affected |                       |                                                                                                                                  |                 |                 | under these operating conditions |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|----------------------------------|--|--|

| Name                                                                                                                                                                                  | Package                     | Step                  | Marking                                                                                                                          | V <sub>cc</sub> | V <sub>PP</sub> | Temp                             |  |  |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV/BE,<br>TB28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BR-T/B,<br>AB28F400BR-T/B | All                         | A<br>B<br>C<br>D<br>E | No ninth digit on<br>topside FPO mark<br>or<br>Ninth digit of topside<br>FPO mark = one of:<br>A, F, C, D, E, G, Q,<br>J, T or Y | All             | All             | All                              |  |  |

#### 3. CE# Delay from RP# High

**PROBLEM:** Affected material requires a delay between coming out of reset (RP# signal going high) and beginning a read operation (CE# going low). This minimum specification must be followed to ensure valid data is read during subsequent read operations.

| Specification      | $V_{\rm CC} = 3.3 \pm 0.3 V$ | $V_{CC} = 5V \pm 10\%$ | Units  |

|--------------------|------------------------------|------------------------|--------|

| t <sub>PHEL2</sub> | 100                          | 100                    | ns     |

| WT                 | WWW.100Y.CO.II               | W WT                   | 100%   |

|                    |                              | HEL2                   |        |

| CE#                | N. M. LON                    |                        |        |

|                    |                              |                        |        |

| RP#                | WW I 100Y.C                  |                        | VI 100 |

#### Timing Diagram for Required Delay

**IMPLICATION:** Applications that do not meet the required delay may read invalid data from the device.

**WORKAROUND:** This timing must be followed for A-step material, but not for B-step material. Verify system timings to ensure this does not impact your design.

**STATUS:** This erratum has been fixed. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** All A-step engineering samples and production materials are affected. B-step has been fixed.

| Thes                                                                                                                                              | under t | nese operatin | g conditions                                                                                             |     |                 |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|

| Name                                                                                                                                              | Package | Step          | Marking                                                                                                  | Vcc | V <sub>PP</sub> | Temp |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BV-T/B, |         |               | No ninth digit on<br>topside FPO mark<br>or<br>ninth digit of topside<br>FPO mark = "A" or<br>"F" or "C" |     | All             | All  |

#### 4. Erroneous Erase Fail Flag Operation

**PROBLEM:** Due to a logic timing problem, affected units may indicate a block erase error in the Status Register when, in fact, proper block erasure has occurred. The relevant bit of the Status Register is SR.5 (Erase Status), which is shaded on the diagram below. Normally, SR.5 = 1 indicates an error in block erasure, and SR.5 = 0 indicates successful block erase. If SR.5 = 0 following an erase operation, the erase operation was completed successfully. If SR.5 = 1 following an erase operation, the bit was most likely set incorrectly due to the logic timing problem.

| WSMS | ESS | ES | DWS  | VPPS | R | R | R   |

|------|-----|----|------|------|---|---|-----|

| 7    | 6   | 5  | 1004 | 3    | 2 | 1 | 000 |

#### NOTE:

Please see Section 3.3.2 of the 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet for more information on Status Register operation.

**IMPLICATION:** Applications using the Status Register to verify successful erase will have erase failures that will affect operation.

**WORKAROUND:** The erase status flag (SR.5) should be ignored by masking this bit in your software. To confirm a successful block erase, read back the contents of a block to verify that all bytes contain FFH (all bits in block equal 1). Alternatively, reissue the Block Erase command until a successful erase is reported in the Status Register. Because of these limitations, block cycling for affected material should be limited to 10,000 cycles for both commercial and extended temperature ranges. Reissuing the Erase command upon an error bit counts as another block erase cycle.

**STATUS:** This erratum has been fixed. Refer to Summary Table of Changes to determine the affected stepping.

特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100v. com. tw

**AFFECTED PRODUCTS:** All A-step engineering samples and production materials are affected. B-step has been fixed.

| These                                                                                                                                                               | under these operating conditions |      |                                                                                                          |     |                 |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|

| Name                                                                                                                                                                | Package                          | Step | Marking                                                                                                  | Vcc | V <sub>PP</sub> | Temp |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BR-T/B | All                              |      | No ninth digit on<br>topside FPO mark<br>or<br>Ninth digit of topside<br>FPO mark = "A" or<br>"F" or "C" | All |                 | All  |

#### 5. False V<sub>PP</sub>-Low Flag Operation When Returning from Erase Suspend

**PROBLEM:** Only applications using erase suspend mode are affected. If using erase suspend mode, the following problem may be encountered: When resuming erase from erase suspend mode, the device may abort the erase procedure as a result of a logic timing problem. When this happens, the Status Register will indicate an erase failure (SR.5 = 1) and the V<sub>PP</sub> status bit will indicate that V<sub>PP</sub> voltage was not within specification (SR.3 = 1), even if V<sub>PP</sub> is within tolerances.

The relevant bit of the Status Register is SR.3 (V<sub>PP</sub> Status), which is shaded on the diagram below. Normally, SR.3 = 1 indicates an aborted operation due to V<sub>PP</sub> not being switched on.

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

#### NOTE:

Please see Section 3.3.2 of the 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet for more information on Status Register operation.

**IMPLICATION:** Applications using the erase suspend features may intermittently experience failures resuming erase from suspend mode. Data in the block being erased when suspend mode was entered will be corrupted by the partial erasure. Data in other blocks is not affected.

**WORKAROUND:** If a system design is experiencing program/erase failures under the conditions described above, issue another Erase command to complete a successful block erase.

**STATUS:** This erratum has been fixed. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** All A-step ES materials using erase suspend mode are affected. B-step has been fixed.

| Thes                                                                                                                                              | These products are affected |                        |                                                                      |     |                 | under these operating conditions |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------|----------------------------------------------------------------------|-----|-----------------|----------------------------------|--|--|

| Name                                                                                                                                              | Package                     | Step                   | Marking                                                              | Vcc | V <sub>PP</sub> | Temp                             |  |  |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400CV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TB28F400BV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BV-T/B, | All                         | A<br>0M<br>CON<br>1.CO | "ES" on topside mark<br>and<br>No ninth digit on<br>topside FPO mark | All | All             |                                  |  |  |

#### 6. Disabled V<sub>PP</sub>-Low Flag

**PROBLEM:** The VPPS flag in the Status Register (SR.3) has been disabled in affected products. Normally, when the VPPS flag is operational, a program or erase command initiated with V<sub>PP</sub> not in range (V<sub>PPH1</sub> or V<sub>PPH2</sub>) will result in the erase status bit (ES = SR.5) or program status bit (DWS = SR.4) being set to "1" along with the V<sub>PP</sub> status bit (VPPS = SR.3) to indicate a failed operation due to low V<sub>PP</sub>. However, under this erratum, if a program or erase command is initiated with V<sub>PP</sub> not in range (V<sub>PPH1</sub> or V<sub>PPH2</sub>), then the erase status bit (ES = SR.5) or program status bit (DWS = SR.4) will be set to "1" to indicate program or erase failure, but the V<sub>PP</sub> status bit (VPPS = SR.3) will remain at "0," since the VPPS flag has been disabled.

Basically, the part will operate normally, but will not indicate when low  $V_{PP}$  is the cause of a failed program or erase operation.

The relevant bit of the Status Register is SR.3 (V<sub>PP</sub> Status), which is shaded on the diagram below. Normally, SR.3 = 1 indicates an aborted operation due to V<sub>PP</sub> not being switched on.

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

NOTE:

Please see Section 3.3.2 of the 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet for more information on Status Register operation.

**IMPLICATION:** When an erase or program failure is experienced, the device will not indicate if low V<sub>PP</sub> was the cause of the failure.

**WORKAROUND:** If a system design is experiencing program/erase failures under the conditions described above, issue another Erase command to complete a successful block erase. System design using the VPPS flag to detect program or erase errors should use the program and erase status bits instead.

**STATUS:** This erratum has been fixed in the B-step. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** This erratum applies to all A-step production material. B-step has been fixed.

| Thes                                                                                                                                                                | These products are affected |                 |                                                           |     |                 | under these operating conditions |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-----------------------------------------------------------|-----|-----------------|----------------------------------|--|--|

| Name                                                                                                                                                                | Package                     | Step            | Marking                                                   | Vcc | V <sub>PP</sub> | Temp                             |  |  |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BR-T/B | All                         | A<br>001<br>100 | Ninth digit of topside<br>FPO mark = "A" or<br>"F" or "C" | All | All             |                                  |  |  |

#### 7. TTL-Level Control Signals

**PROBLEM:** This erratum applies only to systems using TTL signal levels and  $V_{CC} = 5V \pm 10\%$ . If you are using CMOS inputs, this erratum does not affect your design. Due to an internal detector problem, TTL logic high level must be minimum 4.0V (instead of 2.4V) on the control pins of the device: CE#, OE#, and WE#. Standard TTL levels can continue to be used on other pins on the device. The required logic-high level is defined in the table below:

| Parameter                | Min | Max                    | Units |

|--------------------------|-----|------------------------|-------|

| Input High Voltage (TTL) | 4.0 | V <sub>CC</sub> + 0.2V | V     |

**IMPLICATION:** Applications using TTL levels will need to modify their designs to meet the higher input voltage requirements on the control signals.

WORKAROUND: This requirement must be met for proper operation of the device.

**STATUS:** This erratum has been fixed in B-step material. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** All A-step engineering samples and production material using TTL signal levels and operating at  $V_{CC} = 5V \pm 10\%$  are affected. B-step material has been fixed.

| These products are affected                                                                                                                                        |         |      |                                                                                                          | under these operating conditions |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------------------------------------------------------------------------------------------------------|----------------------------------|-----|------|

| Name                                                                                                                                                               | Package | Step | Marking                                                                                                  | Vcc                              | VPP | Temp |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TE28F400BV-T/B,<br>TE28400EV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BR-T/B |         |      | No ninth digit on<br>topside FPO mark<br>or<br>Ninth digit of topside<br>FPO mark = "A" or<br>"F" or "C" | 5V ± 10%<br>(TTL<br>Levels)      |     | All  |

#### 8. Write Timing Erratum/Address Timing Erratum

**PROBLEM:** Due to logic timing problems, modifications in write or address timing are required. Two possible workarounds exist: errata A and B. Refer to the following table to determine the operating which applies to your operation conditions. Where the table says, "One of A or B," one of either erratum A **or** B is necessary for proper functionality. Where it says, "A," only erratum A is needed. "Not Affected" means that this erratum does not effect that operation condition.

| M.L                      | x8-Mode                    | Operation                  | x16-Mode Operation         |                            |  |

|--------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|

| WT                       | V <sub>PP</sub> = 5V ± 10% | V <sub>PP</sub> = 12V ± 5% | V <sub>PP</sub> = 5V ± 10% | V <sub>PP</sub> = 12V ± 5% |  |

| $V_{CC} = 3.3 \pm 0.3 V$ | One of A or B              | A                          | Not Affected               | A                          |  |

| $V_{CC} = 5V \pm 10\%$   | One of A or B              | One of A or B              | Not Affected               | Not Affected               |  |

**IMPLICATION:** Applications operating in an affected mode must implement the applicable workaround for proper operation.

#### WORKAROUND:

#### A. tWHEH- CE# Timing Erratum

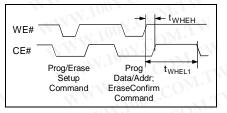

Due to a logic timing problem, new timing restrictions may be necessary between the WE# and CE# signals during write operations. The timing waveforms and specifications are shown below:

Timing Waveform for CE#-Controlled Writes

#### Affected Parameters for WE#-Controlled Writes

|                    | N. 100 COM.                        | Datasheet  |            | Err | CONT  |       |

|--------------------|------------------------------------|------------|------------|-----|-------|-------|

| Symbol             | Parameter                          | Min        | Max        | Min | Max   | Units |

| t <sub>WHEH</sub>  | CE# Hold Time from WE# High        | 0          | no<br>spec | 0   | 5     | ns    |

| t <sub>WHEL1</sub> | CE# Pulse Width High from WE# High | no<br>spec | no<br>spec | 110 | W.100 | ns    |

#### NOTE:

Erratum timing for  $t_{\text{WHEL1}}$ , given above, is required only after the second WE# pulse in a WE# controlled write sequence.

Basically, these new errata specifications for WE#-controlled writes require the system timing to:

- 1. Take CE# to logic high no earlier than WE# goes high and no later than 5 ns after WE# goes high.

- 2. Hold CE# high for at least 110 ns, starting from the time WE# goes high.

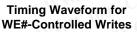

#### Affected Parameters for CE#-Controlled Writes

|                    | OM.L                                                                | Data | sheet      | En  | NW. |       |

|--------------------|---------------------------------------------------------------------|------|------------|-----|-----|-------|

| Symbol             | Parameter                                                           | Min  | Max        | Min | Max | Units |

| t <sub>EHEL1</sub> | CE# Pulse Width High from WE# or CE#<br>High, whichever occurs last | 20   | no<br>spec | 110 |     | ns    |

NOTE:

The erratum timing for t<sub>EHEL1</sub>, given above, is required only after the second CE# pulse in a CE# controlled write sequence.

#### 28F004/400BV/BE/CV/CE SPECIFICATION UPDATE

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

A system can also use the alternative CE#-controlled writes with the specifications given in the datasheet with the addition of  $t_{\text{EHEL1}}$ , which must have a pulse width of 110 ns, as shown above.

These timing specifications must be met for proper operation of the device. The flash memory chip select must go inactive within 5 ns of a program/erase operation and remain inactive for a period of 110 ns before going active again. Consider the following options for meeting the  $t_{WHEL1}$  or  $t_{EHEL1}$  requirement:

- 1. Follow a program/erase two-write sequence with an access to another memory so as not to decode the flash memory chip select for the required period of time.

- Insert one or more no-op commands following a program/erase two-write sequence, again to ensure the flash memory chip select is disabled for the required period of time.

Depending on your system implementation, the  $t_{WHEH}$  requirement may require additional logic to ensure the required  $t_{WHEH}$  timing. Evaluate your system timing to ensure the new write requirements can be met. This erratum has been fixed in B-step material.

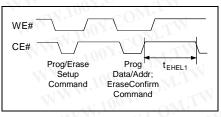

#### B. Address Timing Erratum

Due to a logic timing problem, new timing restrictions may be necessary on the lowest order address pin. This pin is the  $A_{-1}$  address pin for 28F400 products in x8-mode and the  $A_{10}$  address pin for 28F004 x8-only products. The timing waveforms and specifications follow:

| Product | Affected Pin                 |

|---------|------------------------------|

| 28F400  | A <sub>-1</sub> (in x8 mode) |

| 28F004  | A <sub>10</sub>              |

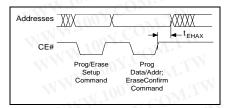

### Timing Waveform for WE#-Controlled Writes

#### Timing Waveform for CE#-Controlled Writes

| Affected Parameters for WE#-Controlled Writes |                                                                                         |      |       |         |      |    |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------|------|-------|---------|------|----|--|--|

|                                               | WWW.200V.COm                                                                            | Data | sheet | Erra    | Unit |    |  |  |

| Symbol                                        | Parameter                                                                               | Min  | Max   | Min Max |      |    |  |  |

| t <sub>WHAX</sub>                             | Address Hold Time from WE# High (unaffected pins)                                       | 10   |       | N10     | 7.   | ns |  |  |

|                                               | Address Hold Time from WE# High<br>(affected pin: A_1 for 28F400 in x8, A10 for 28F004) | 10   | MM    | 40      | 0V.  | ns |  |  |

#### Affected Parameters for CE#-Controlled Writes

| TI                | WWW 100Y.COM.TW                                                                                |     | Datasheet |     | Erratum |      |

|-------------------|------------------------------------------------------------------------------------------------|-----|-----------|-----|---------|------|

| Symbol            | Parameter                                                                                      | Min | Max       | Min | Max     | Unit |

| t <sub>EHAX</sub> | Address Hold Time from CE# High (unaffected pins)                                              | 10  |           |     | W.10    | ns   |

|                   | Address Hold Time from CE# High (affected pin: $A_{-1}$ for 28F400 in x8, $A_{10}$ for 28F004) | 10  |           | 40  | W.      | ns   |

This new erratum specification requires the system timing in x8-mode to hold the affected address pin valid for 40 ns from the time WE# goes high (for WE#-controlled writes) or from the time CE# goes high (for CE#-controlled writes).

These timing specifications must be met for proper operation of the device. Additional logic may be needed to meet these requirements.

**STATUS:** This erratum has been fixed in B-step material. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** All A-step material is affected depending on operating mode (see table below). B-step material has been fixed.

| Thes                                                                                                                                                                | e products | under these operating conditions |                                                                                                          |     |                 |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|

| Name                                                                                                                                                                | Package    | Step                             | Marking                                                                                                  | Vcc | V <sub>PP</sub> | Temp |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400EV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B,<br>AB28F400BR-T/B | All        |                                  | No ninth digit on<br>topside FPO mark<br>or<br>Ninth digit of topside<br>FPO mark = "A" or<br>"F" or "C" | All |                 | All  |

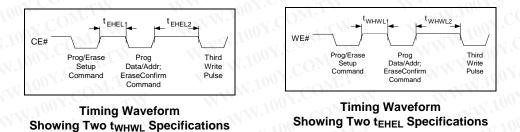

#### 9. Third Write-Pulse twhwL/teheL Specification Erratum

**PROBLEM:** This erratum affects designs issuing program or erase commands to the flash device with  $V_{CC} = 2.7V-3.6V$  or  $3.3 \pm 0.3V$ . Operation with  $V_{CC} = 5V \pm 10\%$  is not affected. Program and erase functions are initiated using a two-write sequence, with the Program or Erase Setup command being written to the part, then the data program or erase confirm being written on the next cycle after a time  $t_{WHWL1}$  ( $t_{EHEL1}$  for CE#-controlled writes) between the write low pulses. Following the second write in a two-write sequence; the WE# (CE#) signal must stay high for 35 ns before going low again for a third write pulse, shown as the  $t_{WHWL2}$  ( $t_{EHEL2}$ ) on the right in the below. The value of  $t_{WHWL1}$  ( $t_{EHEL1}$ ) between the first and second write in the sequence remains at its datasheet specification. The specified and erratum values are shown in the table which follows.

|                                            | Product | BV                      | -60    | BV-80 | /BV–120 |    |  |

|--------------------------------------------|---------|-------------------------|--------|-------|---------|----|--|

|                                            | Vcc     | 2.7V-3.6V or 3.3 ± 0.3V |        |       |         | -  |  |

| Parameter                                  | Load    | 50 pF                   |        |       | Units   |    |  |

|                                            | COM     | Spec                    | Errata | Spec  | Errata  |    |  |

| t <sub>WHWL2</sub> (min, third write only) |         | 20                      | 40     | 30    | 40      | ns |  |

| tEHEL2 (min, third write on                | ly)     | 20                      | 40     | 30    | 40      | ns |  |

**IMPLICATION:** Violating the errata conditions described in this erratum can cause the Write State Machine to abort the program or erase operation in progress and report a successfully completed operation in the Status Register, although in reality, the operation has not completed successfully.

**WORKAROUND:** Note, however, that even without this erratum, it is not useful for the system to write to the flash device after a program sequence until the Status Register reports that the program operation has completed, since the State Machine is designed to ignore all instructions while a program operation is in progress. Writing the Status Register Read command to the device is not necessary since the device defaults to outputting Status Register data while the program operation is in progress. In the case of an erase operation, the only valid command that should be written to the device while an erase operation is in progress is the Erase Suspend command. In this situation, the system must wait for the erratum value of  $t_{WHWL2}$  ( $t_{EHEL2}$ ) before requesting an Erase Suspend.

**STATUS:** This is a permanent change. Refer to Summary Table of Changes to determine the affected steppings.

**AFFECTED PRODUCTS:** All A-, B-, C- and D-step materials are affected when using  $V_{CC} = 3.3 \pm 0.3V$  or 2.7V-3.6V.

| Thes                                                                                                                                          | under these operating conditions |                       |                                                                                                                                  |                               |                 |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|------|

| Name                                                                                                                                          | Package                          | Step                  | Marking                                                                                                                          | Vcc                           | V <sub>PP</sub> | Temp |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400BV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV/BE,<br>TB28F400BV-T/B,<br>TE28400CV/CE,<br>TE28F400BV-T/B |                                  | A<br>B<br>C<br>D<br>E | No ninth digit on<br>topside FPO mark<br>or<br>ninth digit of topside<br>FPO mark = one of:<br>A, F, C, D, E, G, Q,<br>J, T or Y | 2.7V-3.6V<br>or<br>3.3 ± 0.3V | All             | All  |

#### 10. Extended Temperature Programming Limitations

**PROBLEM:** Affected material has the following limitations on operating parameters:

| Parameter                                 | Min | Max | Unit |

|-------------------------------------------|-----|-----|------|

| Extended Temperature Range (Program only) | 0   | +85 | °C   |

Because on-chip program circuitry is sensitive to very low temp operation, this material must be programmed within the temperature range of  $0^{\circ}$ C to +85°C. Read and erase operation is unaffected over the full extended temperature operating range (-40°C to +85°C).

**IMPLICATION:** This erratum limits the temperature range over which affected material can be programmed.

WORKAROUND: Contact your Intel representative for workaround information.

**STATUS:** This errata has been fixed on the C- and D-steppings. Refer to Summary Table of Changes to determine the affected stepping.

**AFFECTED PRODUCTS:** All A- and B-step materials are affected when using  $V_{CC} = 3.3 \pm 0.3V$  and programming over T =  $-40^{\circ}$ C to  $0^{\circ}$ C. Products using commercial temperature, or not programming over this temperature range are not affected.

| Thes                                                                   | under these operating conditions |        |                                                                                                                 |                 |                 |              |

|------------------------------------------------------------------------|----------------------------------|--------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|

| Name                                                                   | Package                          | Step   | Marking                                                                                                         | V <sub>cc</sub> | V <sub>PP</sub> | Temp         |

| TE28F004BV-T/B,<br>TB28F400BV-T/B,<br>TE28400CV-T/B,<br>TE28F400BV-T/B | All                              | A<br>B | No ninth digit on<br>topside FPO mark<br>or<br>Ninth digit of topside<br>FPO mark = one of:<br>A, F, C, D, or E | 3.3 ± 0.3V      | All             | -40°C to 0°C |

#### 11. Low-Voltage Erase Time/Current Erratum

**PROBLEM:** Block erase times for affected material may intermittently exceed erase time and I<sub>PPE</sub> current specifications when operating with  $V_{CC} = 3.3 \pm 0.3V$  and  $V_{PP} = 5V \pm 10\%$  over specified cycling limits. Typical erase times are not affected. The increased erase time and I<sub>PPE</sub> erase current only occur together and do not occur independently of each other. The errata erase times and currents are indicated between the thickened lines, in the tables which follow.

| Parameter                                 | DS Spec | Errata | Unit |

|-------------------------------------------|---------|--------|------|

| Maximum Block Erase Time (Boot/Parameter) | 7       | 20     | s    |

| Maximum Block Erase Time (Main)           | 14      | 20     | s    |

#### Errata Erase Times (V<sub>CC</sub> = $3.3 \pm 0.3V$ , V<sub>PP</sub> = $5V \pm 10\%$

#### Errata IPPE Specification (V<sub>CC</sub> = 3.3 $\pm$ 0.3V, V<sub>PP</sub> = 5V $\pm$ 10%

| Parameter                                 | DS Spec | Errata | Unit |

|-------------------------------------------|---------|--------|------|

| IPPE (max, during errata occurrence only) | 30      | 40     | mA   |

**IMPLICATION:** Applications operating under the affected conditions may intermittently see longer than normal erase times, accompanied by increased erase current.

WORKAROUND: Ensure that system operation is not affected by errata parameters.

**STATUS:** This errata has been fixed on later B-step (ninth digit = "E") and C-/D-step parts. Refer to Summary Table of Changes to determine the affected stepping.

AFFECTED PRODUCTS: Early B-, C-, and D-step material is affected when erasing at  $V_{CC} = 3.3 \pm 0.3V$  and  $V_{PP} = 5V \pm 10\%$ .

| Thes                                                                                                                           | e products       | under ti                   | hese operatin                                                                                                       | g conditions                            |          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------|--|--|

| Name                                                                                                                           | Name Package Ste |                            | Marking                                                                                                             | Marking V <sub>CC</sub> V <sub>PP</sub> |          |  |  |

| E28F004BV-T/B,<br>PA28F400BV-T/B,<br>E28F400CV-T/B,<br>E28F400BV-T/B,<br>TE28F004BV-T/B,<br>TE28F400BV-T/B,<br>TE28F400BV-T/B, | All              | Early<br>B or<br>C or<br>D | Ninth digit of topside<br>FPO mark = "D" or<br>"G" or "J" is affected.<br>"E," "Q," and "T"<br>materials are fixed. | 3.3 ± 0.3V                              | 5V ± 10% |  |  |

#### NOTE:

Designs not using B-step material or the 3V  $V_{CC}$  / 5V  $V_{PP}$  voltage combination are not affected. All B-step units of the listed products that meet the application and marking criteria are affected. A-step is not affected.

#### 12. BE/CE/BV/CV 5V Vcc Extended Temperature Limitation

#### PROBLEM

The operating temperature for affected material is limited to  $0^{\circ}C - +85^{\circ}C$  when using  $V_{CC} = 5V \pm 10\%$ . This is detailed in the table below.

| Parameter                                                             | Min | Max | Unit |

|-----------------------------------------------------------------------|-----|-----|------|

| Extended Temperature Range ( $V_{CC} = 5V \pm 10\%$ or $5V \pm 5\%$ ) | 0   | +85 | °C   |

When using 5V V<sub>CC</sub>, the chip must be operated within the temperature range of 0°C to +85°C. Low voltage operation ( $3.3\pm0.3$ V or 2.7-3.6V) is unaffected and can be used over the full extended temperature operating range (-40°C to +85°C). Note that if the flash pin CE# is permanently tied low (enabled), then this erratum does not apply.

#### IMPLICATION

This erratum limits the temperature range over which affected material can be used at 5V  $V_{\text{CC}}.$

#### WORKAROUND

Ensure the erratum temperature requirements are not violated when using 5V  $V_{CC}$ . Contact your Intel representative for additional workaround options.

#### STATUS

This erratum has been modified to include -BV/CV suffix products as well as the -BE/CE products originally covered. This erratum has been fixed in new production material. However, shipments of affected products may contain fixed and unfixed material through October 1996. Fixed material can be identified a "T" in the ninth digit of the topside FPO mark. Refer to Summary Table of Changes to determine the affected stepping.

#### AFFECTED PRODUCTS

Only initial limited production D-Step -BE/CE/BV/CV material (identified by a "J" in the ninth digit of the topside FPO mark) is affected by this erratum when operating at 5V V<sub>CC</sub>. All A-, B-, C-, and later D-step materials (ninth digit = "T") are **unaffected**. Applications not using 5V V<sub>CC</sub> or sub  $-0^{\circ}$ C temperatures are not affected.