勝特力材料 886-3-5753170

胜特力电子(上海) 86-21-34970699

胜特力电子(深圳) 86-755-83298787

[Http://www.100y.com.tw](http://www.100y.com.tw)

To our customers,

---

## Old Company Name in Catalogs and Other Documents

---

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <http://www.renesas.com>

April 1<sup>st</sup>, 2010

Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<http://www.renesas.com>)

Send any inquiries to <http://www.renesas.com/inquiry>.

## Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

To all our customers

---

**Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.**

---

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

## Description

## Description

The M16C/62T group of single-chip microcomputers are built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and are packaged in a 100-pin or a 80-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. They also feature a built-in multiplier and DMAC, making them ideal for controlling office, communications, industrial equipment, and other high-speed processing applications.

The M16C/62T group includes a wide range of products with different internal memory types and sizes and various package types.

## Features

- Memory capacity ..... M30623M4T-XXXGP : ROM 32K bytes, RAM 3K bytes

M30622M8T/M8V-XXXFP, M30623M8T/M8V-XXXGP : ROM 64K bytes, RAM 4K bytes

M30622MCT/MCV-XXXFP, M30623MCT/MCV-XXXGP : ROM 128K bytes, RAM 5K bytes

M30622ECT/ECV-XXXFP, M30623ECT/ECV-XXXGP : PROM 128K bytes, RAM 5K bytes

- Shortest instruction execution time ..... 62.5ns (f(XIN)=16MHz, Vcc=5V)

- Supply voltage ..... Mask ROM version : 4.2 to 5.5V (f(XIN)=16MHz, without software wait)

One-time PROM version : 4.5 to 5.5V (f(XIN)=16MHz, without software wait)

- Low power consumption ..... 140mW (Vcc = 5V, f(XIN)=16MHz)

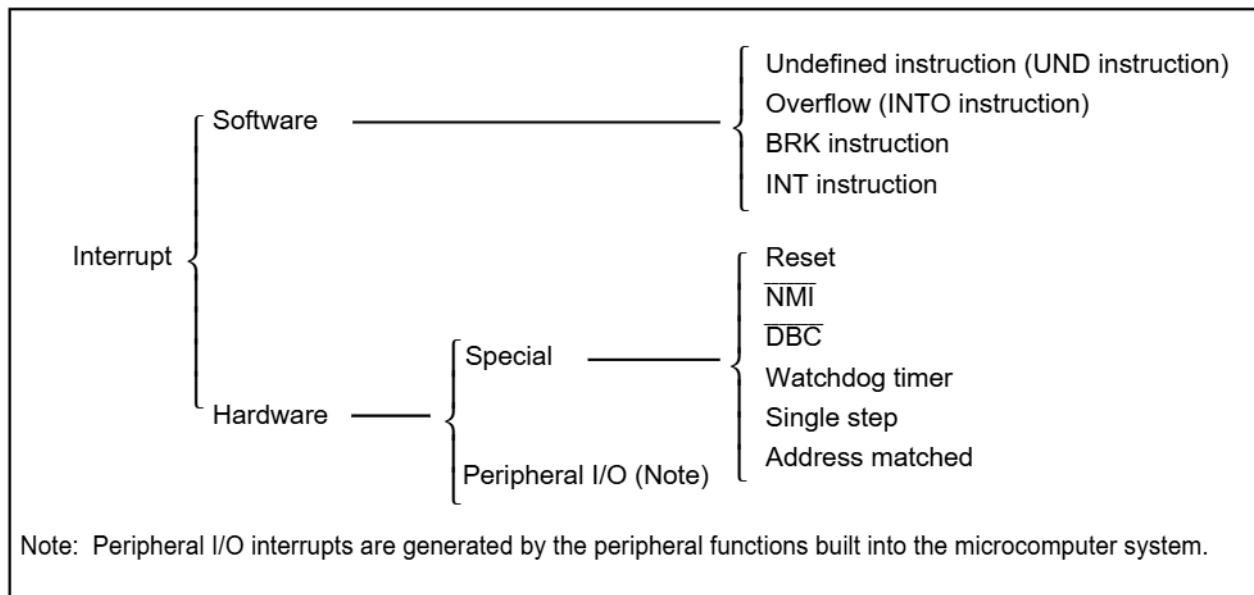

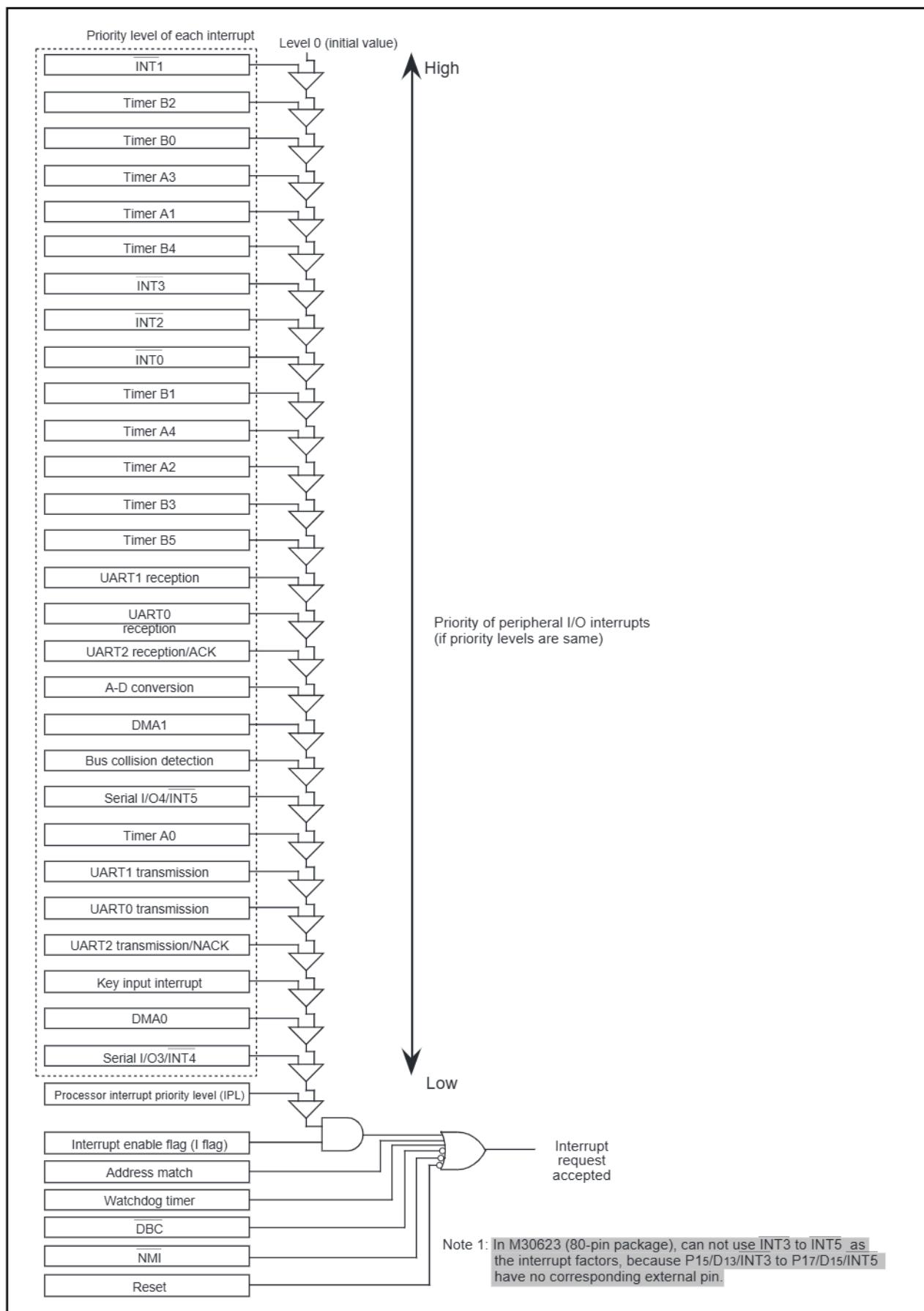

- Interrupts ..... 25 internal interrupt sources, 8 external interrupt sources (M30622(100-pin package))

/5 sources (M30623(80-pin package)), 4 software interrupt sources, 7 levels (including key input interrupt)

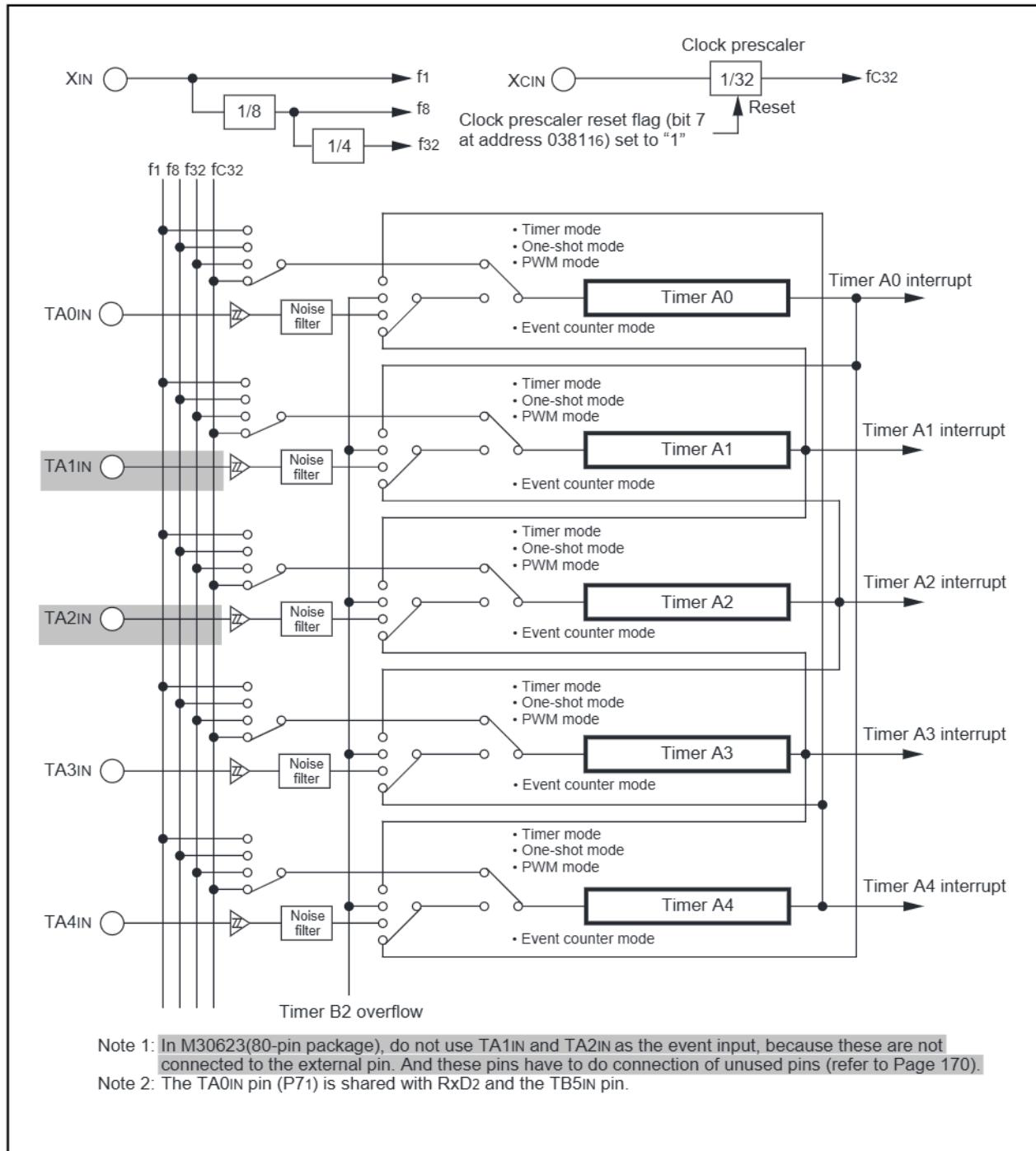

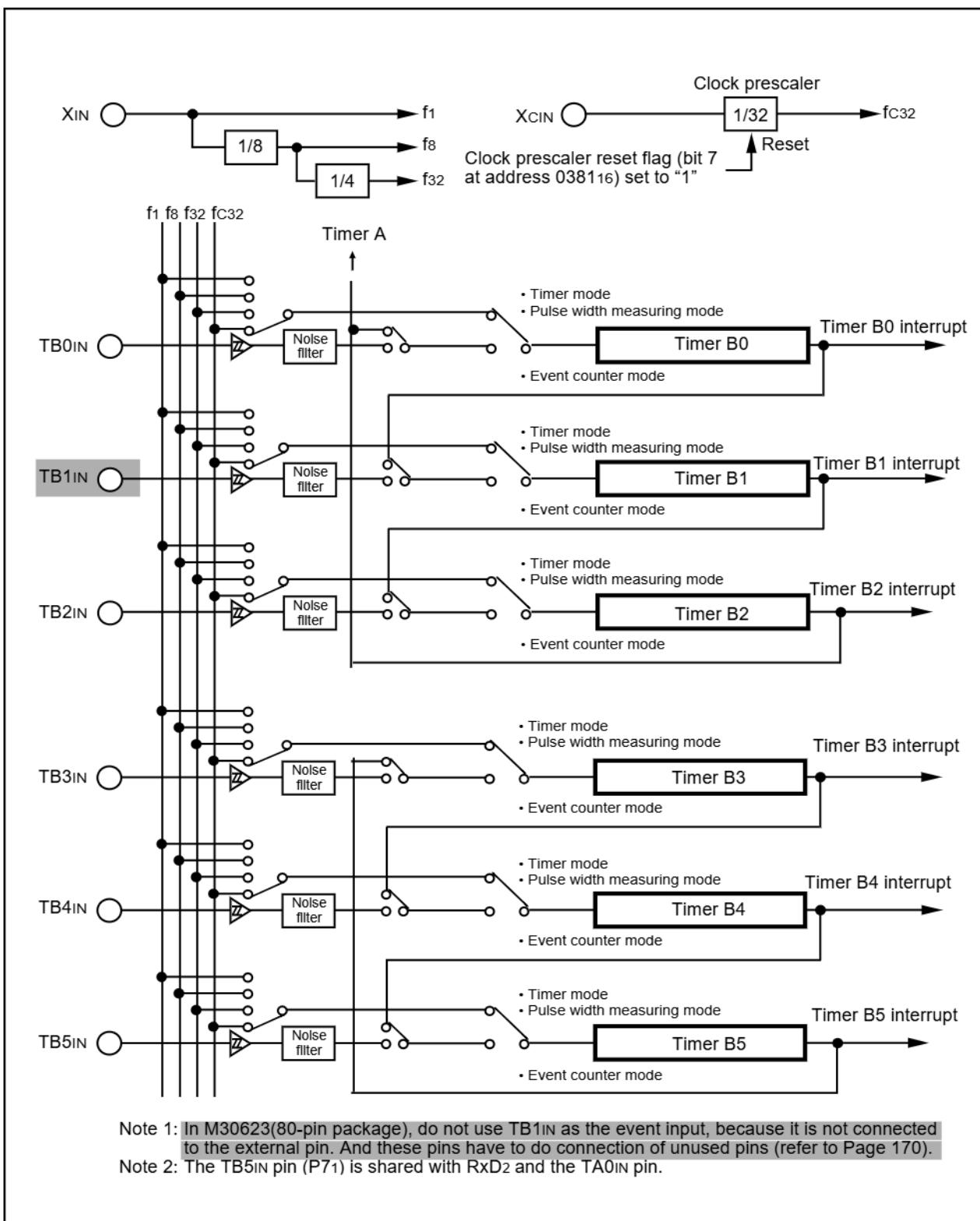

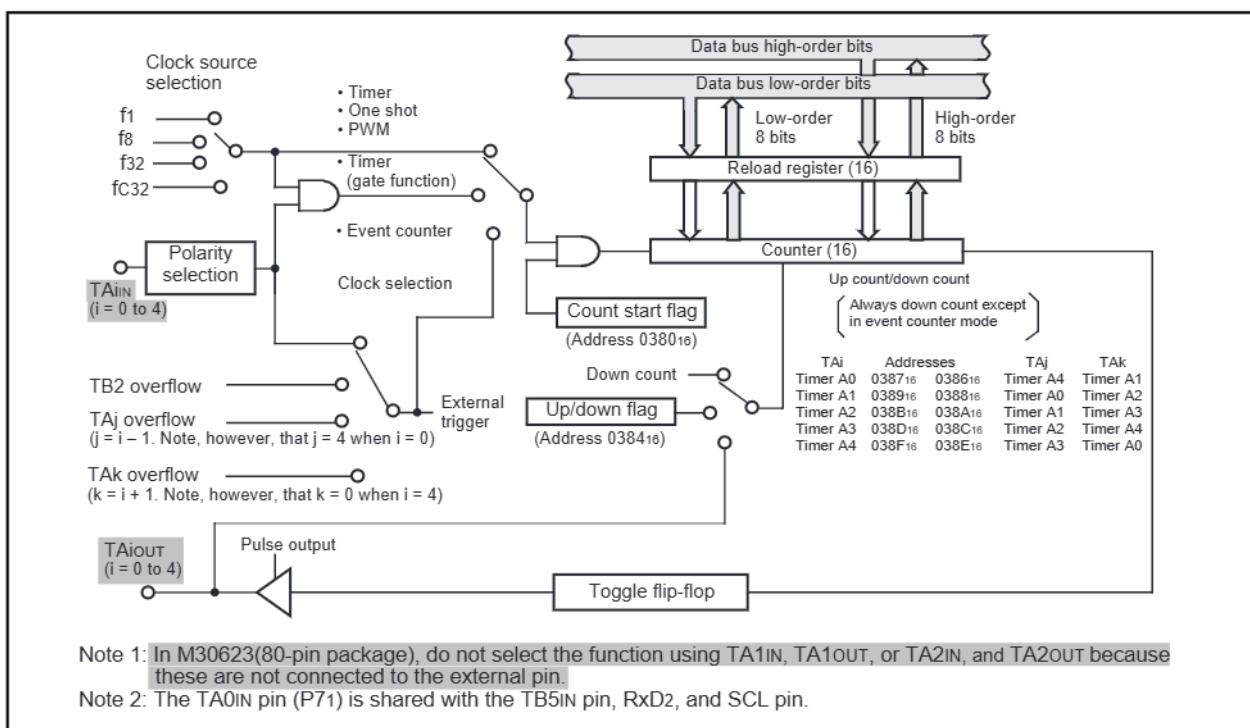

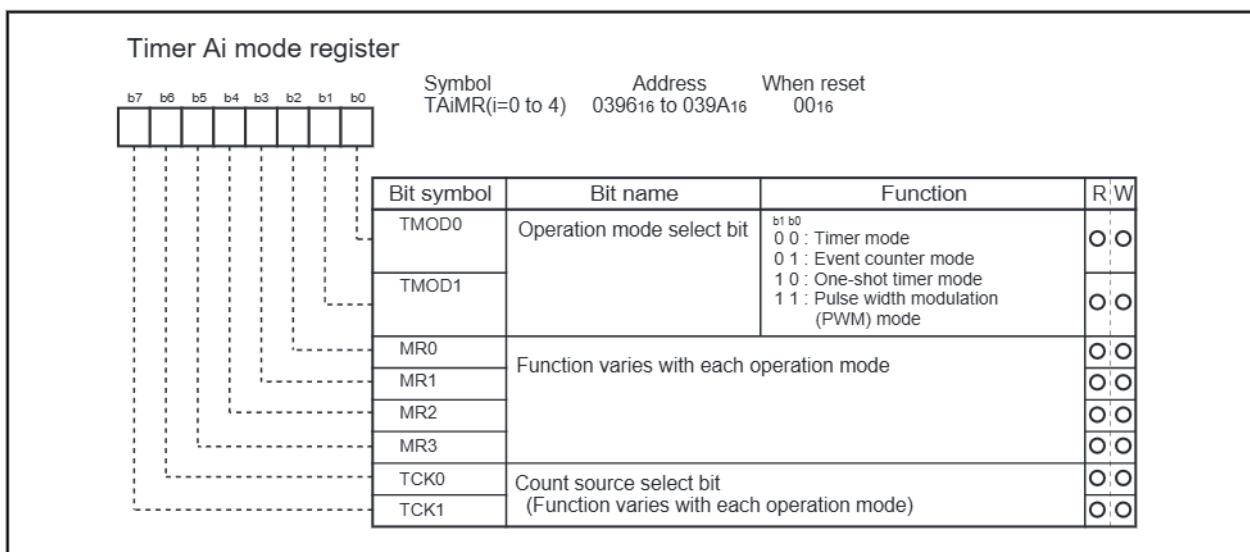

- Multifunction 16-bit timer ..... 5 I/O timers + 6 input timers(M30622(100-pin package))

3 I/O timers + 5 input timers(M30623(80-pin package))

- Inside 16-bit timer ..... 3 timers(only M30623(80-pin package))(Note 1)

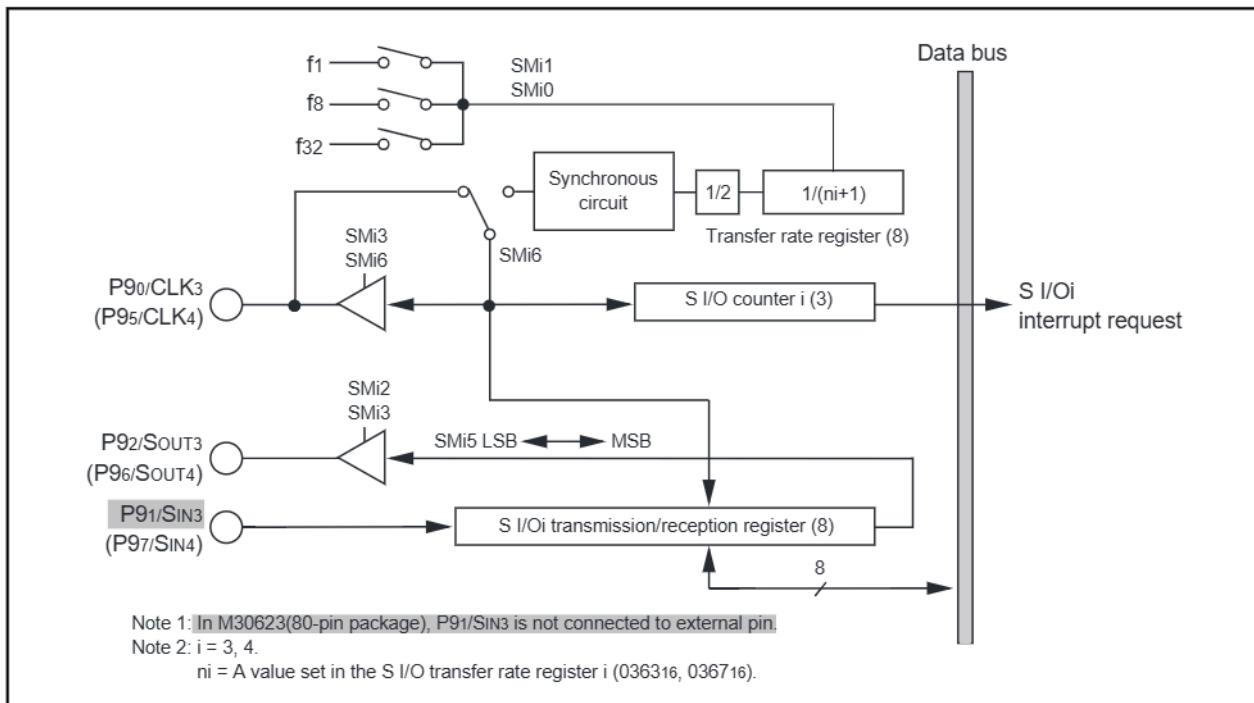

- Serial I/O ..... • M30622(100-pin package) : 3 for UART or clock synchronous + 2 for synchronous

• M30623(80-pin package) : 3 for UART or clock synchronous(one of exclusive UART)

+ 2 for synchronous(one of exclusive transmission)

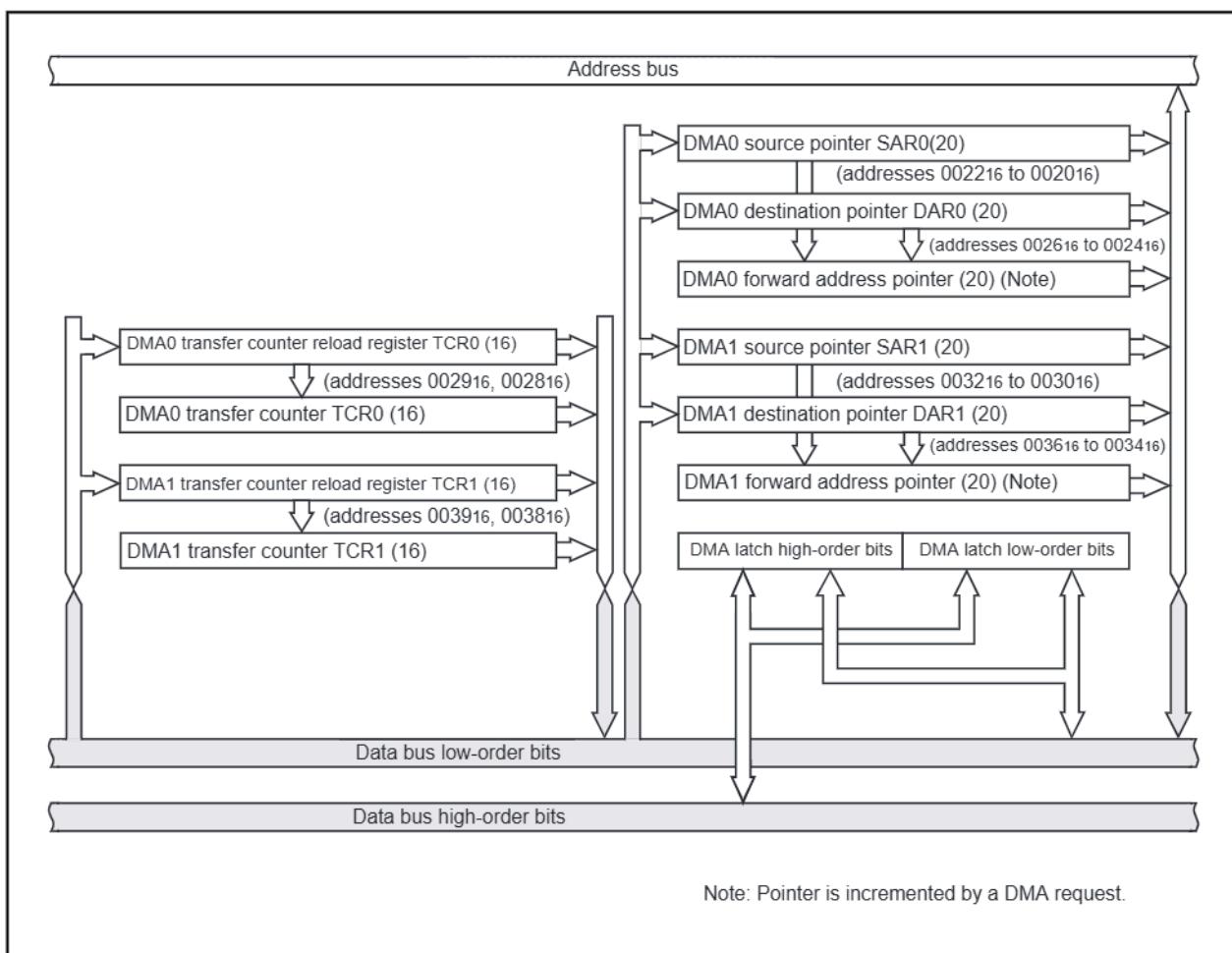

- DMAC ..... 2 channels (trigger: 24 sources)

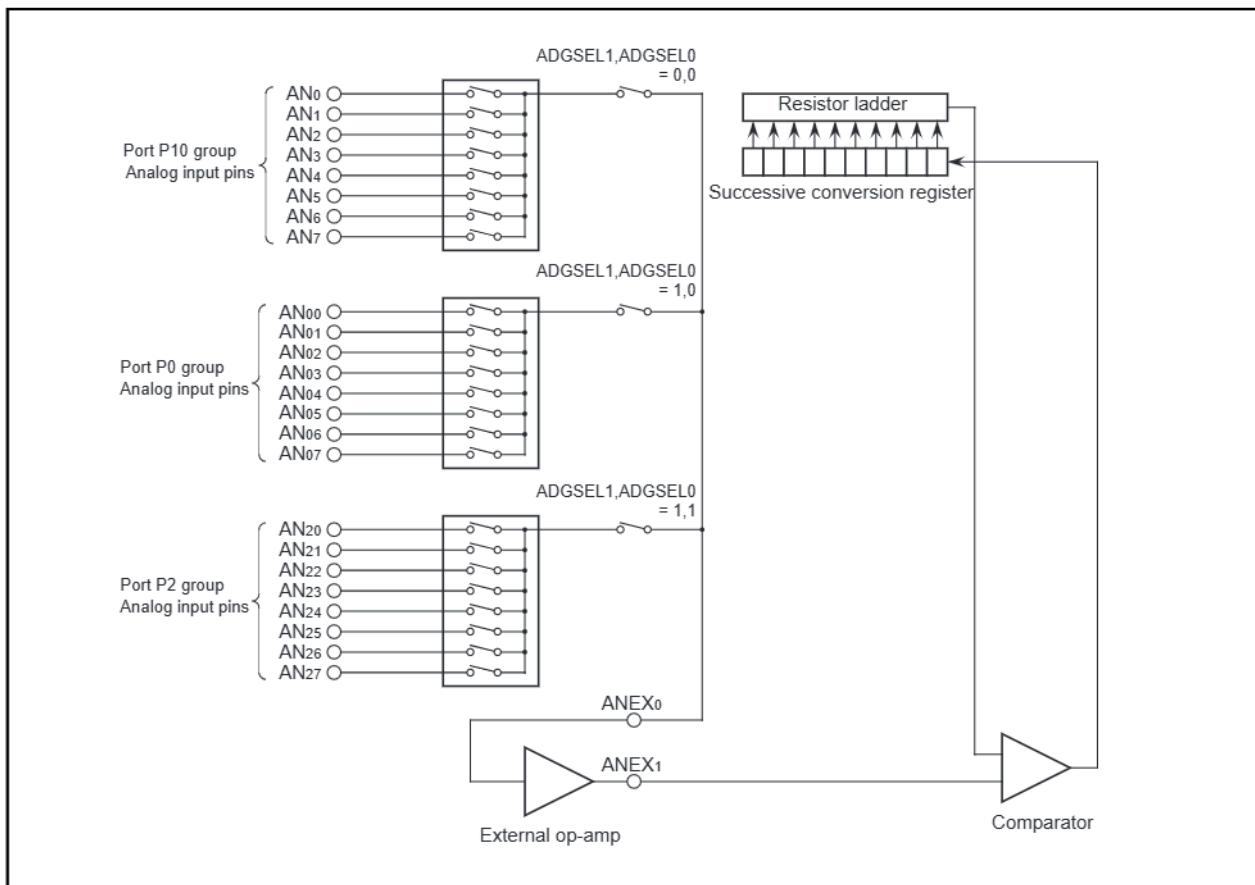

- A-D converter ..... 10 bits X 8 channels (Expandable up to 26 channels)

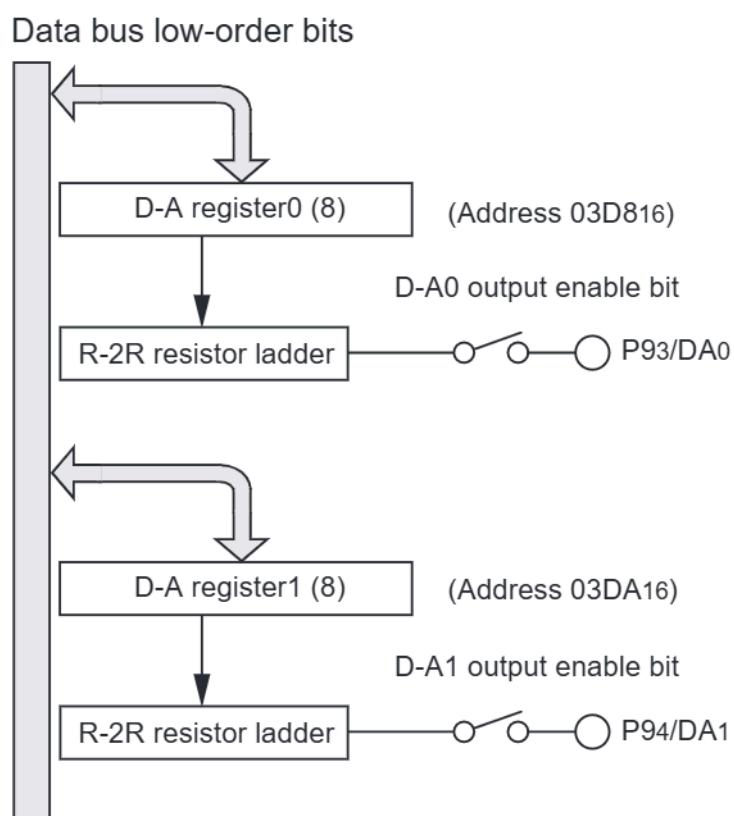

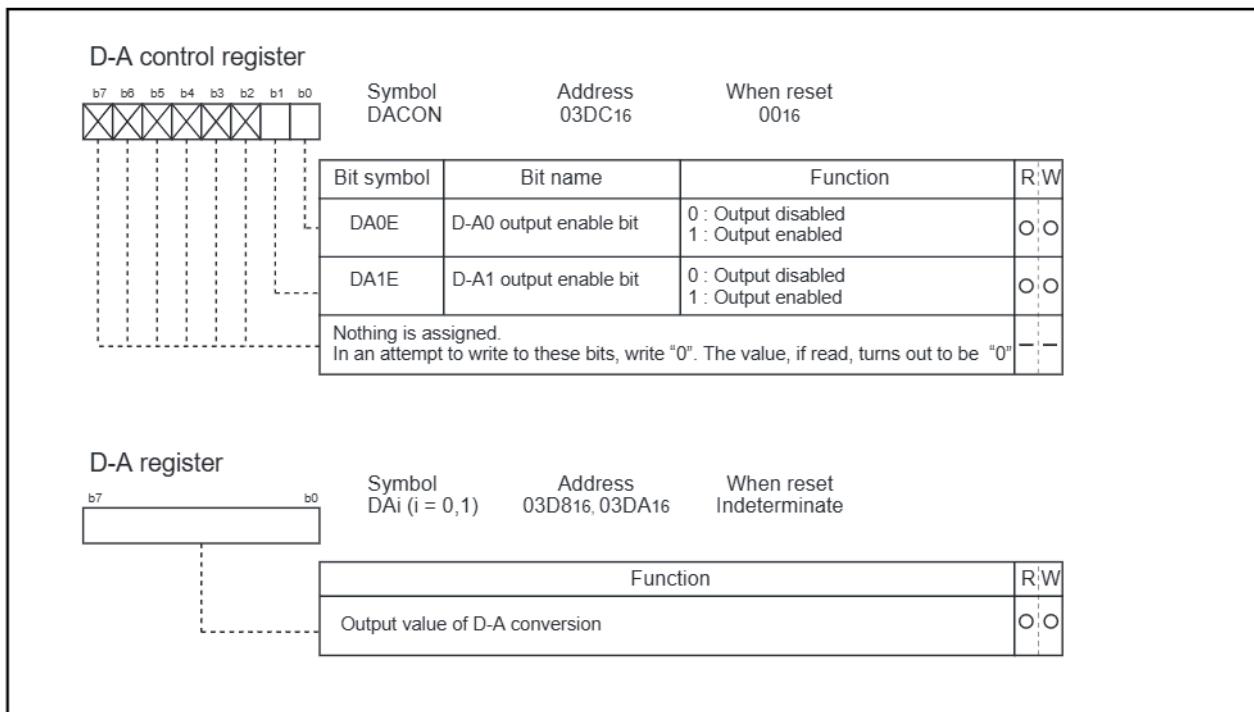

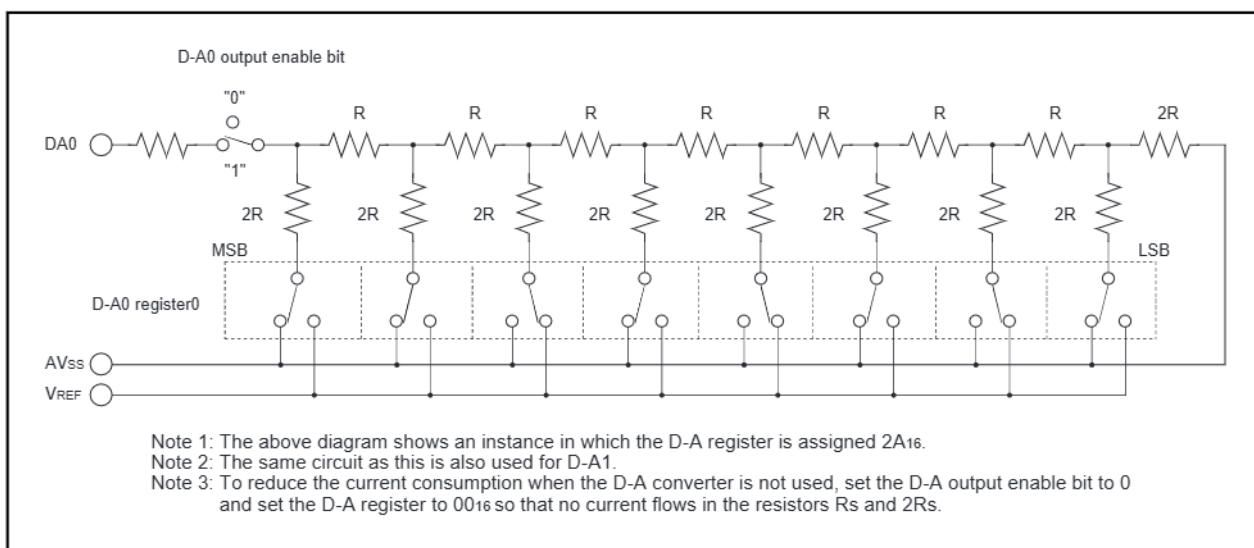

- D-A converter ..... 8 bits X 2 channels

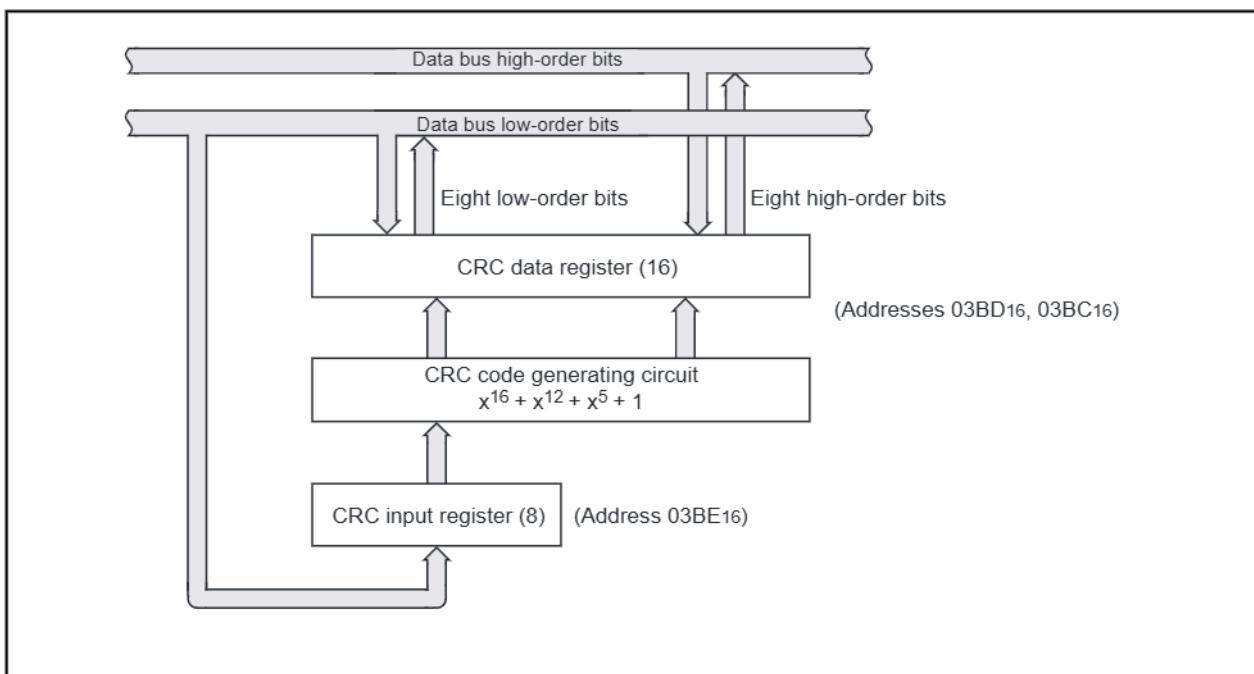

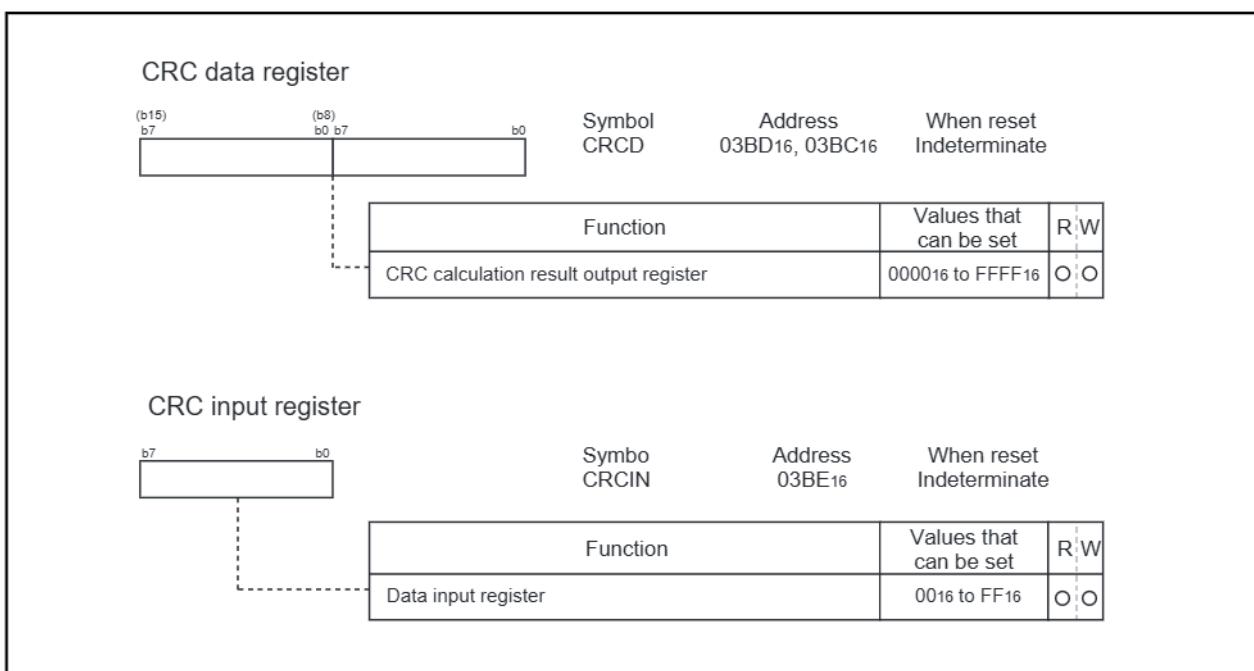

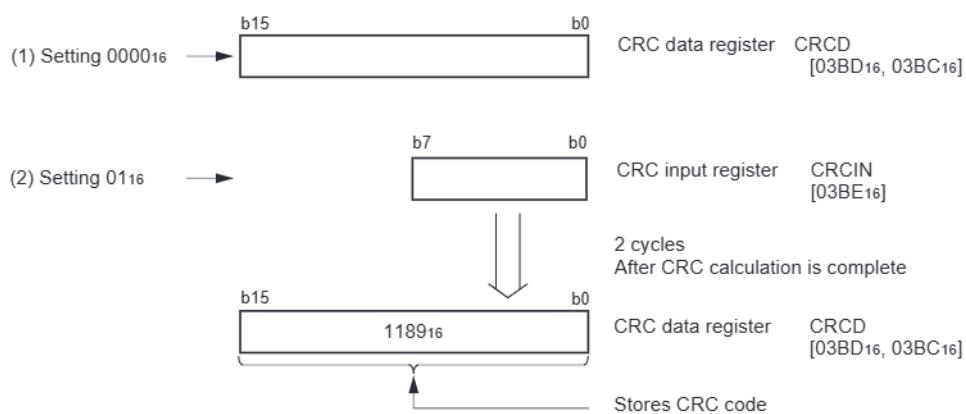

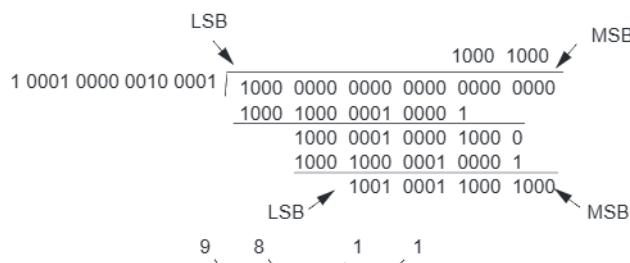

- CRC calculation circuit ..... 1 circuit

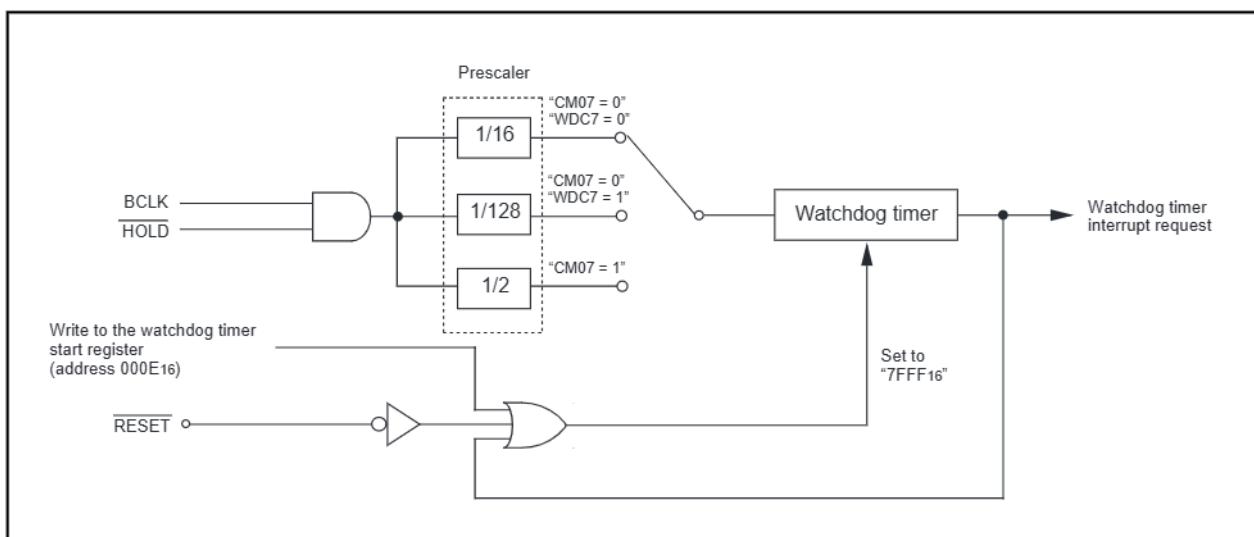

- Watchdog timer ..... 1 line

- Programmable I/O ..... 87 lines(M30622(100-pin package)), 70 lines(M30623(80-pin package))

- Input port ..... 1 line (P85 shared with NMI pin)

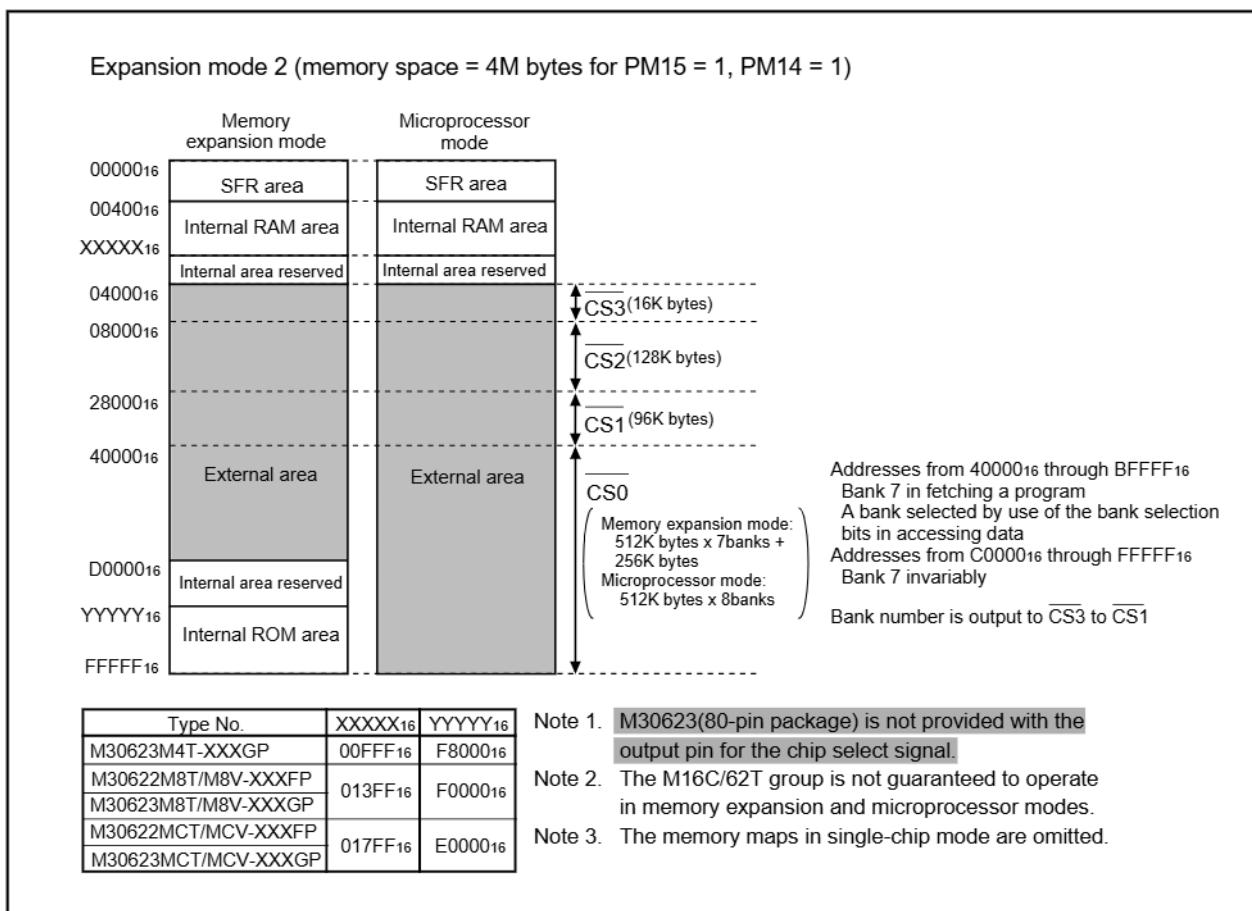

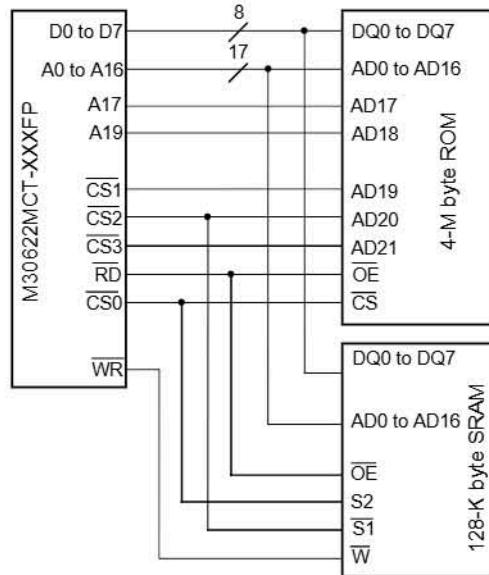

- Memory expansion ..... Available (to 1.2M bytes or 4M bytes)

- Chip select output ..... 4 lines(only M30622(100-pin package))(Note 2)

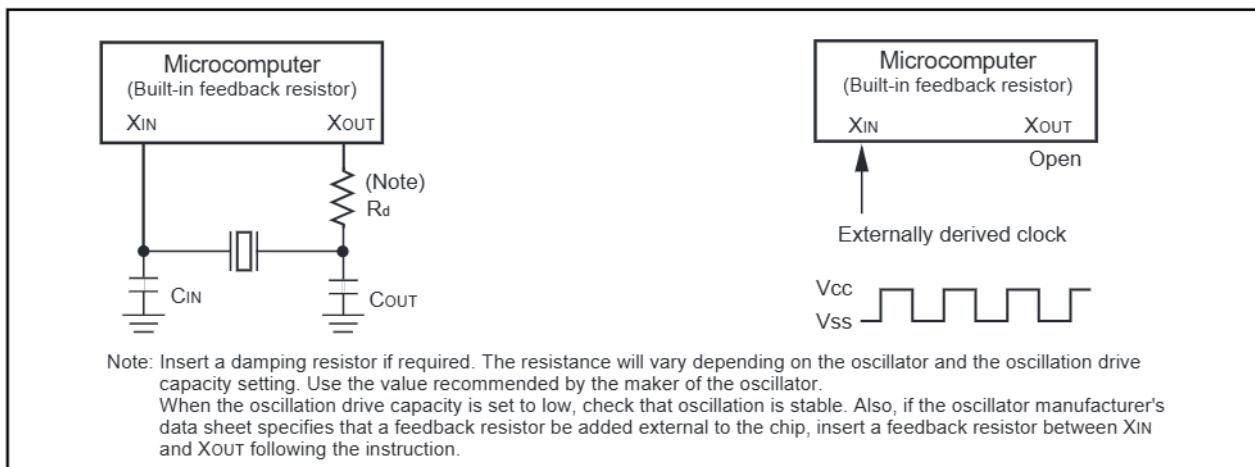

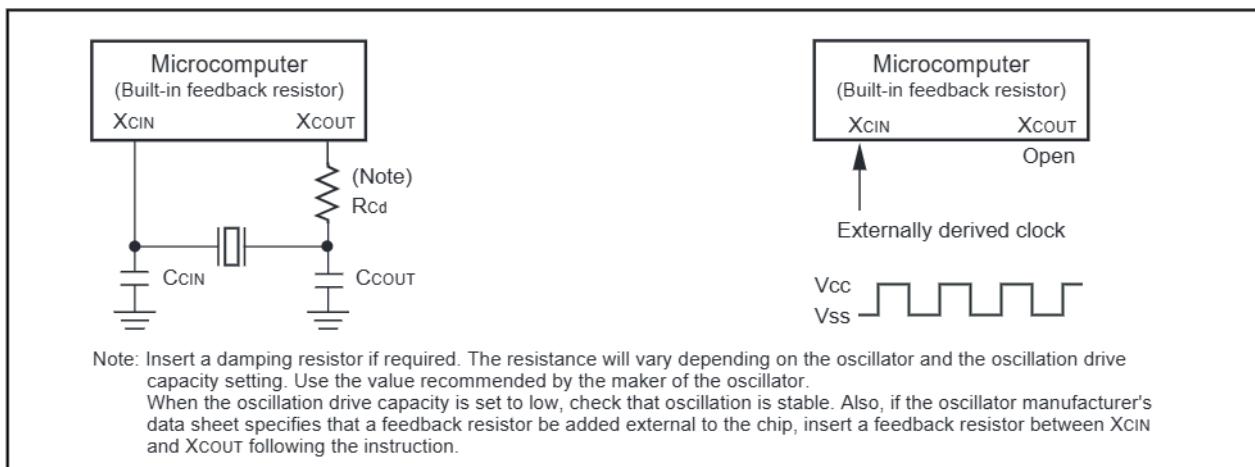

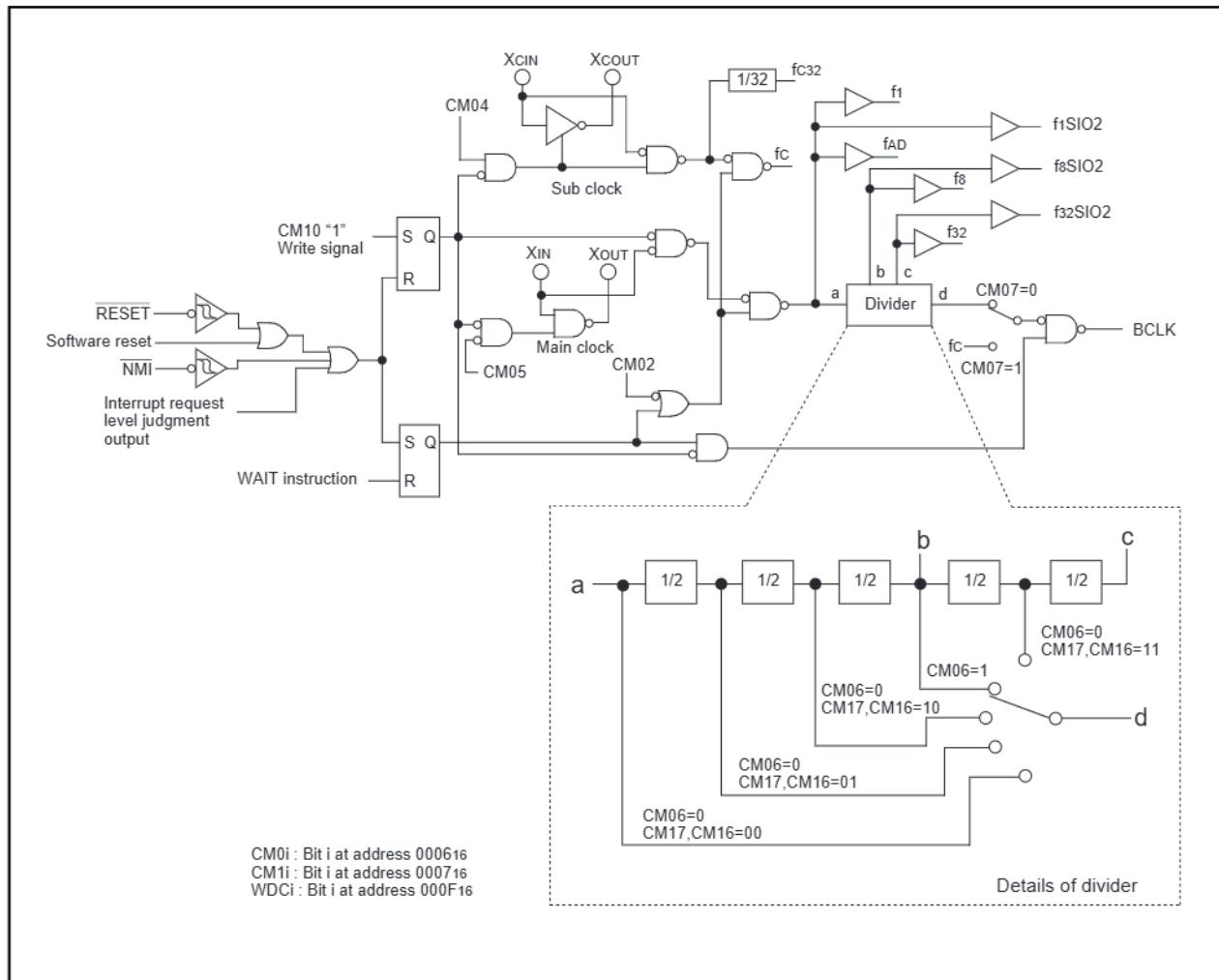

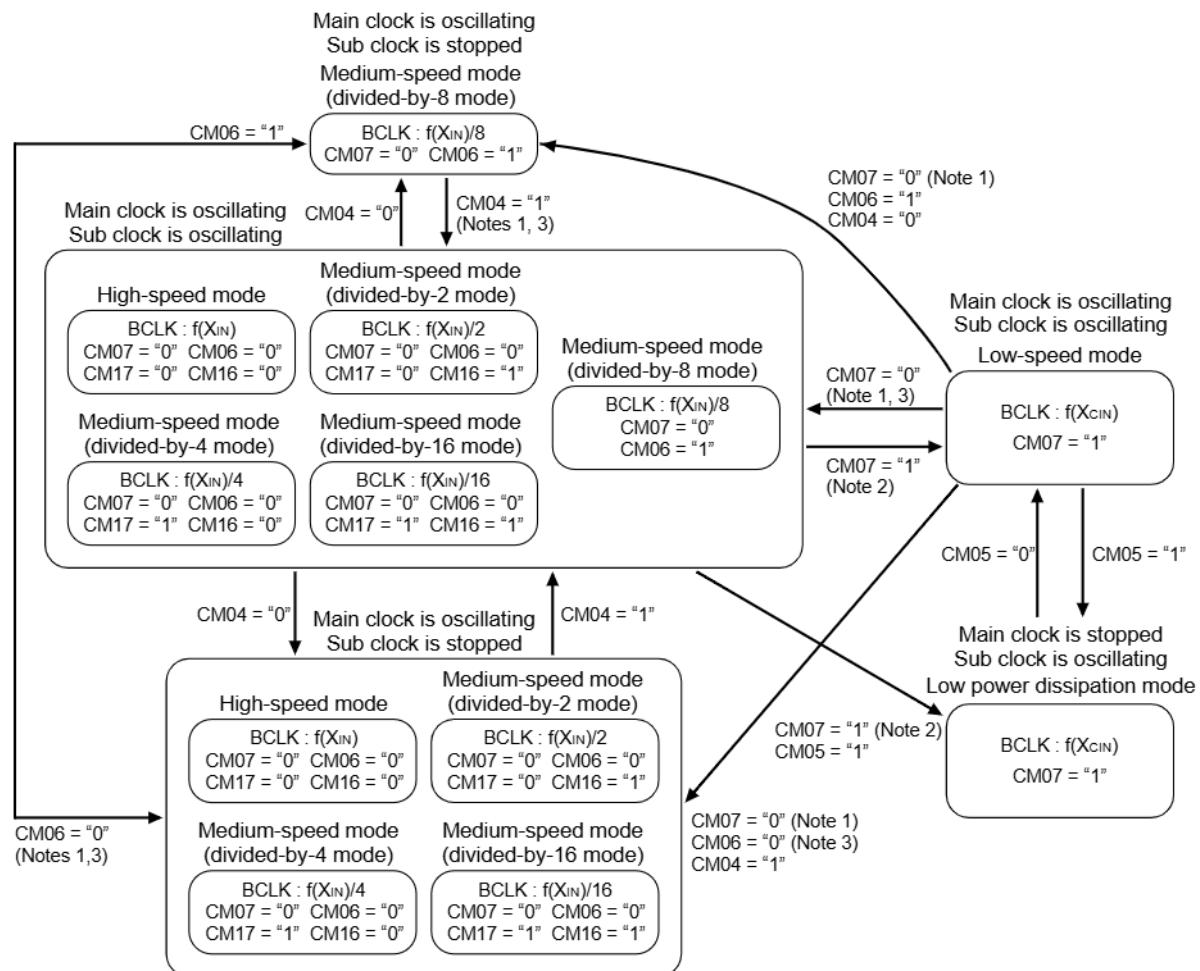

- Clock generating circuit ..... 2 built-in clock generation circuits (built-in feedback resistor, and external ceramic or quartz oscillator)

Note 1: In M30623(80-pin package), these timers have no corresponding external pin can be used as internal timers.

Note 2: M30623(80-pin package) has no external pin for chip select output.

## Applications

Audio, cameras, office equipment, communications equipment, portable equipment, cars, etc

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error.

Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

## -----Table of Contents-----

|                                     |    |                                                      |     |

|-------------------------------------|----|------------------------------------------------------|-----|

| Central Processing Unit (CPU) ..... | 12 | Timer .....                                          | 82  |

| Reset .....                         | 15 | Timers' function for three-phase motor control ..... | 100 |

| Processor Mode .....                | 28 | Serial I/O .....                                     | 112 |

| Clock Generating Circuit .....      | 40 | A-D Converter .....                                  | 148 |

| Protection .....                    | 49 | D-A Converter .....                                  | 159 |

| Interrupts .....                    | 50 | CRC Calculation Circuit .....                        | 161 |

| Watchdog Timer .....                | 70 | Programmable I/O Ports .....                         | 163 |

| DMAC .....                          | 72 | Electrical characteristics .....                     | 178 |

## Pin Configuration

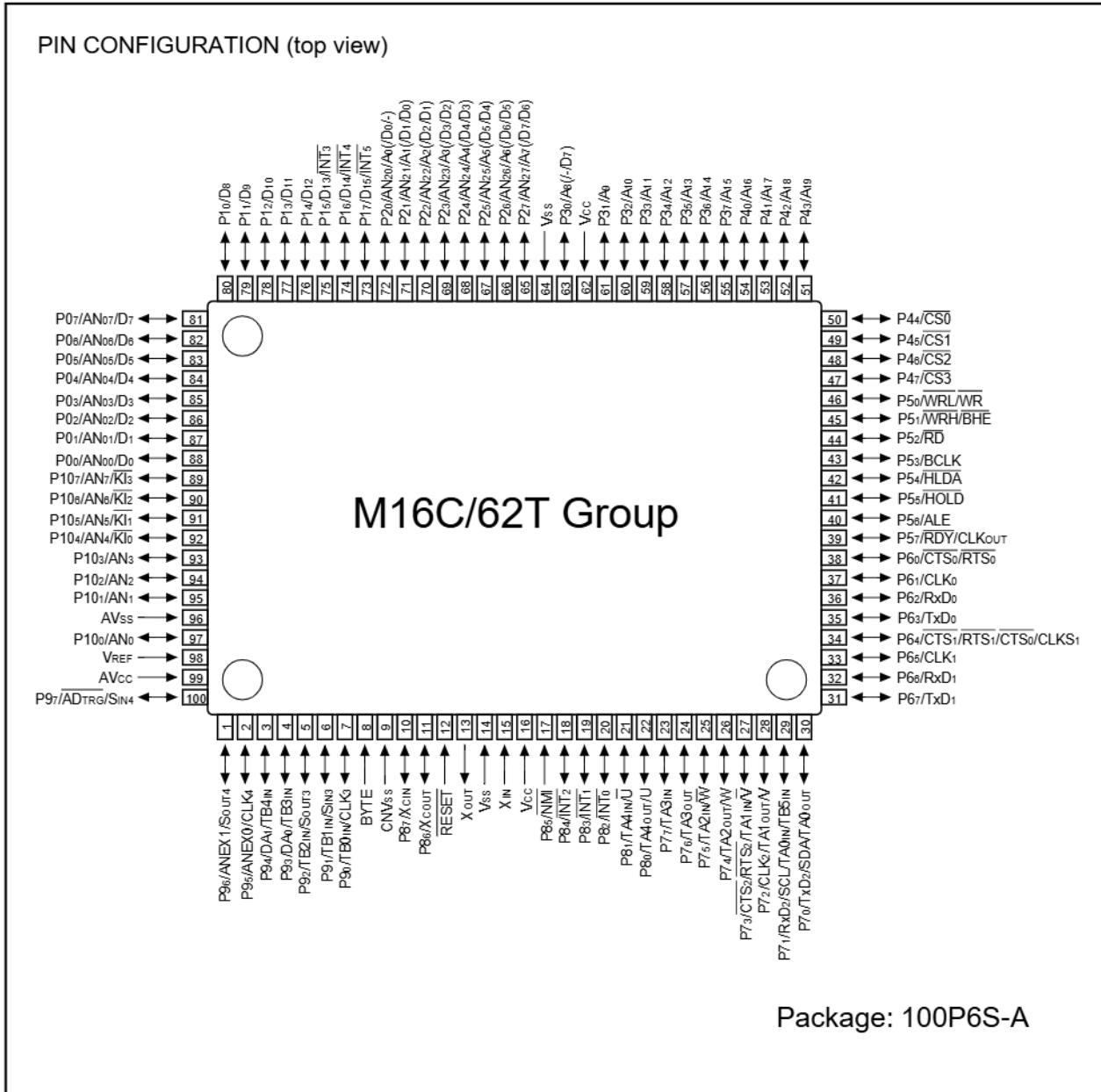

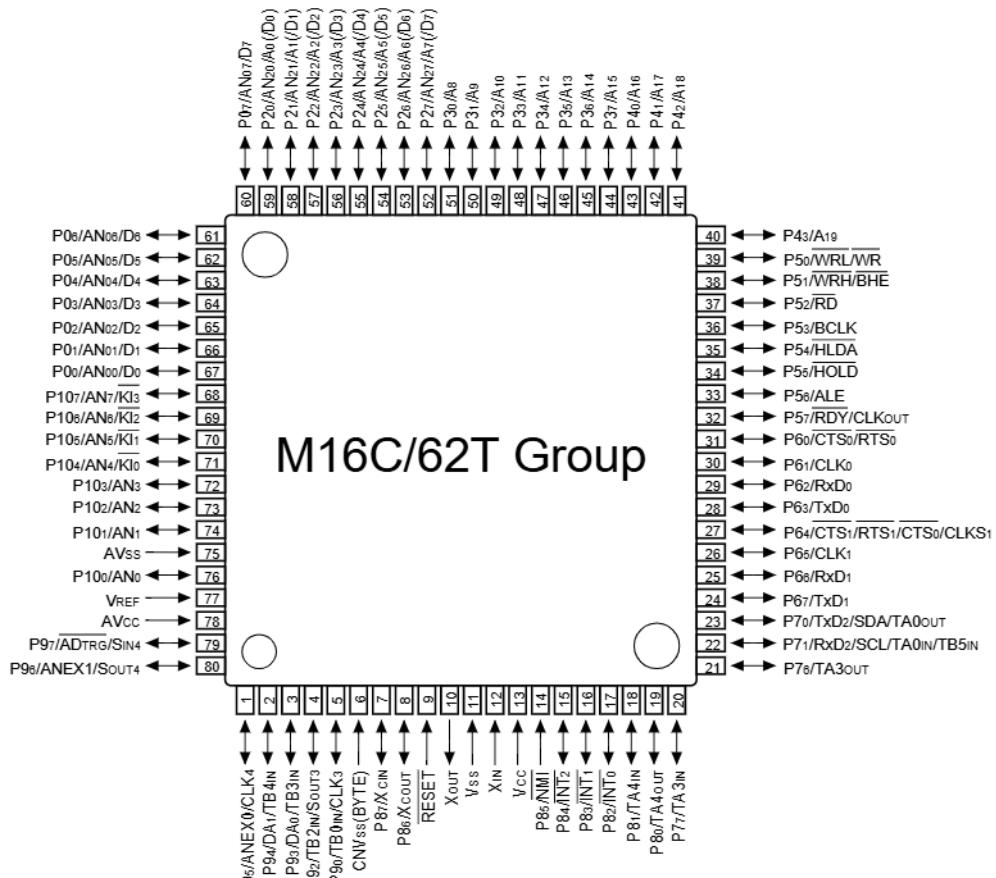

Figures 1.1.1 show the pin configurations (top view) of M30622(100-pin package) and 1.1.2 show the pin configurations (top view) of M30623(80-pin package).

Figure 1.1.1. Pin configuration (top view) of M30622 (100-pin package)

PIN CONFIGURATION (top view)

Package: 80P6S-A

Figure 1.1.2. Pin configuration (top view) of M30623 (80-pin package)

## Block Diagram

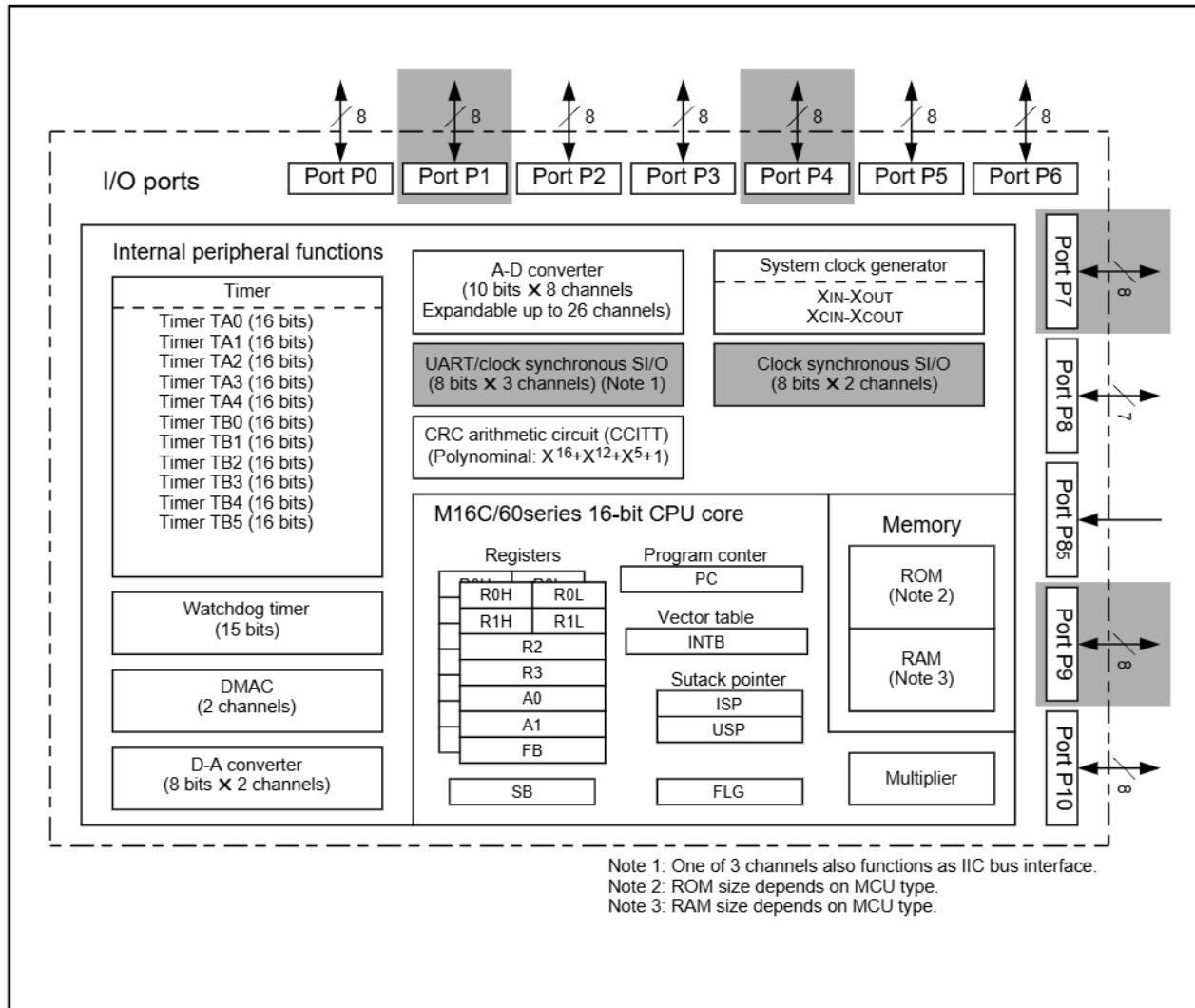

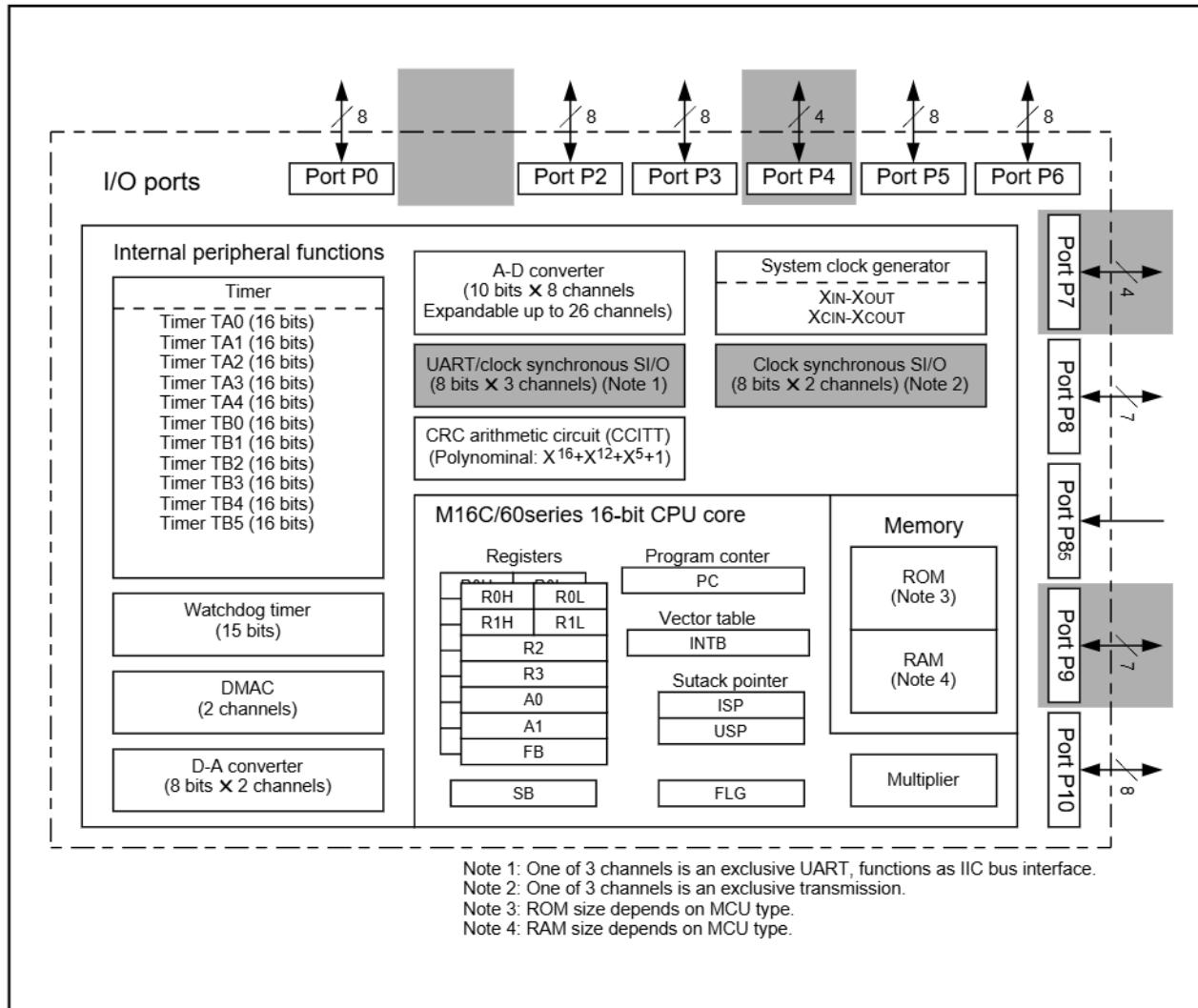

Figure 1.1.3 is block diagrams of M30622(100-pin package) and 1.1.4 is block diagrams of M30623(80-pin package).

Figure 1.1.3. Block diagram of M30622 (100-pin package)

Figure 1.1.4. Block diagram of M30623 (80-pin package)

## Performance Outline

Table 1.1.1 is a performance outline of M16C/62T group.

Table 1.1.1. Performance outline of M16C/62T group

| Item                                |                         | Performance                                                                                                                                                                         |                                                                  |

|-------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|                                     |                         | M30622(100-pin package)                                                                                                                                                             | M30623(80-pin package)                                           |

| Number of basic instructions        |                         | 91 instructions                                                                                                                                                                     |                                                                  |

| Shortest instruction execution time |                         | 62.5ns(f(XIN)=16MHz, Vcc=5V)                                                                                                                                                        |                                                                  |

| Memory capacity                     | ROM                     | 32Kbytes (M30623M4T-XXXGP)<br>64Kbytes (M30622M8T/M8V-XXXFP, M30623M8T/M8V-XXXGP)<br>128Kbytes (M30622MCT/MCV-XXXFP, M30623MCT/MCV-XXXGP, M30622ECT/ECV-XXXFP, M30623ECT/ECV-XXXGP) |                                                                  |

|                                     | RAM                     | 3Kbytes (M30623M4T-XXXGP)<br>4Kbytes (M30622M8T/M8V-XXXFP, M30623M8T/M8V-XXXGP)<br>5Kbytes (M30622MCT/MCV-XXXFP, M30623MCT/MCV-XXXGP, M30622ECT/ECV-XXXFP, M30623ECT/ECV-XXXGP)     |                                                                  |

| I/O port                            | P0, P2, P3, P5, P6, P10 | 8 bits x 6                                                                                                                                                                          |                                                                  |

|                                     | P1                      | 8 bits x 1                                                                                                                                                                          | —                                                                |

|                                     | P4, P7                  | 8 bits x 2                                                                                                                                                                          | 4 bits x 2                                                       |

|                                     | P8 (except P85)         | 7 bits x 1                                                                                                                                                                          |                                                                  |

|                                     | P9                      | 8 bits x 1                                                                                                                                                                          | 7 bits x 1                                                       |

| Input port                          | P85                     | 1 bit x 1                                                                                                                                                                           |                                                                  |

| Multifunction timer                 | TA0, A3, TA4            | 16 bits x 3 (cycle timer, external / internal event count, pulse output)                                                                                                            |                                                                  |

|                                     | TA1, TA2                | 16 bits x 2<br>(cycle timer, external / internal event count, pulse output)                                                                                                         | 16 bits x 2<br>(cycle timer, internal event count)               |

|                                     | TB0, TB2 to TB5         | 16 bits x 5 (cycle timer, external / internal event count, pulse period / pulse width measurement)                                                                                  |                                                                  |

|                                     | TB1                     | 16 bits x 1 (cycle timer, external / internal event count, pulse period / pulse width measurement)                                                                                  | 16 bits x 1<br>(cycle timer, internal event count)               |

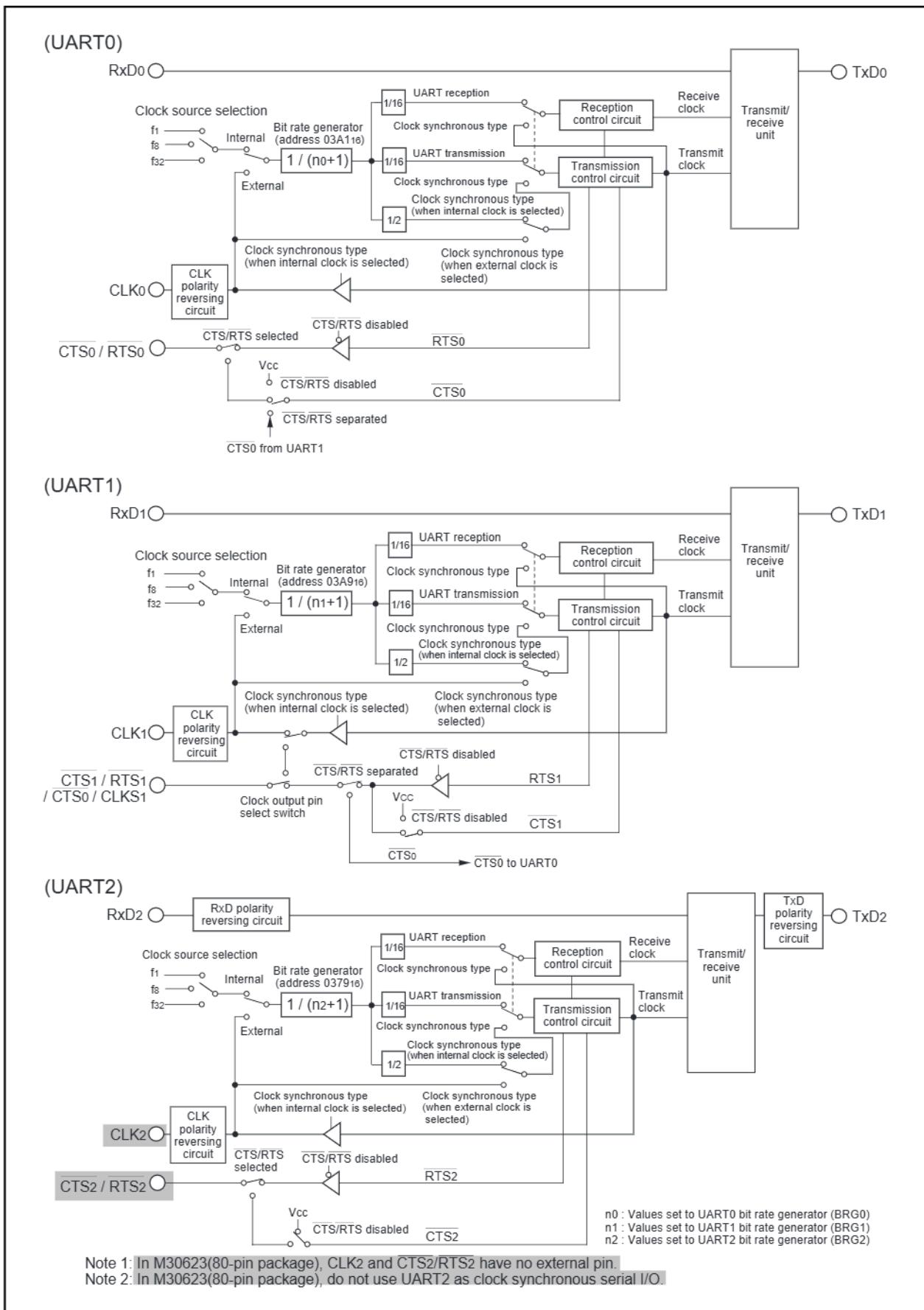

| Serial I/O                          | UART0, UART1            | (UART or clock synchronous) x 2                                                                                                                                                     |                                                                  |

|                                     | UART2                   | (UART or clock synchronous) x 1                                                                                                                                                     | UART x 1                                                         |

|                                     | SI/O3                   | (Clock synchronous) x 1                                                                                                                                                             | (Clock synchronous) x 1 (exclusive transmission)                 |

|                                     | SI/O4                   | (Clock synchronous) x 1                                                                                                                                                             |                                                                  |

| A-D converter                       |                         | 10 bits x (8 x 3 + 2) channels                                                                                                                                                      |                                                                  |

| D-A converter                       |                         | 8 bits x 2 channels                                                                                                                                                                 |                                                                  |

| DMAC                                |                         | 2 channels (trigger: 24 sources)                                                                                                                                                    |                                                                  |

| CRC calculation circuit             |                         | CRC-CCITT                                                                                                                                                                           |                                                                  |

| Watchdog timer                      |                         | 15 bits x 1 (with prescaler)                                                                                                                                                        |                                                                  |

| Interrupt                           |                         | 25 internal and 8 external sources, 4 software sources, 7 levels                                                                                                                    | 25 internal and 5 external sources, 4 software sources, 7 levels |

| Clock generating circuit            |                         | 2 built-in clock generation circuits<br>(built-in feedback resistor, and external ceramic or quartz oscillator)                                                                     |                                                                  |

| Supply voltage                      |                         | Mask ROM version : 4.2 to 5.5V (f(XIN)=16MHz, without software wait)<br>One-time PROM version : 4.5 to 5.5V (f(XIN)=16MHz, without software wait)                                   |                                                                  |

| Power consumption                   |                         | 140mW (Vcc=5V, f(XIN) = 16MHz)                                                                                                                                                      |                                                                  |

| I/O characteristics                 | I/O withstand voltage   | 5V                                                                                                                                                                                  |                                                                  |

|                                     | Output current          | 5mA                                                                                                                                                                                 |                                                                  |

| Memory expansion                    |                         | Available (to 1.2M bytes or 4M bytes)<br>(The M16C/62T group is not guaranteed to operate in memory expansion.)                                                                     |                                                                  |

| Operating ambient temperature       |                         | 85°C guaranteed version : -40°C to 85°C, 125°C guaranteed version : -40°C to 125°C                                                                                                  |                                                                  |

| Device configuration                |                         | CMOS high performance silicon gate                                                                                                                                                  |                                                                  |

| Package                             |                         | 100-pin plastic mold QFP                                                                                                                                                            | 80-pin plastic mold QFP                                          |

Description

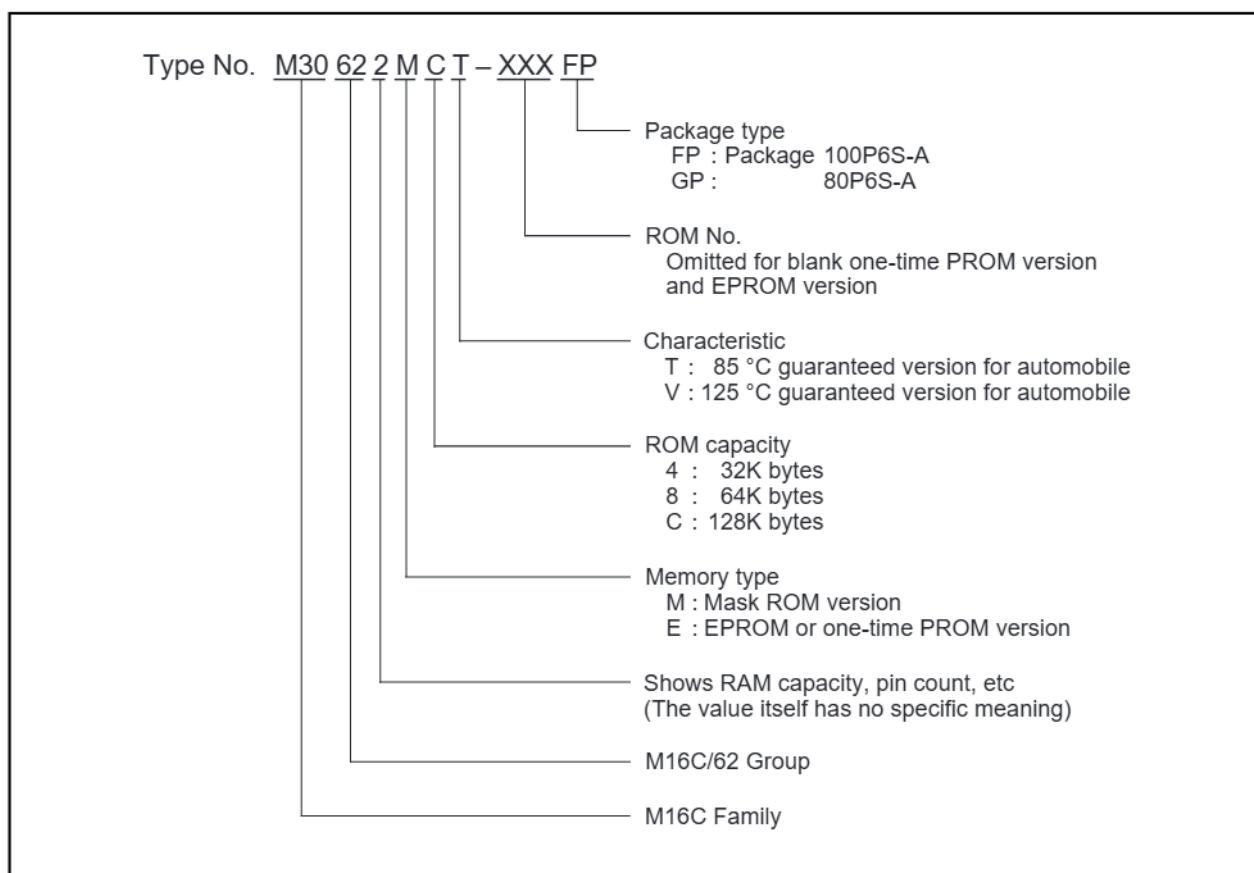

Mitsubishi plans to release the following products in the M16C/62T group:

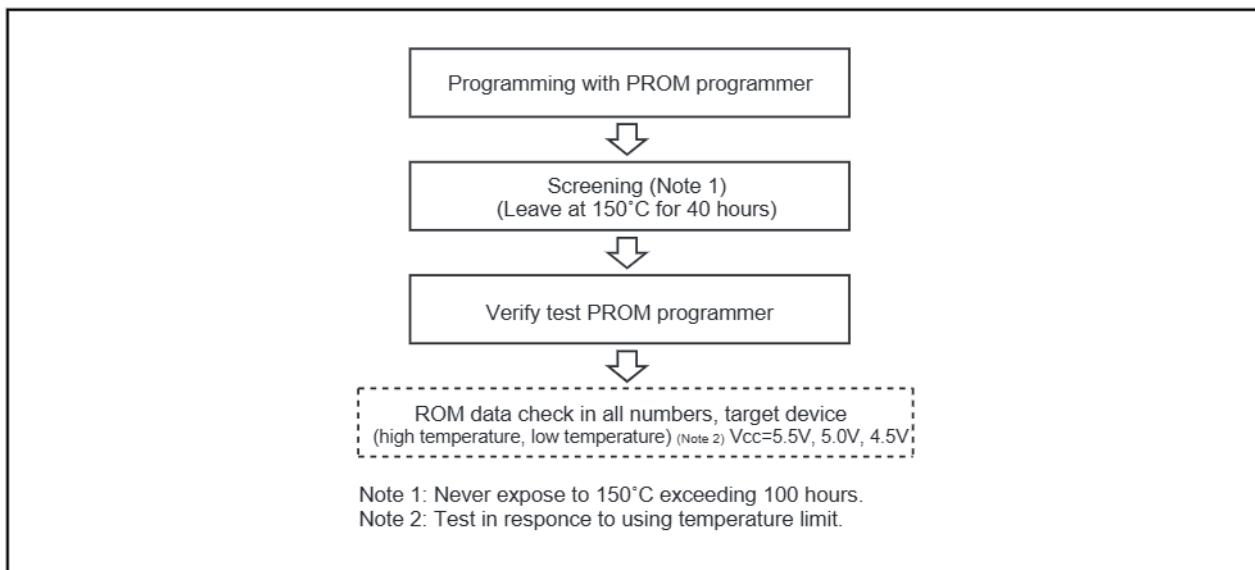

(1) Support for mask ROM version, one-time PROM version

One-time PROM version has the equally functions mask ROM version, with the exception of built-in electolic-programming-possible PROM.

(2) ROM capacity

(3) Package(number of pin)

100P6S-A : 100-pin plastic molded QFP

80P6S-A : 80-pin plastic molded QFP

(4) Support for 85°C guaranteed version, 125°C guaranteed version

125°C guaranteed version M30622MxV/ECV-XXXFP, M30623MxV/ECV-XXXGP is suported. These are different from 85°C guaranteed version M30622MxT/ECT-XXXFP, M30623MxT/ECT-XXXGP on operating ambient temperature and the terms of the use, and so please inquire.

| ROM size                                                                                                                                                                                                             | 100-pin packaege                   |                                                                    | 80-pin packaege                    |                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------|

|                                                                                                                                                                                                                      |                                    |                                                                    |                                    |                                                                    |

| 128K bytes                                                                                                                                                                                                           | M30622MCT-XXXFP<br>M30622MCV-XXXFP | M30622ECT-XXXFP<br>M30622ECTFP*<br>M30622ECV-XXXFP<br>M30622ECVFP* | M30623MCT-XXXGP<br>M30623MCV-XXXGP | M30623ECT-XXXGP<br>M30623ECTGP*<br>M30623ECV-XXXGP<br>M30623ECVGP* |

| 64K bytes                                                                                                                                                                                                            | M30622M8T-XXXFP<br>M30622M8V-XXXFP |                                                                    | M30623M8T-XXXGP<br>M30623M8V-XXXGP |                                                                    |

| 32K bytes                                                                                                                                                                                                            |                                    |                                                                    | M30623M4T-XXXGP                    |                                                                    |

|                                                                                                                                                                                                                      | Mask ROM version                   | One-time PROM version                                              | Mask ROM version                   | One-time PROM version                                              |

|                                                                                                                                                                                                                      | * Shipped in blank                 |                                                                    |                                    |                                                                    |

| Note 1: It may change in the future.<br>Note 2: Use shipped in blank of one-time PROM version as the trial, development of program.<br>In case of vehicle-mount test or mass production, use shipped in programming. |                                    |                                                                    |                                    |                                                                    |

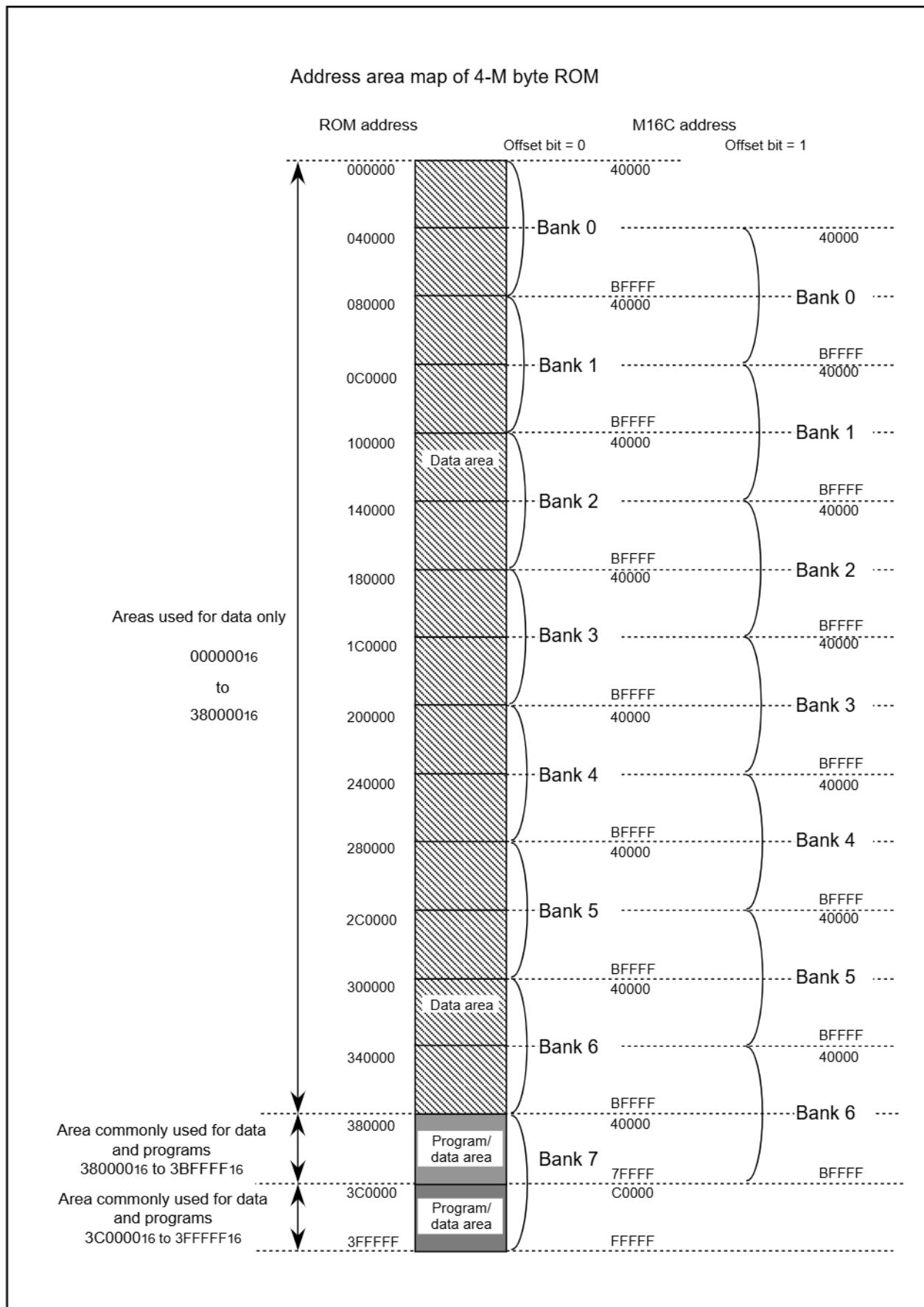

Figure 1.1.5. ROM expansion

Now: Mar.1999.

The M16C/62T group products currently supported are listed in Table 1.1.2.

**Table 1.1.2. M16C/62T group**

**Now: Mar.1999.**

| Type No.        | ROM capacity | RAM capacity | Characteristic                     | Package  | Remarks                             |

|-----------------|--------------|--------------|------------------------------------|----------|-------------------------------------|

| M30622M8T-XXXFP | 64K bytes    | 4K bytes     | 85 °C guaranteed version           | 100P6S-A | Mask ROM version                    |

| M30622M8V-XXXFP |              |              | 125 °C guaranteed version (Note 3) |          |                                     |

| M30622MCT-XXXFP |              |              | 85 °C guaranteed version           |          | Mask ROM version                    |

| M30622ECT-XXXFP |              |              |                                    |          | One-time PROM version (programming) |

| M30622ECTFP     |              |              |                                    |          | One-time PROM version (blank)       |

| M30622MCV-XXXFP |              |              | 125 °C guaranteed version (Note 3) |          | Mask ROM version                    |

| M30622ECV-XXXFP |              |              |                                    |          | One-time PROM version (programming) |

| M30622ECVFP     |              |              |                                    |          | One-time PROM version (blank)       |

| M30623M4T-XXXGP | 32K bytes    | 3K bytes     | 85 °C guaranteed version           | 80P6S-A  | Mask ROM version                    |

| M30623M8T-XXXGP | 64K bytes    | 4K bytes     | 85 °C guaranteed version           |          | Mask ROM version                    |

| M30623M8V-XXXGP |              |              | 125 °C guaranteed version (Note 3) |          |                                     |

| M30623MCT-XXXGP | 128K bytes   | 5K bytes     | 85 °C guaranteed version           |          | Mask ROM version                    |

| M30623ECT-XXXGP |              |              |                                    |          | One-time PROM version (programming) |

| M30623ECTGP     |              |              |                                    |          | One-time PROM version (blank)       |

| M30623MCV-XXXGP |              |              | 125 °C guaranteed version (Note 3) |          | Mask ROM version                    |

| M30623ECV-XXXGP |              |              |                                    |          | One-time PROM version (programming) |

| M30623ECVGP     |              |              |                                    |          | One-time PROM version (blank)       |

Note 1: It may change in the future.

Note 2: Use shipped in blank of one-time PROM version as the trial, development of program.

In case of vehicle-mount test or mass production, use shipped in programming.

Note 3: It is different from 85°C guaranteed version on operating ambient temperature and the terms of the use, please inquire.

**Figure 1.1.6. Type No., memory size, and package**

Pin Description

**Pin Description**

| Pin name              | Signal name                          | I/O type               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|--------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss              | Power supply input                   |                        | Supply 4.2 V to 5.5 V to the Vcc pin. Supply 0 V to the Vss pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

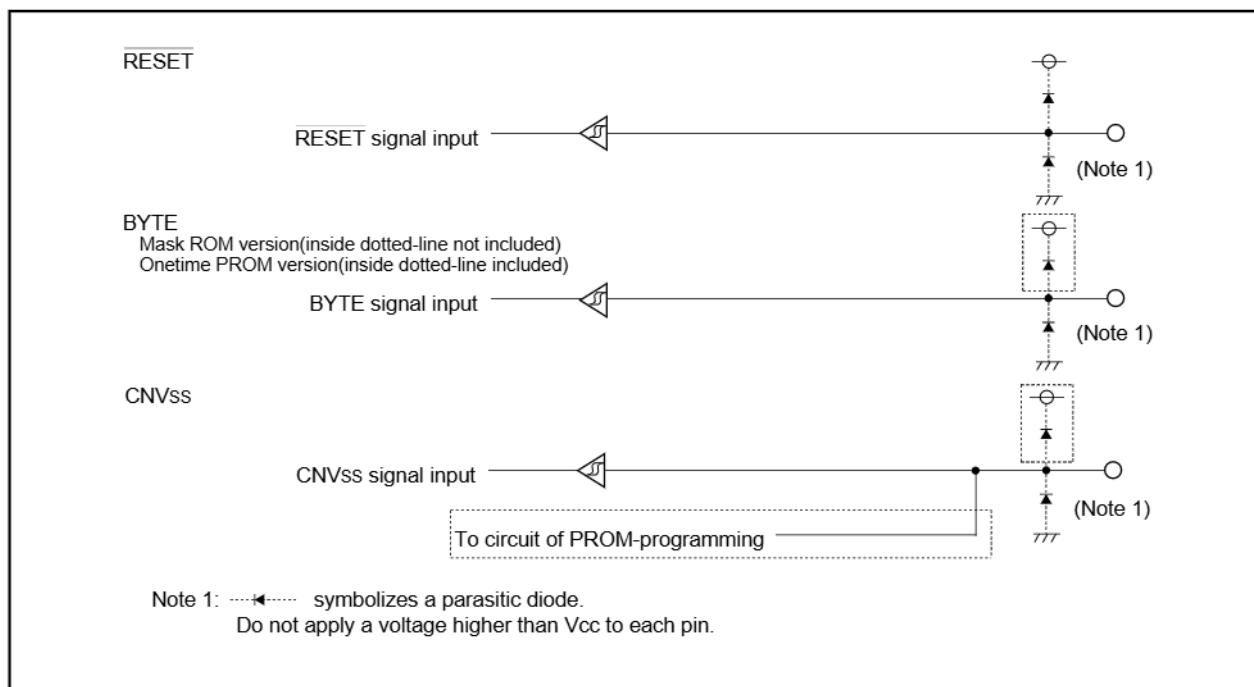

| CNVss                 | CNVss                                | Input                  | This pin switches between processor modes. Connect it to the Vss pin when operating in single-chip or memory expansion mode. Connect it to the Vcc pin when operating in microprocessor mode.                                                                                                                                                                                                                                                                                                                                         |

| RESET                 | Reset input                          | Input                  | A "L" on this input resets the microcomputer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XIN<br>XOUT           | Clock input<br>Clock output          | Input<br>Output        | These pins are provided for the main clock generating circuit. Connect a ceramic resonator or crystal between the XIN and the XOUT pins. To use an externally derived clock, input it to the XIN pin and leave the XOUT pin open.                                                                                                                                                                                                                                                                                                     |

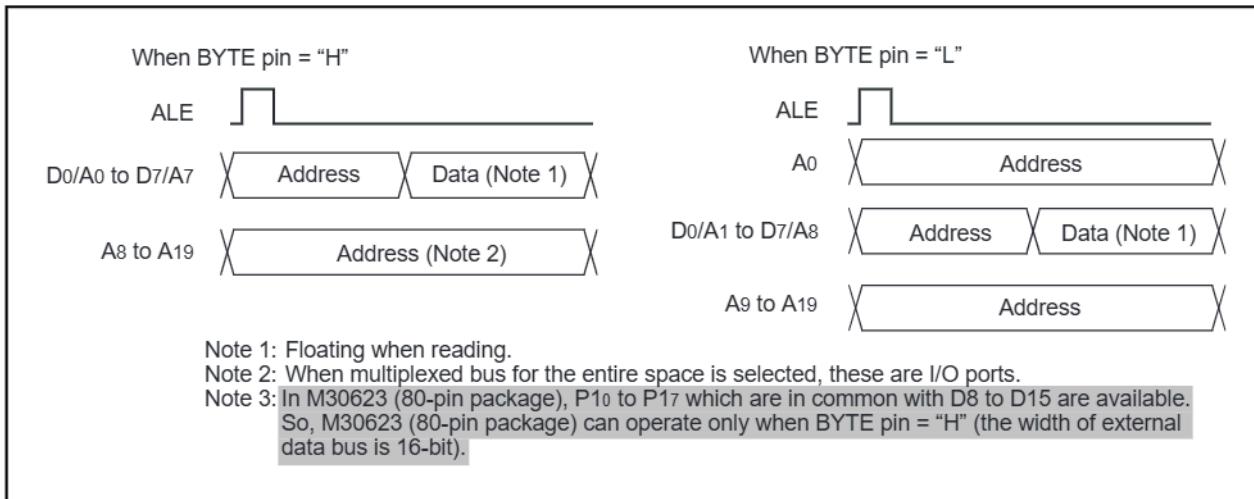

| BYTE                  | External data bus width select input | Input                  | This pin selects the width of an external data bus. A 16-bit width is selected when this input is "L"; an 8-bit width is selected when this input is "H". This input must be fixed to either "H" or "L". When operating in single-chip mode, connect this pin to Vss. In M30623 (80-pin package), the BYTE signal is internally connected to the CNVss signal.                                                                                                                                                                        |

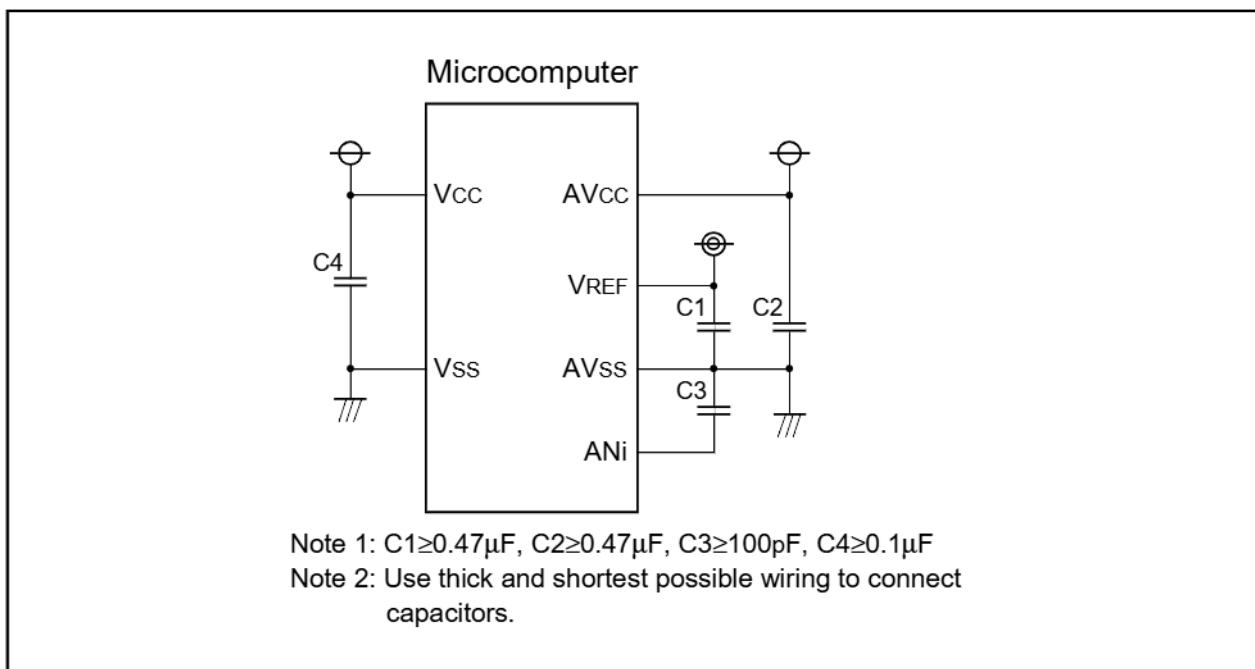

| AVCC                  | Analog power supply input            |                        | This pin is a power supply input for the A-D converter. Connect this pin to Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AVss                  | Analog power supply input            |                        | This pin is a power supply input for the A-D converter. Connect this pin to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VREF                  | Reference voltage input              | Input                  | This pin is a reference voltage input for the A-D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

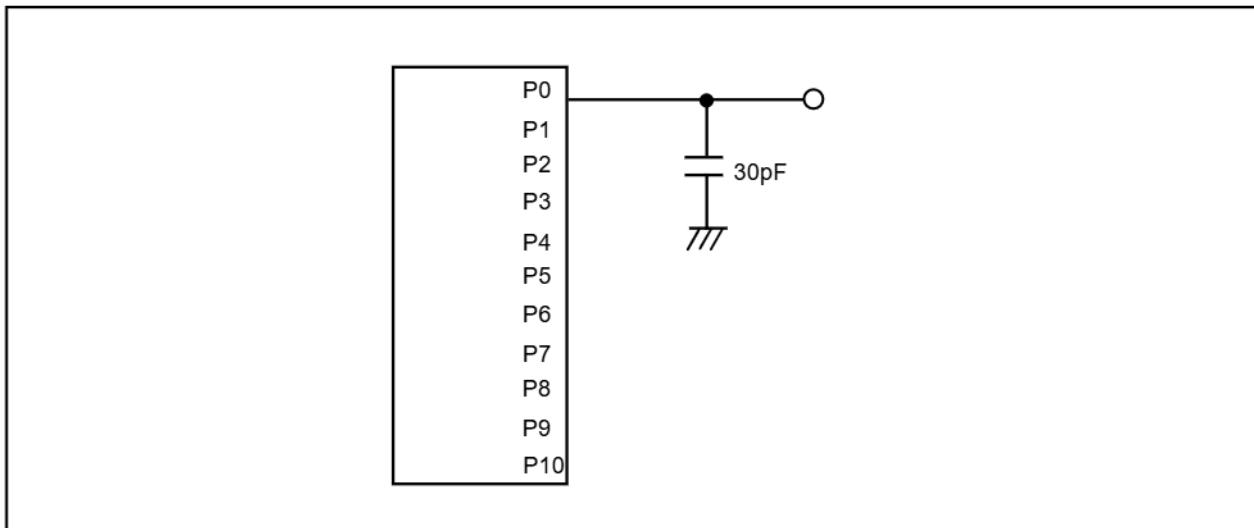

| P00 to P07            | I/O port P0                          | Input/output           | This is an 8-bit CMOS I/O port. It has an input/output port direction register that allows the user to set each pin for input or output individually. When used for input in single-chip mode, the port can be set to have or not have a pull-up resistor in units of four bits by software. In memory expansion and microprocessor modes, selection of the internal pull-resistor is not available. Pins in this port also function as A-D converter extended input pins as selected by software when operating in single-chip mode. |

| D0 to D7              |                                      | Input/output           | When set as a separate bus, these pins input and output data (D0–D7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P10 to P17            | I/O port P1                          | Input/output           | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as external interrupt pins as selected by software.                                                                                                                                                                                                                                                                                                                                                                                                       |

| D8 to D15             |                                      | Input/output           | When set as a separate bus, these pins input and output data (D8–D15).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P20 to P27            | I/O port P2                          | Input/output           | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as A-D converter extended input pins as selected by software when operating in single-chip mode.                                                                                                                                                                                                                                                                                                                                                          |

| A0 to A7              |                                      | Output                 | These pins output 8 low-order address bits (A0–A7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A0/D0 to<br>A7/D7     |                                      | Input/output           | If the external bus is set as an 8-bit wide multiplexed bus, these pins input and output data (D0–D7) and output 8 low-order address bits (A0–A7) separated in time by multiplexing.                                                                                                                                                                                                                                                                                                                                                  |

| A0, A1/D0<br>to A7/D6 |                                      | Output<br>Input/output | If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (D0–D6) and output address (A1–A7) separated in time by multiplexing. They also output address (A0).                                                                                                                                                                                                                                                                                                                                    |

| P30 to P37            | I/O port P3                          | Input/output           | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A8 to A15             |                                      | Output                 | These pins output 8 middle-order address bits (A8–A15).                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A8/D7,<br>A9 to A15   |                                      | Input/output           | If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (D7) and output address (A8) separated in time by multiplexing. They also output address (A9–A15).                                                                                                                                                                                                                                                                                                                                      |

## Pin Description

| Pin name                                                                                   | Signal name                     | I/O type                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P40 to P47<br>CS0 to CS3,<br>A16 to A19                                                    | I/O port P4                     | Input/output<br>Output<br>Output                                                         | This is an 8-bit I/O port equivalent to P0.<br>These pins output CS0-CS3 signals and A16-A19. CS0-CS3 are chip select signals used to specify an access space. A16-A19 are 4 high-order address bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

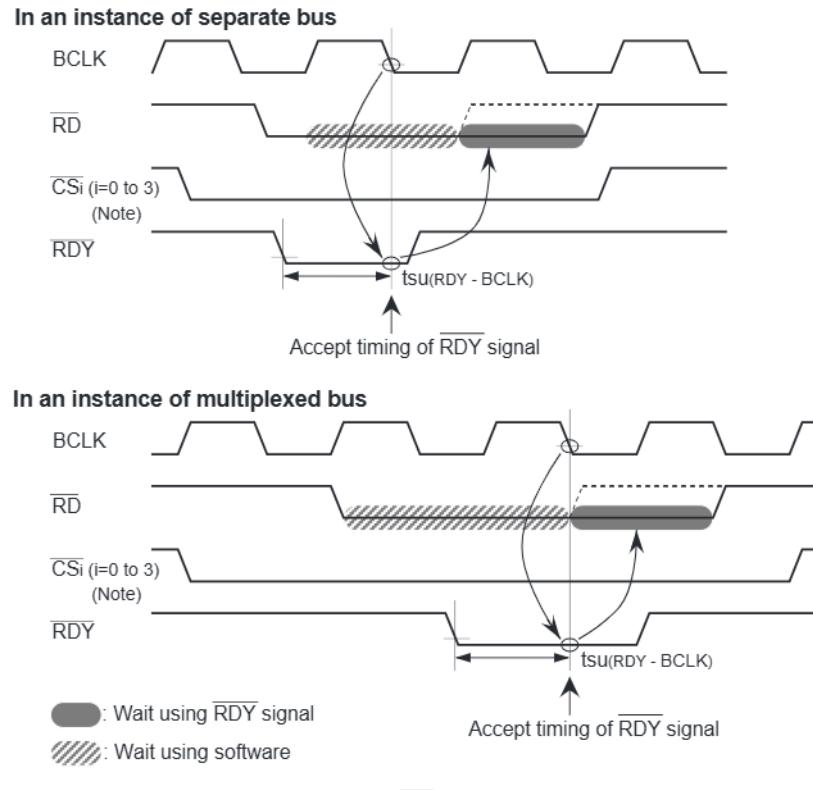

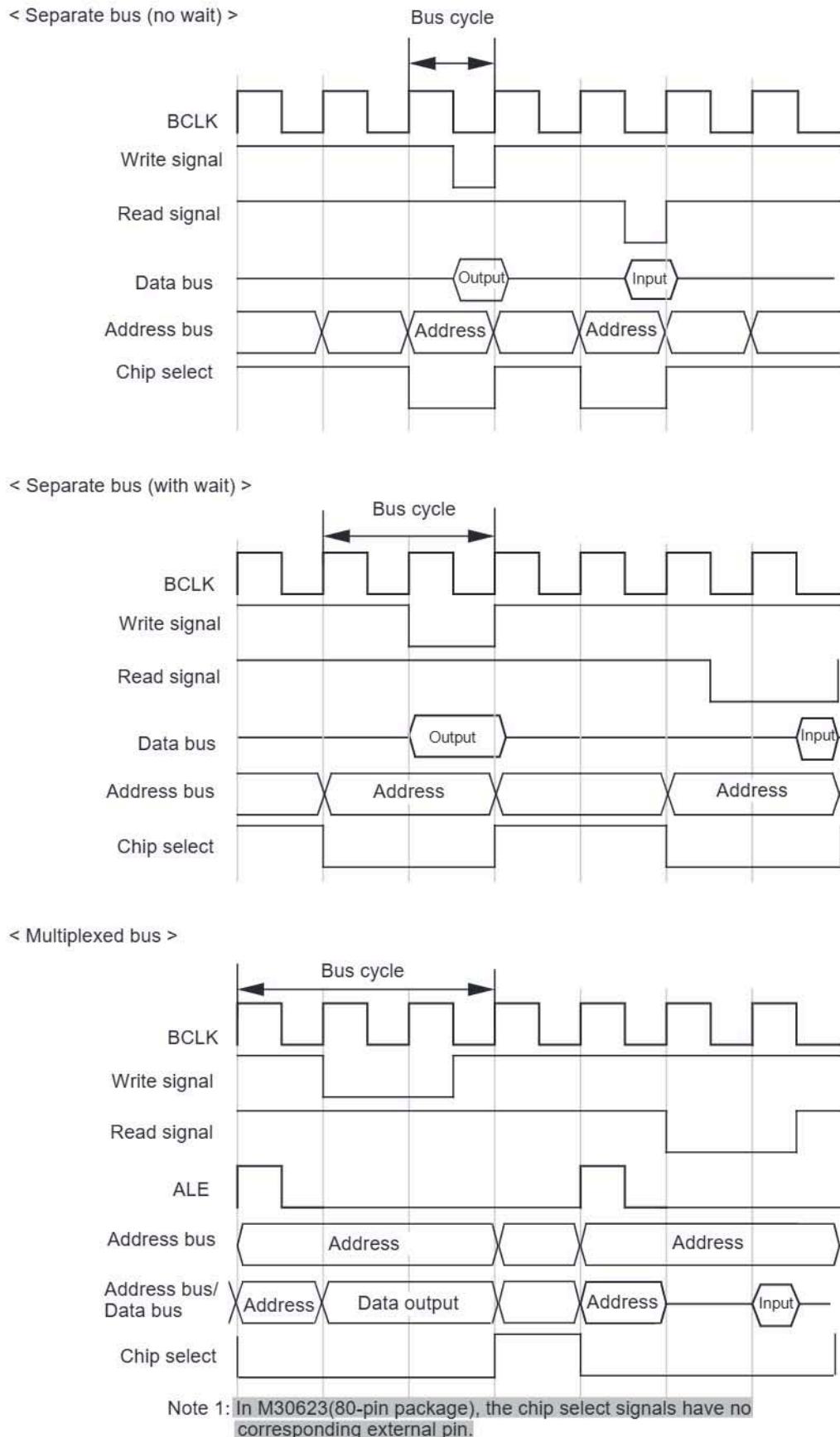

| P50 to P57<br><br>WRL/WR,<br>WRH/BHE,<br>RD,<br>BCLK,<br>HLDA,<br>HOLD,<br><br>ALE,<br>RDY | I/O port P5                     | Input/output<br><br>Output<br>Output<br>Output<br>Output<br>Input<br><br>Output<br>Input | This is an 8-bit I/O port equivalent to P0. In single-chip mode, P57 in this port outputs a divide-by-8 or divide-by-32 clock of XIN or a clock of the same frequency as XCIN as selected by software.<br><br>Output WRL, WRH (WR and BHE), RD, BCLK, HLDA, and ALE signals. WRL and WRH, and BHE and WR can be switched using software control.<br>■ WRL, WRH, and RD selected<br>With a 16-bit external data bus, data is written to even addresses when the WRL signal is "L" and to the odd addresses when the WRH signal is "L". Data is read when RD is "L".<br>■ WR, BHE, and RD selected<br>Data is written when WR is "L". Data is read when RD is "L". Odd addresses are accessed when BHE is "L". Use this mode when using an 8-bit external data bus.<br>While the input level at the HOLD pin is "L", the microcomputer is placed in the hold state. While in the hold state, HLDA outputs a "L" level. ALE is used to latch the address. While the input level of the RDY pin is "L", the microcomputer is in the ready state. |

| P60 to P67                                                                                 | I/O port P6                     | Input/output                                                                             | This is an 8-bit I/O port equivalent to P0. When used for input in single-chip, memory expansion, and microprocessor modes, the port can be set to have or not have a pull-up resistor in units of four bits by software. Pins in this port also function as UART0 and UART1 I/O pins as selected by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P70 to P77                                                                                 | I/O port P7                     | Input/output                                                                             | This is an 8-bit I/O port equivalent to P6 (P70 and P71 are N channel open-drain output). Pins in this port also function as timer A0-A3, timer B5 or UART2 I/O pins as selected by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P80 to P84,<br>P86,<br>P87,<br>P85                                                         | I/O port P8<br><br>I/O port P85 | Input/output<br>Input/output<br>Input/output<br>Input                                    | P80 to P84, P86 and P87 are I/O ports with the same functions as P6. Using software, they can be made to function as the I/O pins for timer A4 and the input pins for external interrupts. P86 and P87 can be set using software to function as the I/O pins for a sub clock generation circuit. In this case, connect a quartz oscillator between P86 (XCOUT pin) and P87 (XCIN pin). P85 is an input-only port that also functions for NMI. The NMI interrupt is generated when the input at this pin changes from "H" to "L". The NMI function cannot be cancelled using software. The pull-up cannot be set for this pin.                                                                                                                                                                                                                                                                                                                                                                                                                |

| P90 to P97                                                                                 | I/O port P9                     | Input/output                                                                             | This is an 8-bit I/O port equivalent to P6. Pins in this port also function as SI/O 3, 4 I/O pins, timer B0-B4 input pins, D-A converter output pins, A-D converter extended input pins, or A-D trigger input pins as selected by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

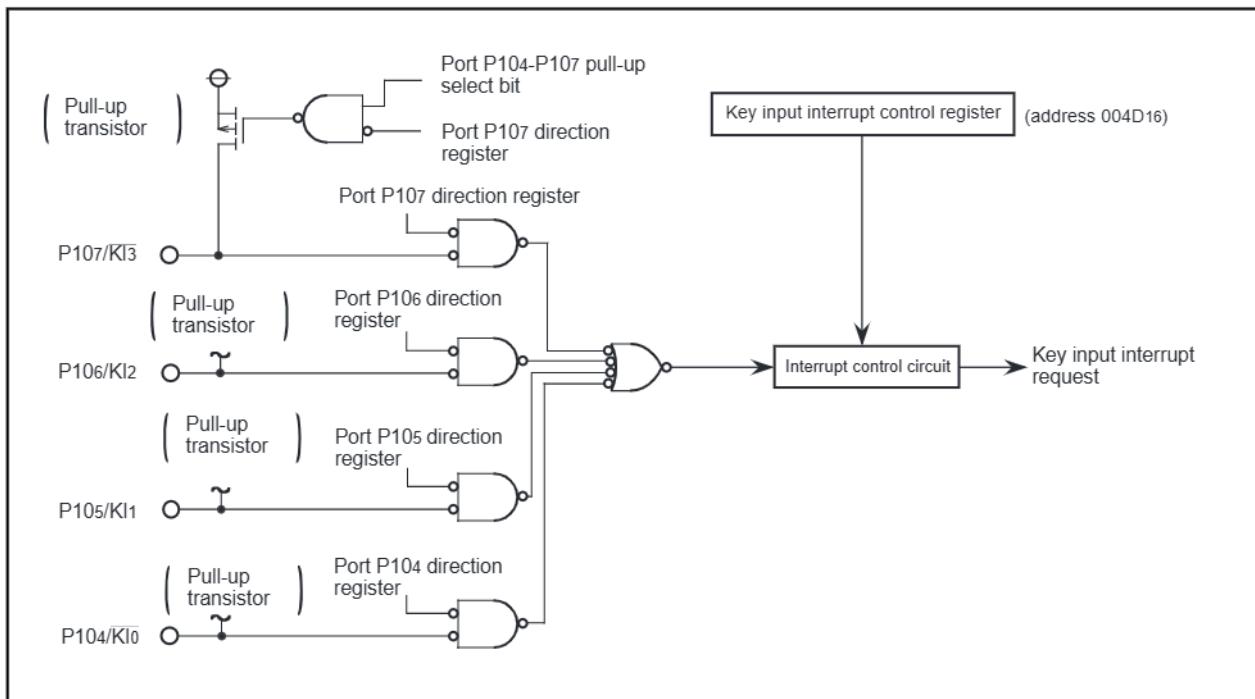

| P100 to P107                                                                               | I/O port P10                    | Input/output                                                                             | This is an 8-bit I/O port equivalent to P6. Pins in this port also function as A-D converter input pins. Furthermore, P104-P107 also function as input pins for the key input interrupt function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Note 1: In M30623(80-pin package), the following signals do not have the corresponding external pin.

- P10/D8 to P14/D12, P15/D13/INT3 to P17/D15/INT5

- P44/CS0 to P47/CS3

- P72/CLK2/TA1OUT/V, P73/CST2/RTS2/TA1IN/V, P74/TA2OUT/W, P75/TA2IN/W

- P91/TB1IN/SIN3

Note 2: The M16C/62T group is not guaranteed to operate in memory expansion and microprocessor modes.

## Operation of Functional Blocks

The M16C/62T group accommodates certain units in a single chip. These units include ROM and RAM to store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations. Also included are peripheral units such as timers, serial I/O, D-A converter, DMAC, CRC calculation circuit, A-D converter, and I/O ports.

The following explains each unit.

## Memory

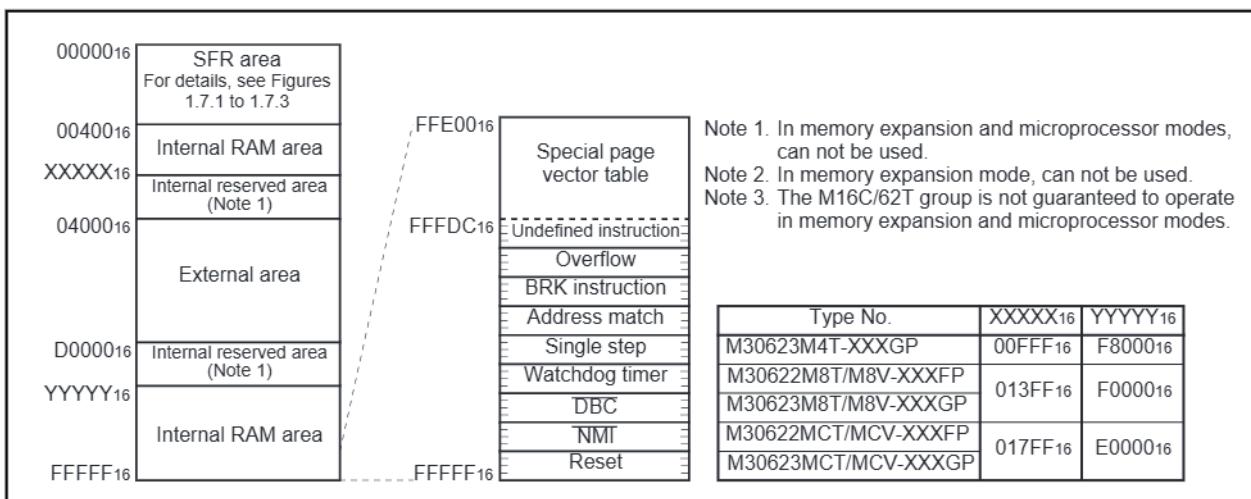

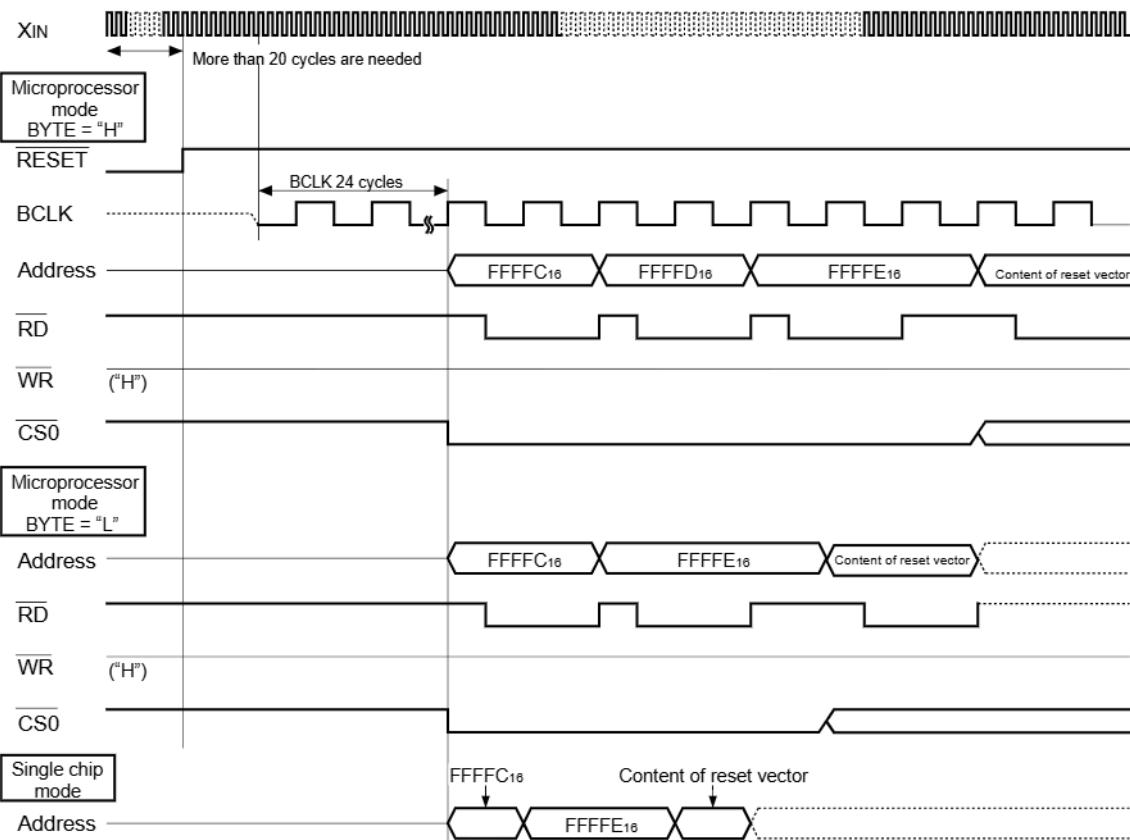

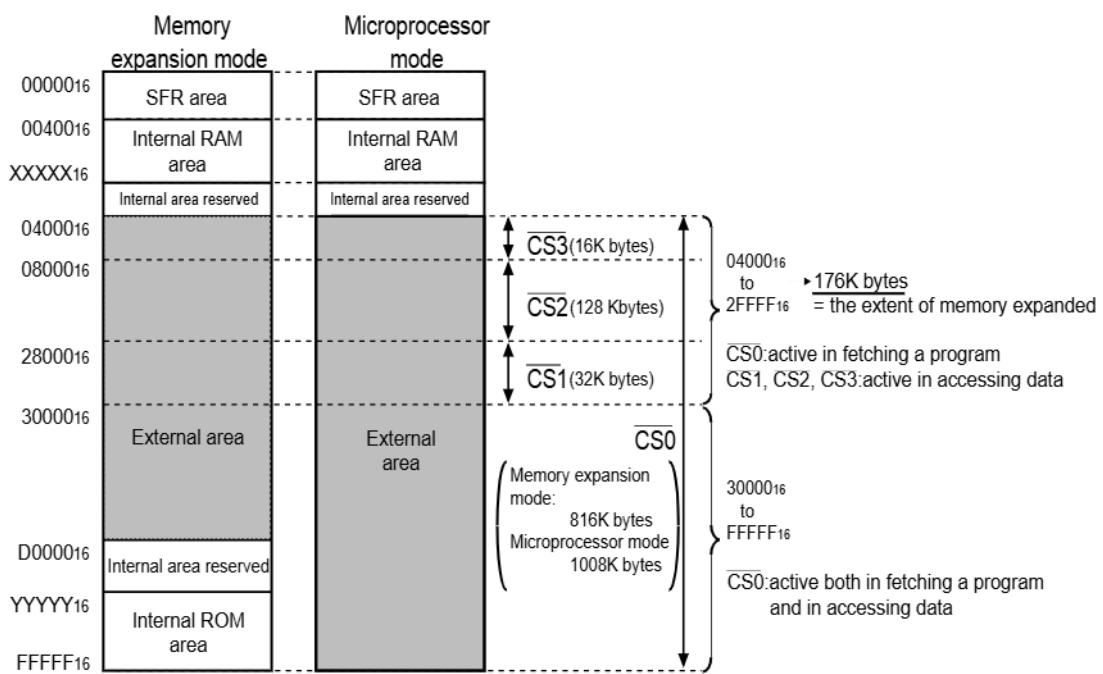

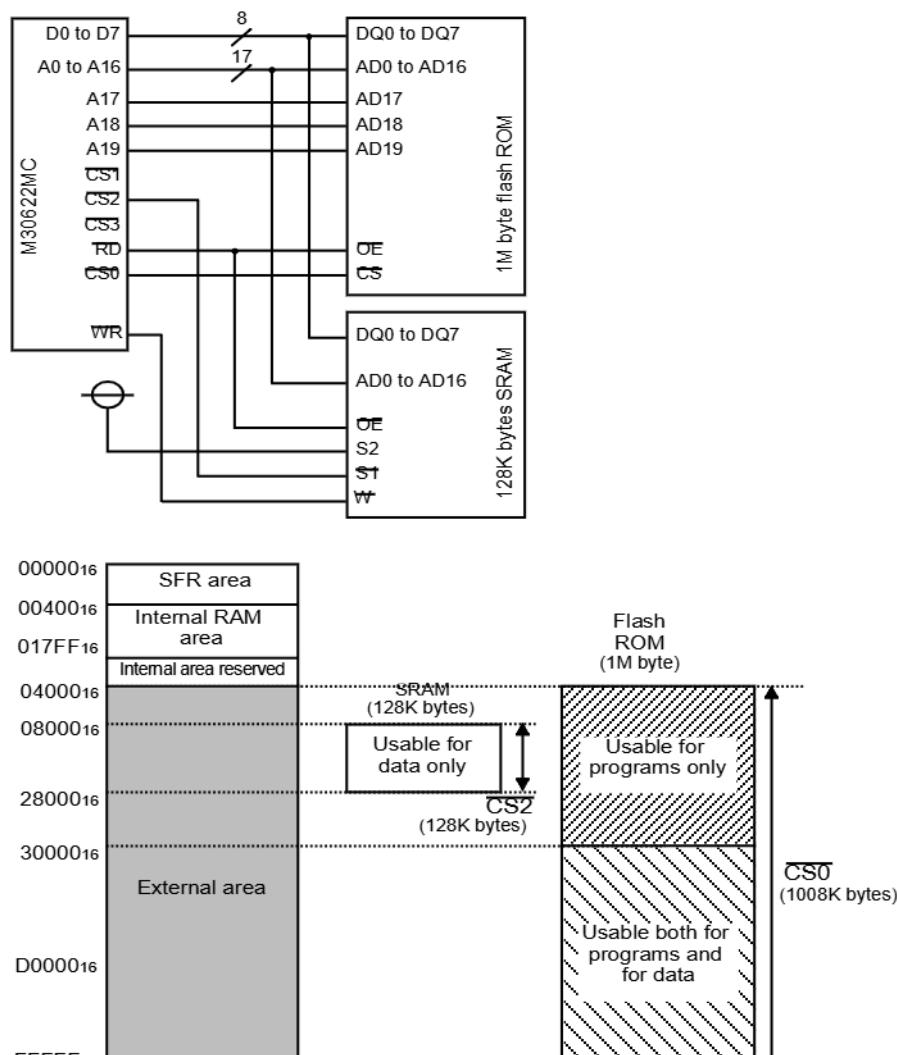

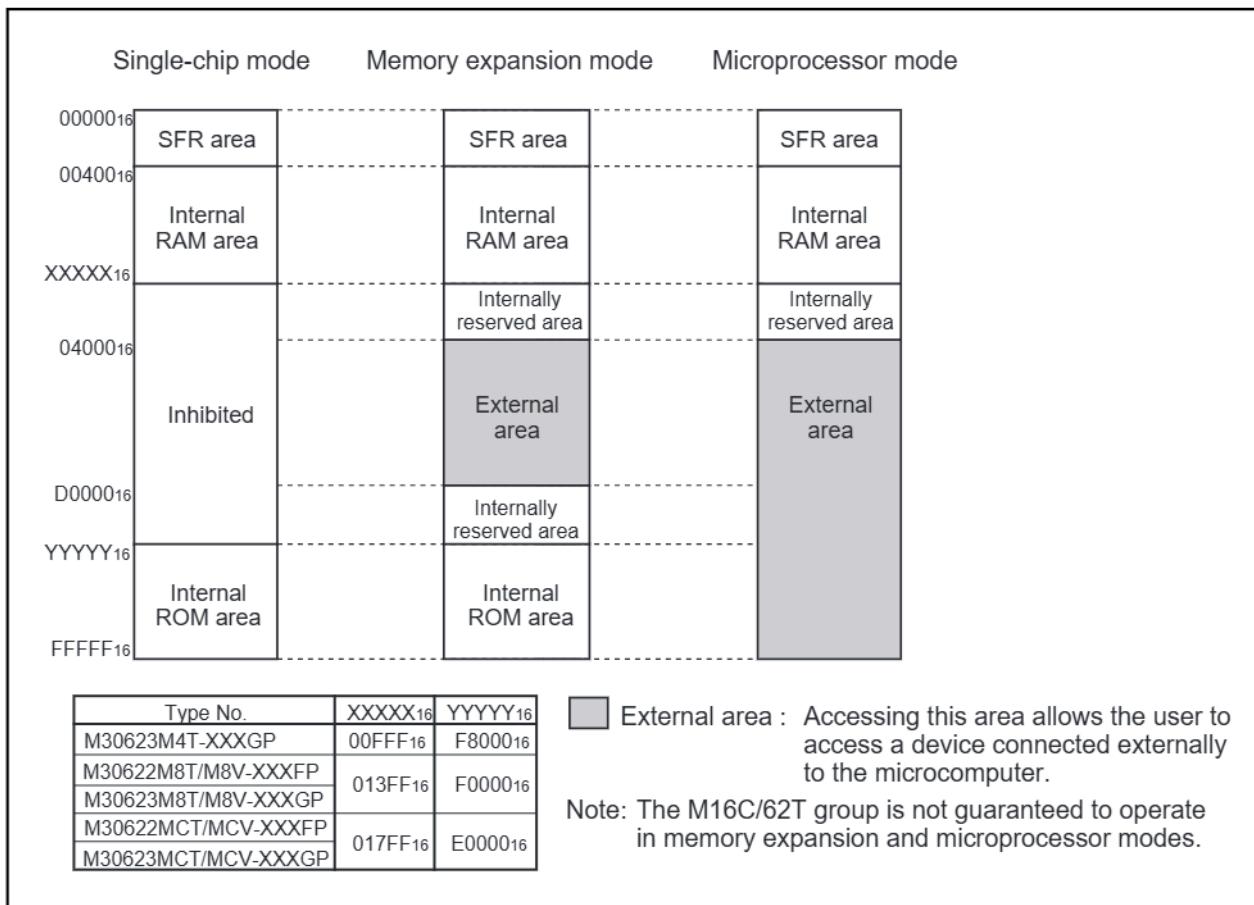

Figure 1.4.1 is a memory map of the M16C/62T group. The address space extends the 1M bytes from address 0000016 to FFFFFF16.

Internal ROM is located as the following, in M30623M4T-XXXGP from address F800016 to FFFFFF16 (32K bytes), in M30622M8T/M8V-XXXFP and M30623M8T/M8V-XXXGP from address F000016 to FFFFFF16 (64K bytes), in M30622MCT/MCV-XXXFP and M30623MCT/MCV-XXXGP from address E000016 to FFFFFF16 (128K bytes).

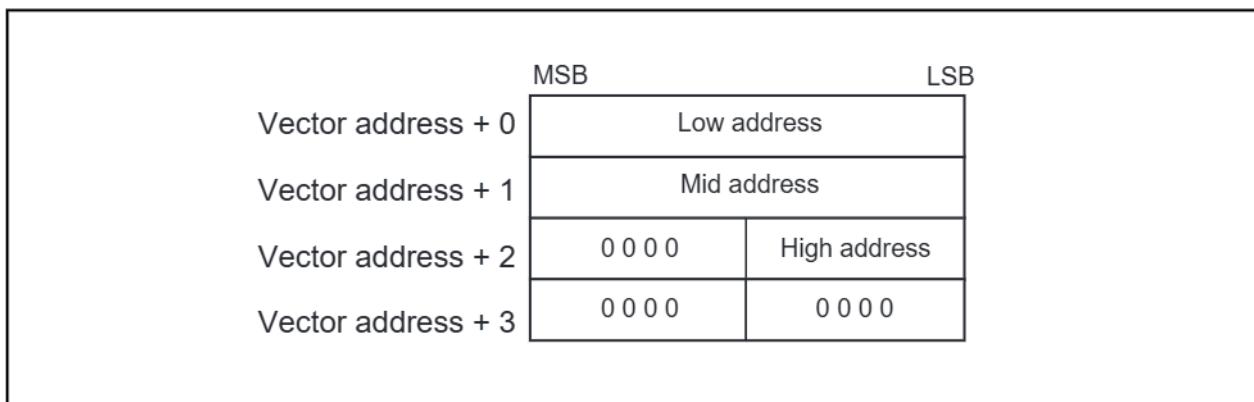

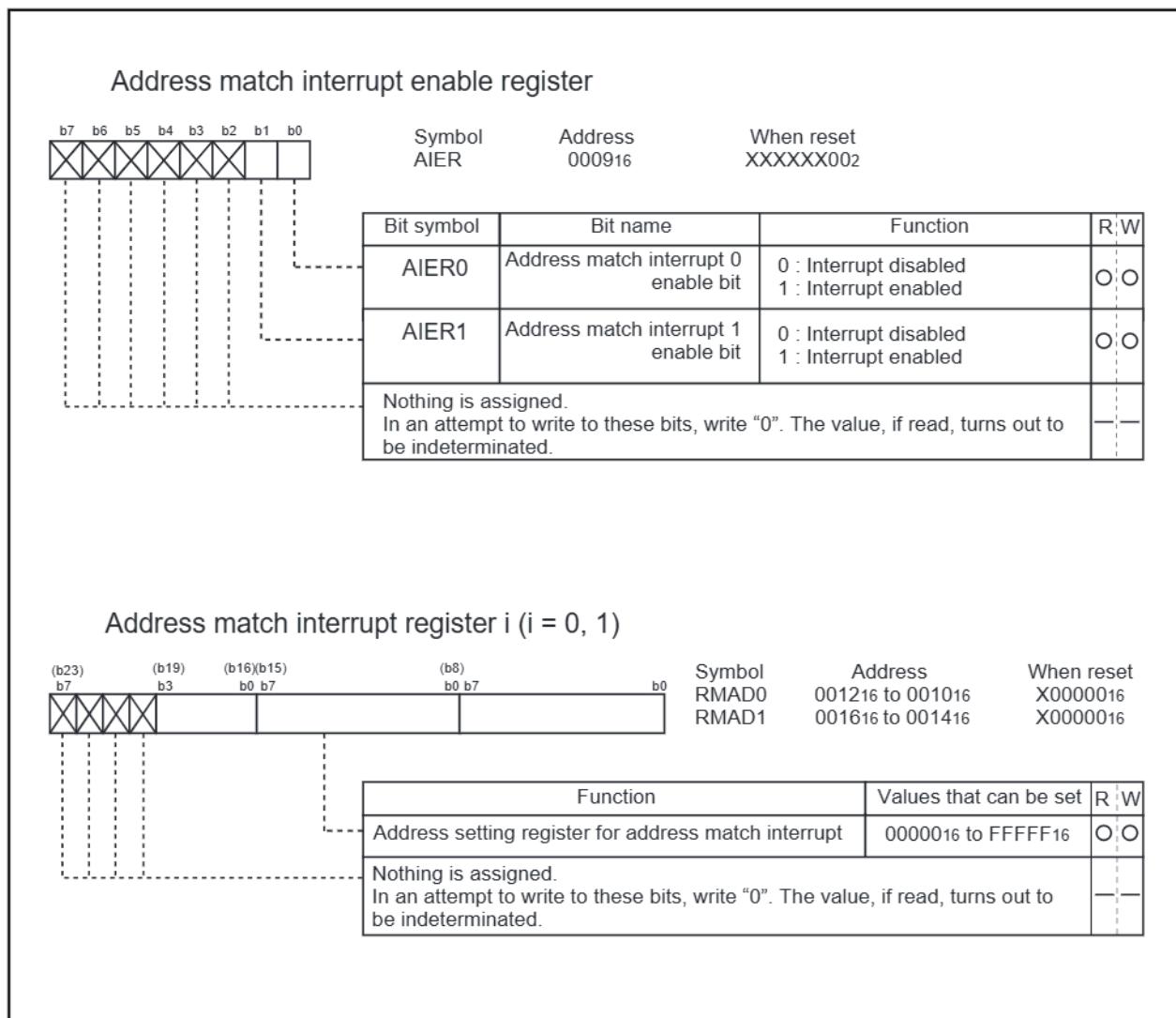

The vector table for fixed interrupts such as the reset and NMI are mapped to FFFDC16 to FFFFFF16. The starting address of the interrupt routine is stored here. The address of the vector table for timer interrupts, etc., can be set as desired using the internal register (INTB). See the section on interrupts for details.

Internal RAM is located as the following, in M30623M4T-XXXGP from address 0040016 to 00FFF16 (3K bytes), in M30622M8T/M8V-XXXFP and M30623M8T/M8V-XXXGP from address 0040016 to 013FF16 (4K bytes), in M30622MCT/MCV-XXXFP and M30623MCT/MCV-XXXGP from address 0040016 to 017FF16 (5K bytes). In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated.

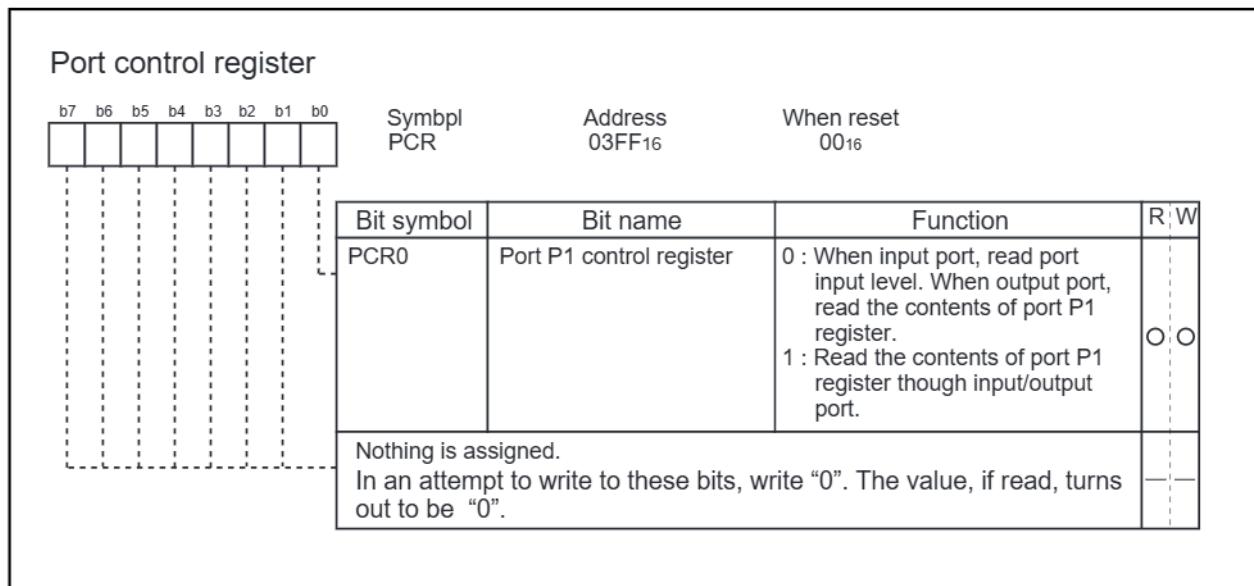

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for peripheral devices such as I/O ports, A-D converter, serial I/O, and timers, etc. Figures 1.7.1 to 1.7.3 are location of peripheral unit control registers. Any part of the SFR area that is not occupied is reserved and cannot be used for other purposes.

The special page vector table is mapped to FFE0016 to FFFDB16. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as 2-byte instructions, reducing the number of program steps.

In memory expansion mode and microprocessor mode, a part of the spaces are reserved and cannot be used. For example, in the M30623MCT/MCV-XXXGP, the following spaces cannot be used.

- The space between 0100016 and 03FFF16 (Memory expansion and microprocessor modes)

- The space between D000016 and D7FFF16 (Memory expansion mode)

But the M16C/62T group is not guaranteed to operate in memory expansion and microprocessor modes.

Figure 1.4.1. Memory map

## Central Processing Unit (CPU)

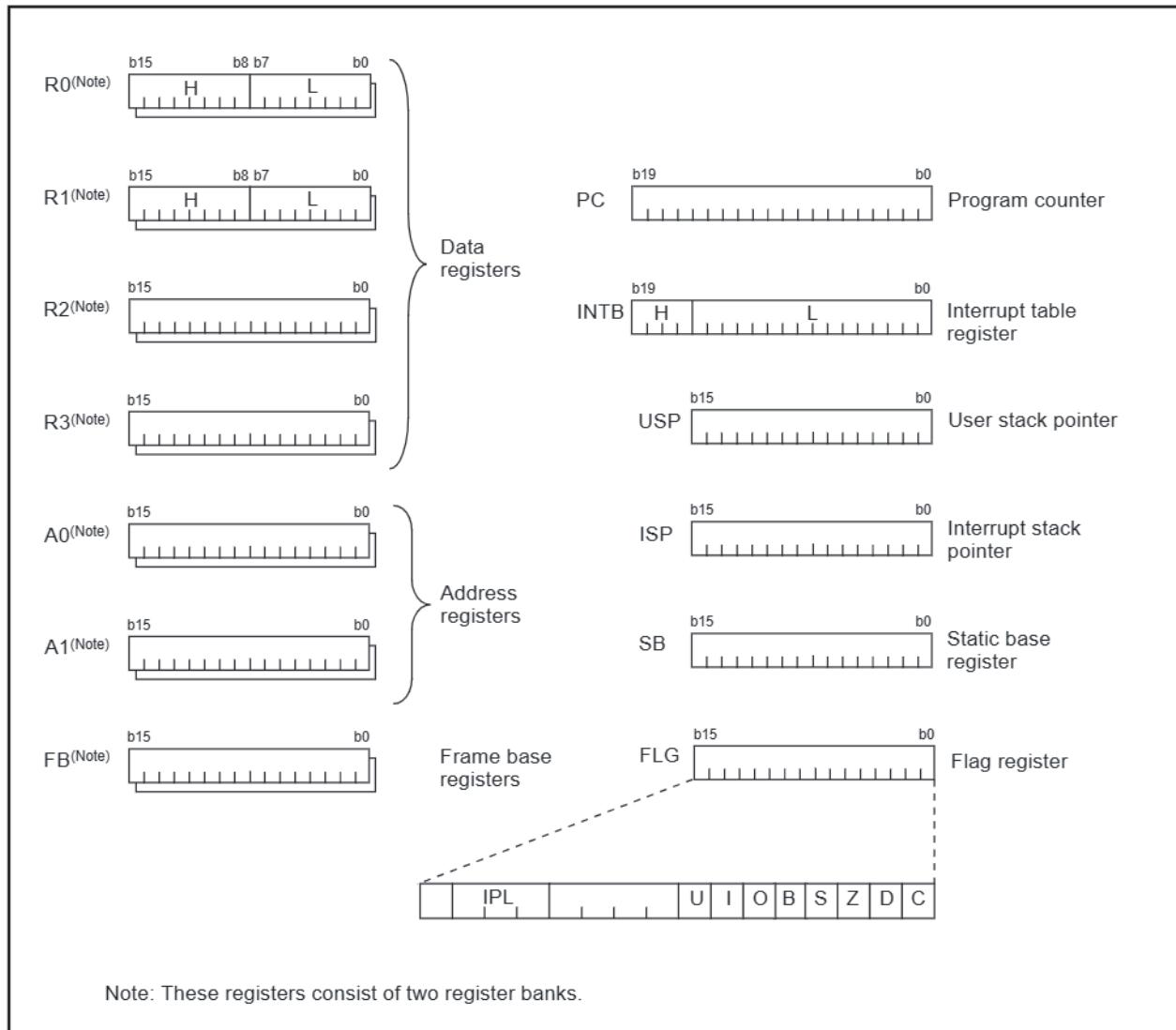

The CPU has a total of 13 registers shown in Figure 1.5.1. Seven of these registers (R0, R1, R2, R3, A0, A1, and FB) come in two sets; therefore, these have two register banks.

Figure 1.5.1. Central processing unit register

### (1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H), and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can use as 32-bit data registers (R2R0/R3R1).

### (2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data registers. These registers can also be used for address register indirect addressing and address register relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

### (3) Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

### (4) Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

### (5) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector table.

### (6) Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag). This flag is located at the position of bit 7 in the flag register (FLG).

### (7) Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

### (8) Flag register (FLG)

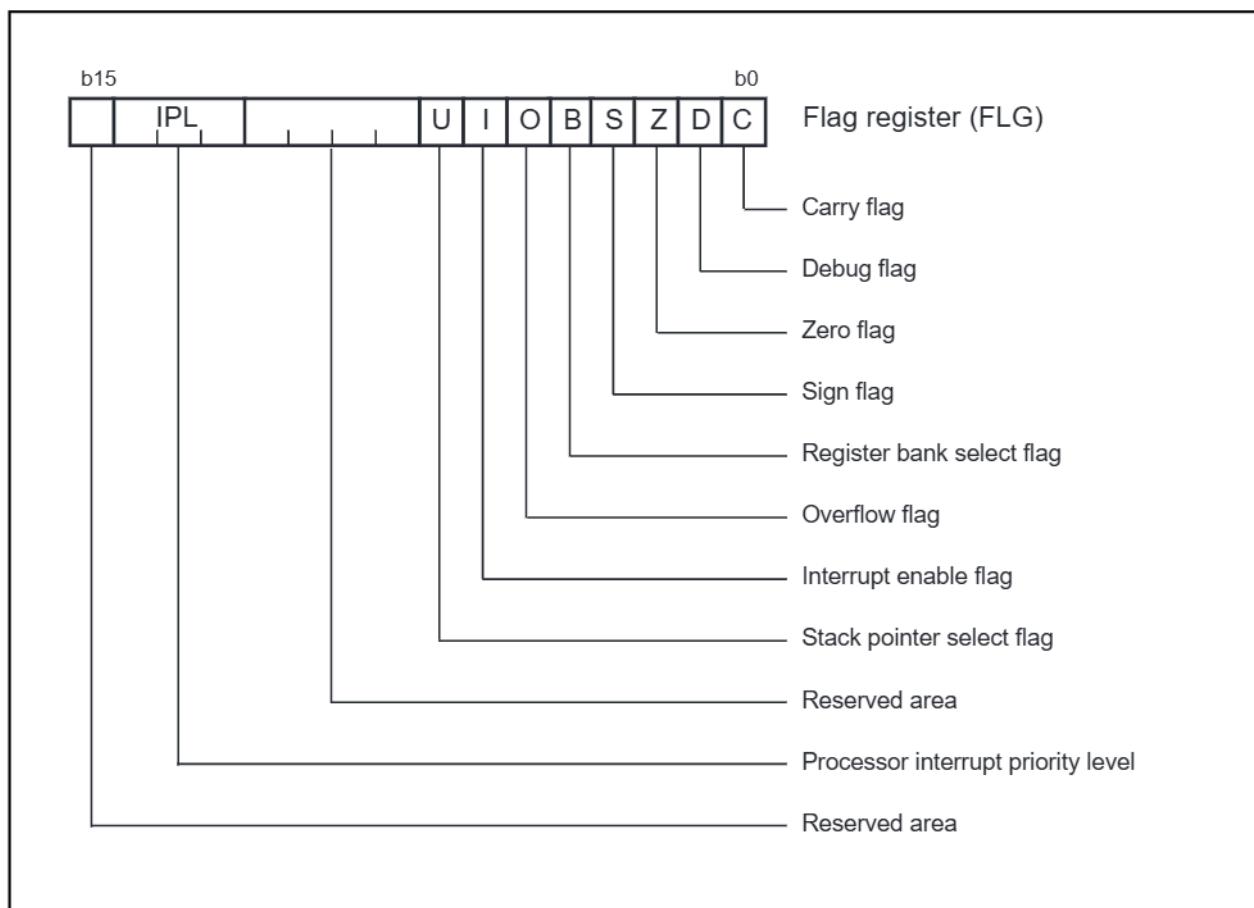

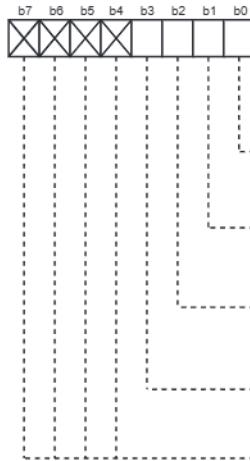

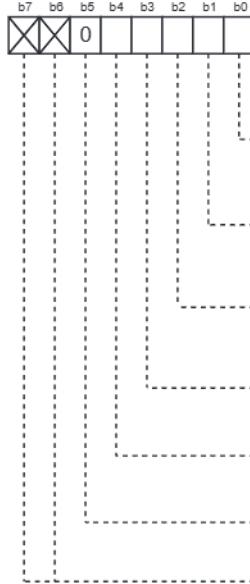

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.5.2 shows the flag register (FLG). The following explains the function of each flag:

- **Bit 0: Carry flag (C flag)**

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

- **Bit 1: Debug flag (D flag)**

This flag enables a single-step interrupt.

When this flag is “1”, a single-step interrupt is generated after instruction execution. This flag is cleared to “0” when the interrupt is acknowledged.

- **Bit 2: Zero flag (Z flag)**

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, cleared to “0”.

- **Bit 3: Sign flag (S flag)**

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, cleared to “0”.

- **Bit 4: Register bank select flag (B flag)**

This flag chooses a register bank. Register bank 0 is selected when this flag is “0”; register bank 1 is selected when this flag is “1”.

- **Bit 5: Overflow flag (O flag)**

This flag is set to “1” when an arithmetic operation resulted in overflow; otherwise, cleared to “0”.

- **Bit 6: Interrupt enable flag (I flag)**

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is “0”, and is enabled when this flag is “1”. This flag is cleared to “0” when the interrupt is acknowledged.

**• Bit 7: Stack pointer select flag (U flag)**

Interrupt stack pointer (ISP) is selected when this flag is “0” ; user stack pointer (USP) is selected when this flag is “1”.

This flag is cleared to “0” when a hardware interrupt is acknowledged or an INT instruction of software interrupt Nos. 0 to 31 is executed.

**• Bits 8 to 11: Reserved area****• Bits 12 to 14: Processor interrupt priority level (IPL)**

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is enabled.

**• Bit 15: Reserved area**

The C, Z, S, and O flags are changed when instructions are executed. See the software manual for details.

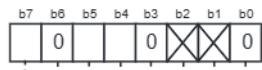

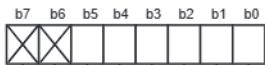

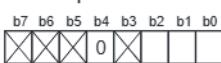

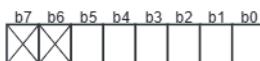

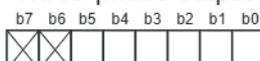

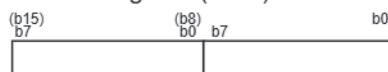

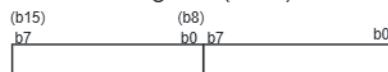

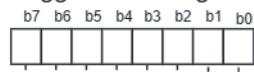

Figure 1.5.2. Flag register (FLG)

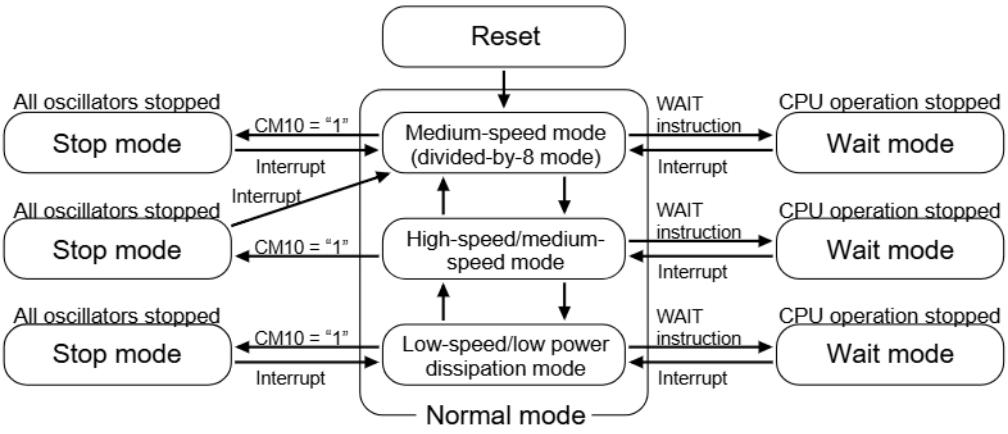

**Reset**

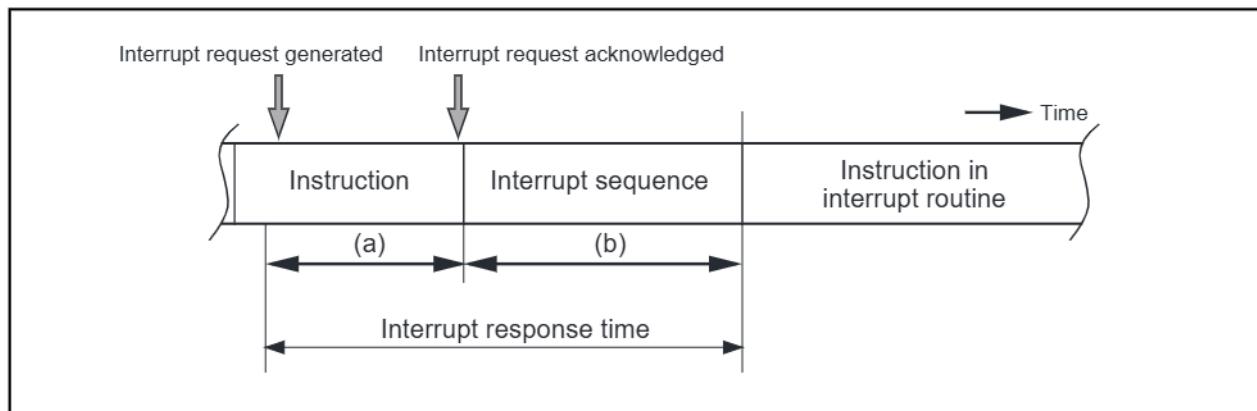

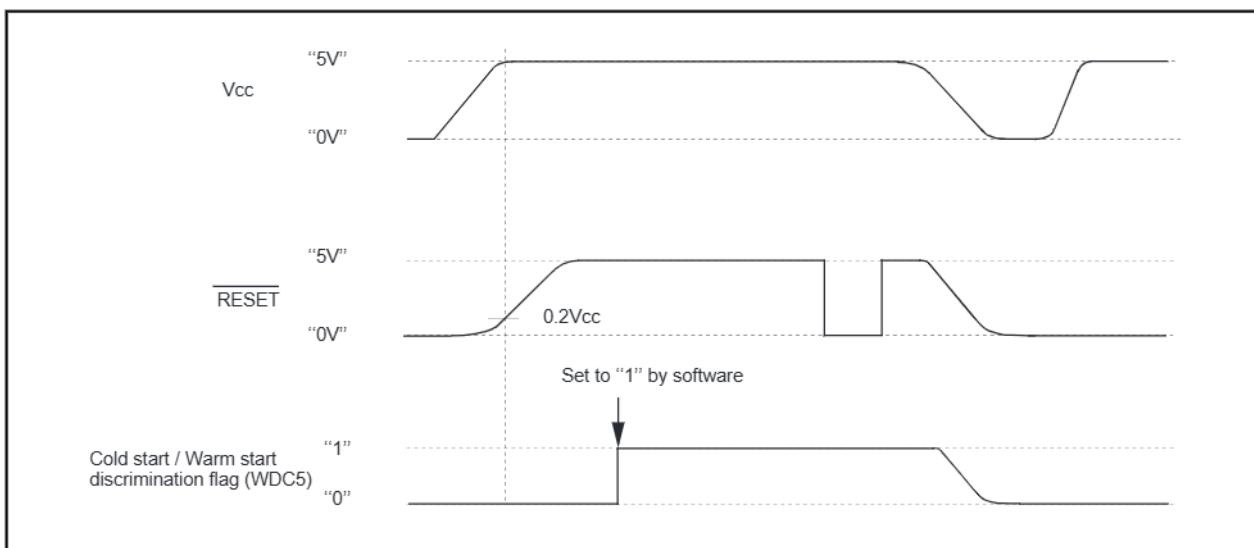

There are two kinds of resets; hardware and software. In both cases, operation is the same after the reset. (See "Software Reset" for details of software resets.) This section explains on hardware resets.

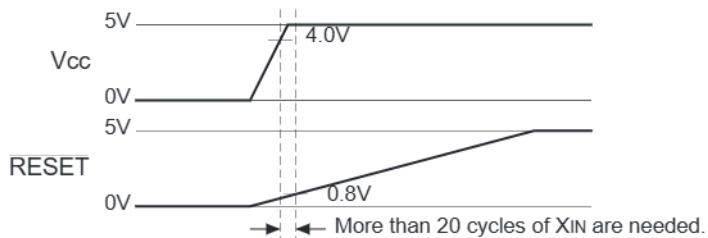

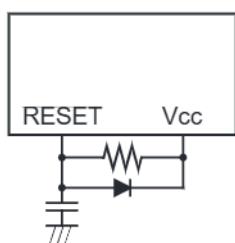

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the reset pin level "L" (0.2V<sub>CC</sub> max.) for at least 20 cycles. When the reset pin level is then returned to the "H" level while main clock is stable, the reset status is cancelled and program execution resumes from the address in the reset vector table.

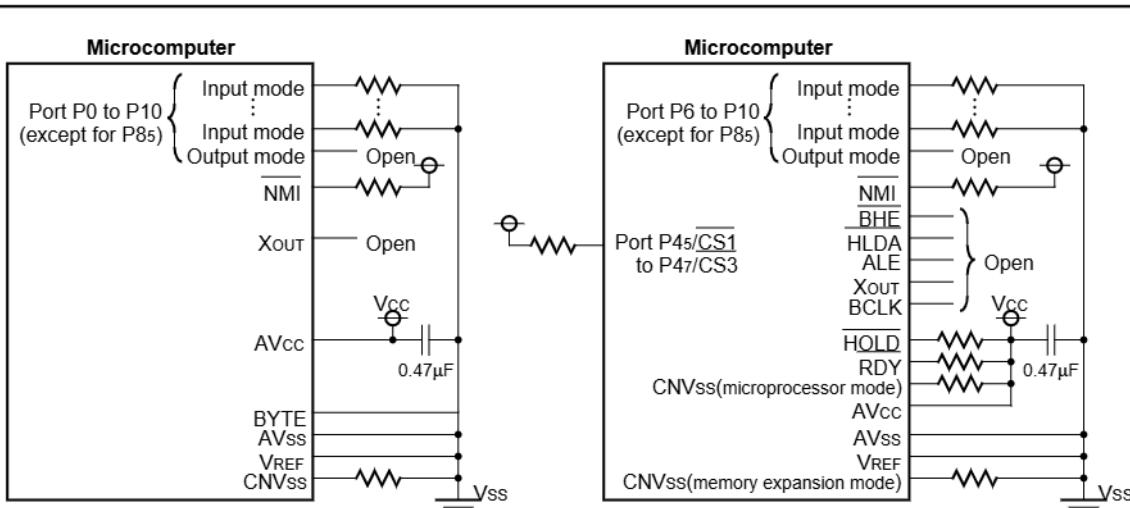

Figure 1.6.1 shows the example reset circuit. Figure 1.6.2 shows the reset sequence.

Example when V<sub>CC</sub>=5V.

Figure 1.6.1. Example reset circuit

Note 1: In M30623(80-pin package), the BYTE signal has no external pin, and is internally connected to the CNVss signal. Accordingly, in the microprocessor mode, BYTE = CNVss = V<sub>CC</sub>.

Note 2: M16C/62T group is not guaranteed to operate in memory expansion and microprocessor modes.

Note 3: M30623(80-pin package) is not provided with the chip select signals (CS0 to CS3).

Figure 1.6.2. Reset sequence

Table 1.6.1 shows the statuses of the other pins while the **RESET** pin level is “L”. Figures 1.6.3 and 1.6.4 show the internal status of the microcomputer immediately after the reset is cancelled.

**Table 1.6.1. Pin status when **RESET** pin level is “L”**

| Pin name                                 | Status                                            |                                                                     |                                                                     |

|------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

|                                          | CNVss = Vss                                       | CNVss = VCC                                                         |                                                                     |

|                                          |                                                   | BYTE = Vss (Note 1)                                                 | BYTE = VCC                                                          |

| P0                                       | Input port (floating)                             | Data input (floating)                                               | Data input (floating)                                               |

| P1                                       | Input port (floating)                             | Data input (floating)                                               | Input port (floating)                                               |

| P2, P3, P40 to P43                       | Input port (floating)                             | Address output (undefined)                                          | Address output (undefined)                                          |

| P44                                      | Input port (floating)                             | CS0 output (“H” level is output)                                    | CS0 output (“H” level is output)                                    |

| P45 to P47                               | Input port (floating)<br>(pull-up resistor is on) | Input port (floating)<br>(pull-up resistor is on)                   | Input port (floating)<br>(pull-up resistor is on)                   |

| P50                                      | Input port (floating)                             | WR output (“H” level is output)                                     | WR output (“H” level is output)                                     |

| P51                                      | Input port (floating)                             | BHE output (undefined)                                              | BHE output (undefined)                                              |

| P52                                      | Input port (floating)                             | RD output (“H” level is output)                                     | RD output (“H” level is output)                                     |

| P53                                      | Input port (floating)                             | BCLK output                                                         | BCLK output                                                         |

| P54                                      | Input port (floating)                             | HLDA output (The output value depends on the input to the HOLD pin) | HLDA output (The output value depends on the input to the HOLD pin) |

| P55                                      | Input port (floating)                             | HOLD input (floating)                                               | HOLD input (floating)                                               |

| P56                                      | Input port (floating)                             | ALE output (“L” level is output)                                    | ALE output (“L” level is output)                                    |

| P57                                      | Input port (floating)                             | RDY input (floating)                                                | RDY input (floating)                                                |

| P6, P7, P80 to P84,<br>P86, P87, P9, P10 | Input port (floating)                             | Input port (floating)                                               | Input port (floating)                                               |

Note 1: In M30623(80-pin package), the BYTE signal has no external pin, and is internally connected to the CNVss signal. Accordingly, in the microprocessor mode, BYTE = CNVss = VCC.

Note 2: In M30623(80-pin package), Port P1, P44 to P47, P72 to P75 and P91 have no external pin, and are internally the above conditions. After reset, set these ports to one of the following conditions.

- Be output mode, and output “L” level.

- Pull-up resistor is on.

|                                                         |             |                                                               |                   |                                                |             |                                                             |                 |

|---------------------------------------------------------|-------------|---------------------------------------------------------------|-------------------|------------------------------------------------|-------------|-------------------------------------------------------------|-----------------|

| (1) Processor mode register 0 (Note 1)                  | (000416)... | <table border="1"><tr><td>0018</td></tr></table>              | 0018              | (24) A-D conversion interrupt control register | (004E16)... | <table border="1"><tr><td>XXXXXX ? 0 0 0</td></tr></table>  | XXXXXX ? 0 0 0  |

| 0018                                                    |             |                                                               |                   |                                                |             |                                                             |                 |

| XXXXXX ? 0 0 0                                          |             |                                                               |                   |                                                |             |                                                             |                 |

| (2) Processor mode register 1                           | (000516)... | <table border="1"><tr><td>0 0 0 0 0 0 X X 0</td></tr></table> | 0 0 0 0 0 0 X X 0 | (25) UART2 transmit interrupt control register | (004F16)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| 0 0 0 0 0 0 X X 0                                       |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| (3) System clock control register 0                     | (000616)... | <table border="1"><tr><td>0 1 0 0 1 0 0 0</td></tr></table>   | 0 1 0 0 1 0 0 0   | (26) UART2 receive interrupt control register  | (005016)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| 0 1 0 0 1 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| (4) System clock control register 1                     | (000716)... | <table border="1"><tr><td>0 0 1 0 0 0 0 0</td></tr></table>   | 0 0 1 0 0 0 0 0   | (27) UART0 transmit interrupt control register | (005116)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| 0 0 1 0 0 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| (5) Chip select control register                        | (000816)... | <table border="1"><tr><td>0 0 0 0 0 0 0 1</td></tr></table>   | 0 0 0 0 0 0 0 1   | (28) UART0 receive interrupt control register  | (005216)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| 0 0 0 0 0 0 0 1                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| (6) Address match interrupt enable register             | (000916)... | <table border="1"><tr><td>X X X X X X 0 0</td></tr></table>   | X X X X X X 0 0   | (29) UART1 transmit interrupt control register | (005316)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| X X X X X X 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

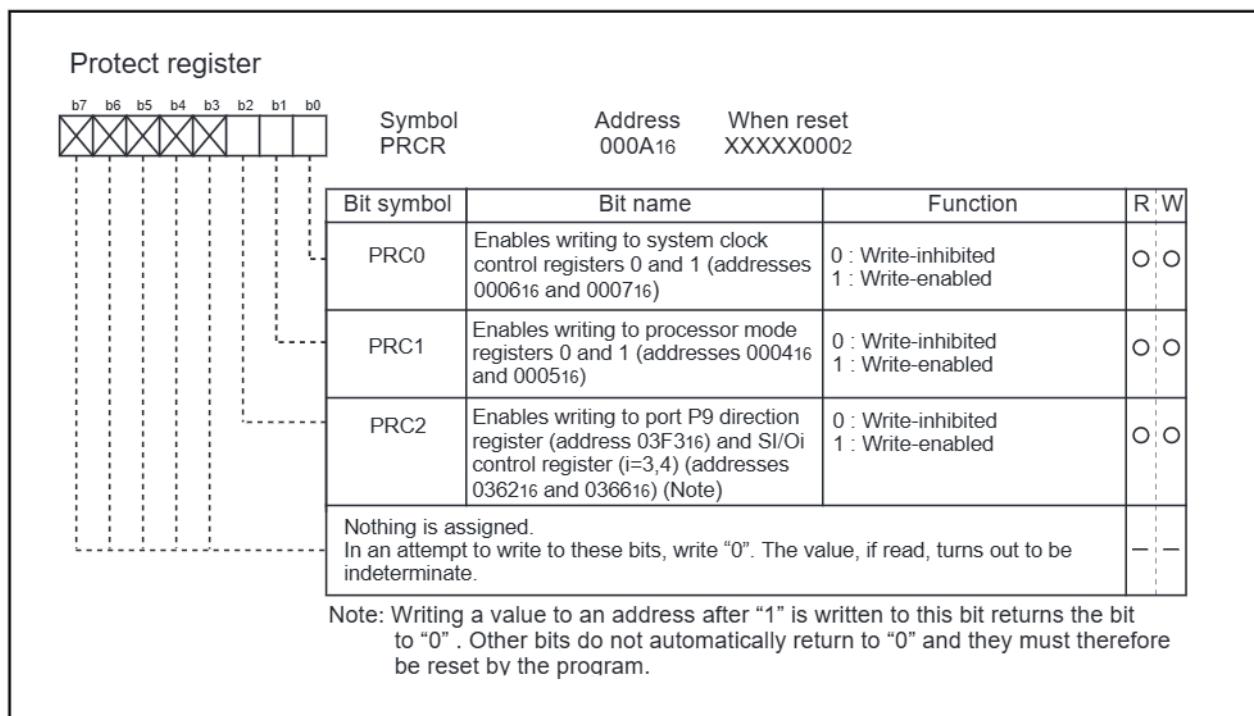

| (7) Protect register                                    | (000A16)... | <table border="1"><tr><td>X X X X \ 0 0 0</td></tr></table>   | X X X X \ 0 0 0   | (30) UART1 receive interrupt control register  | (005416)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

| X X X X \ 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

| X X X X ? 0 0 0                                         |             |                                                               |                   |                                                |             |                                                             |                 |

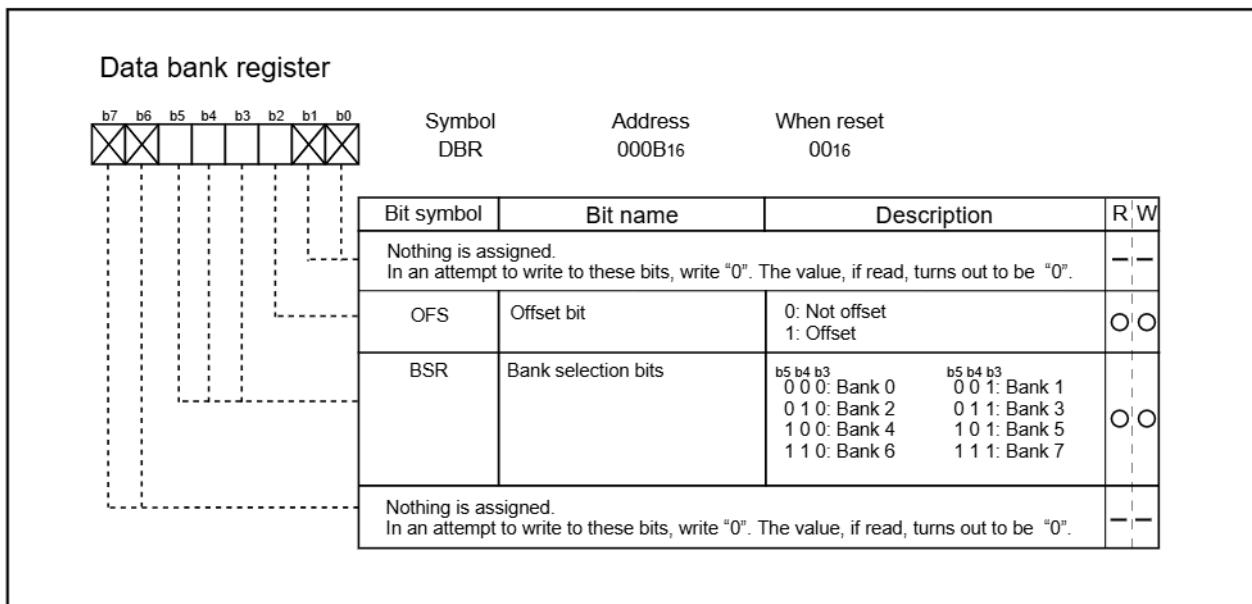

| (8) Data bank register                                  | (000B16)... | <table border="1"><tr><td>0018</td></tr></table>              | 0018              | (31) Timer A0 interrupt control register       | (005516)... | <table border="1"><tr><td>X X X X ? 0 0 0</td></tr></table> | X X X X ? 0 0 0 |

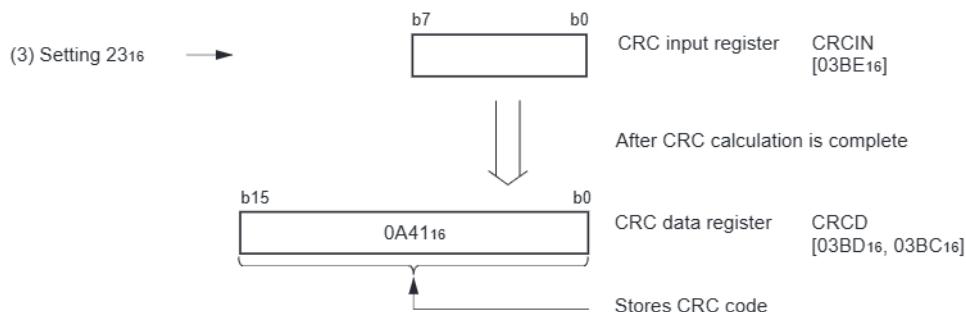

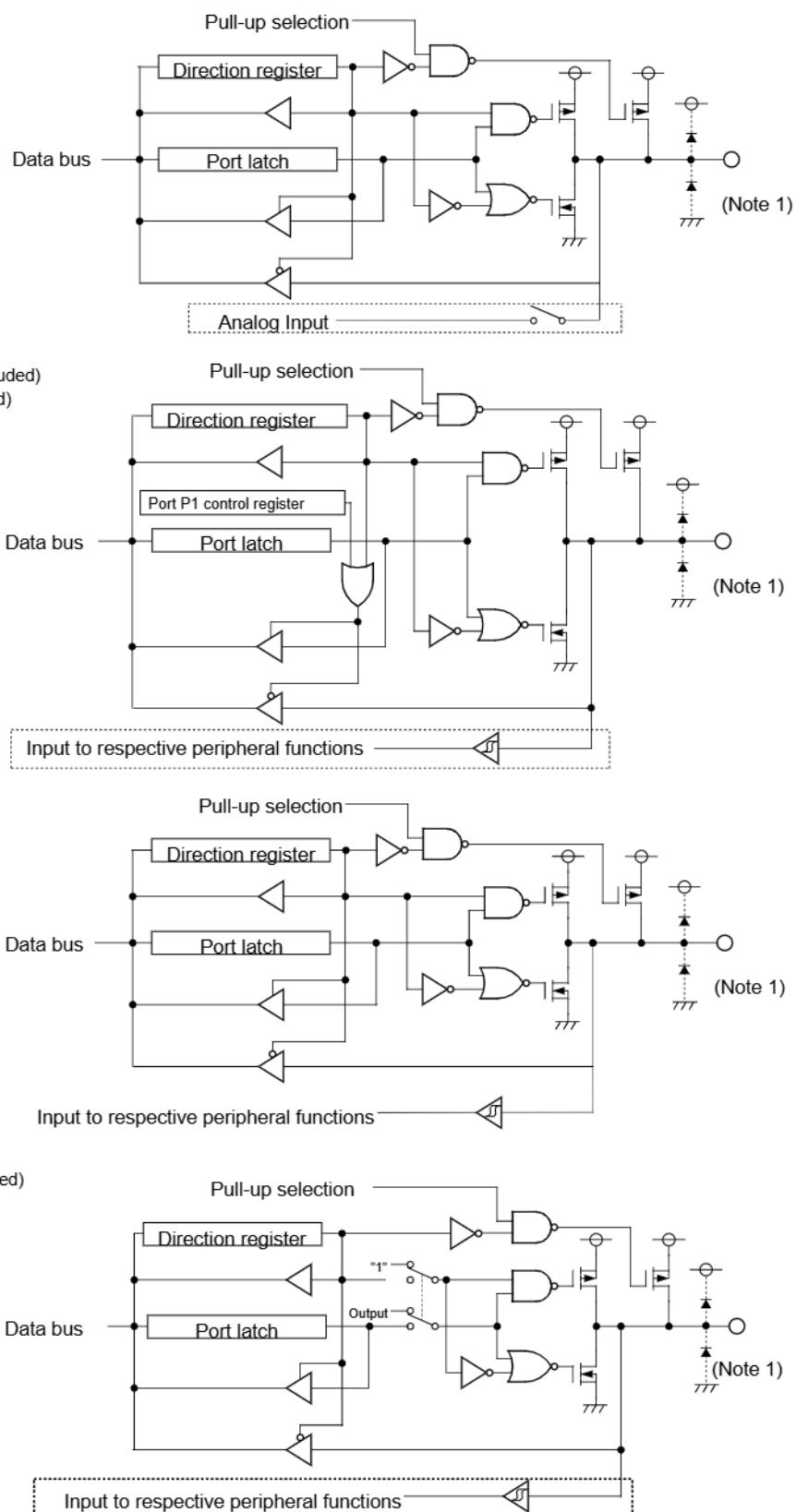

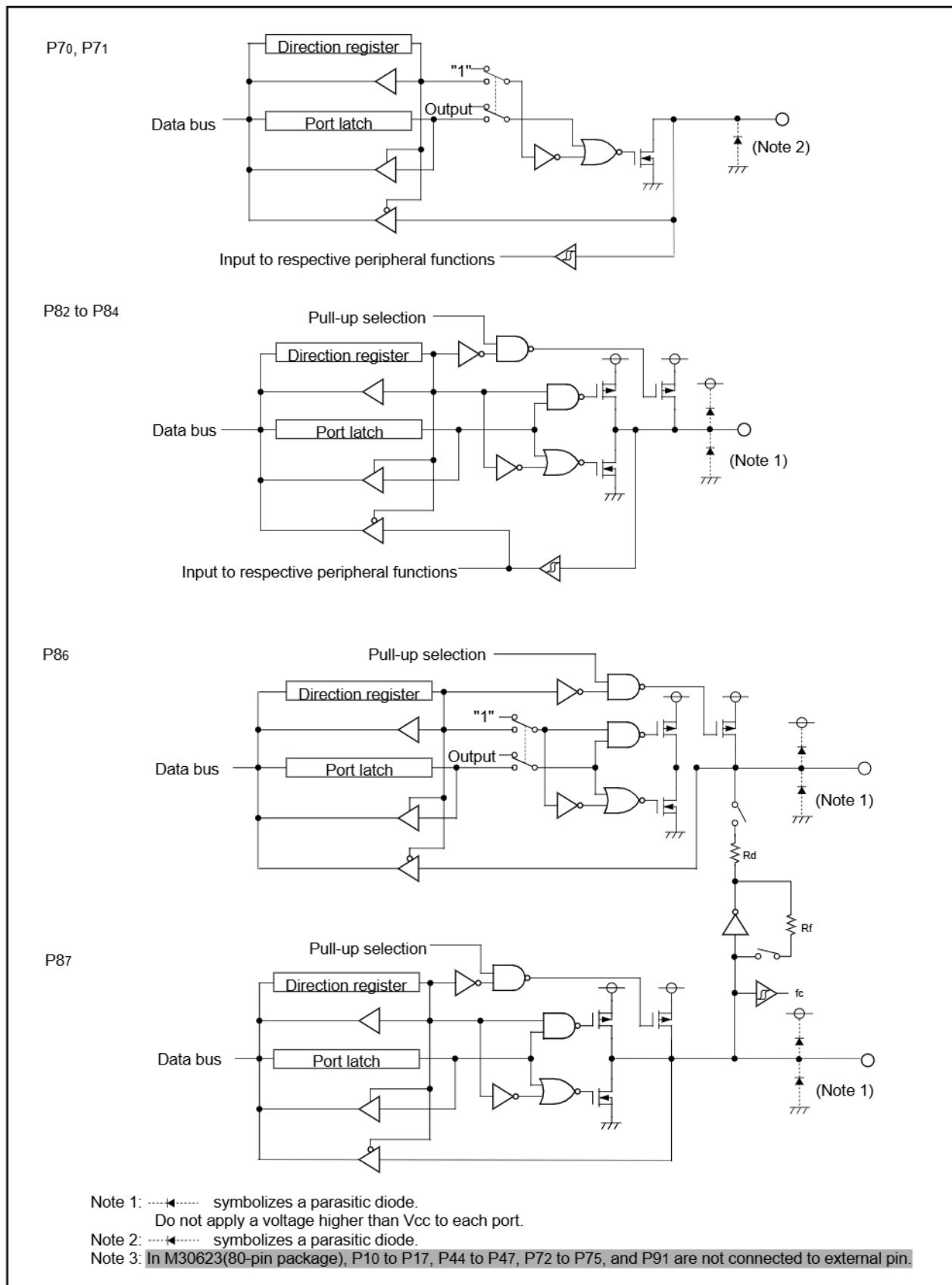

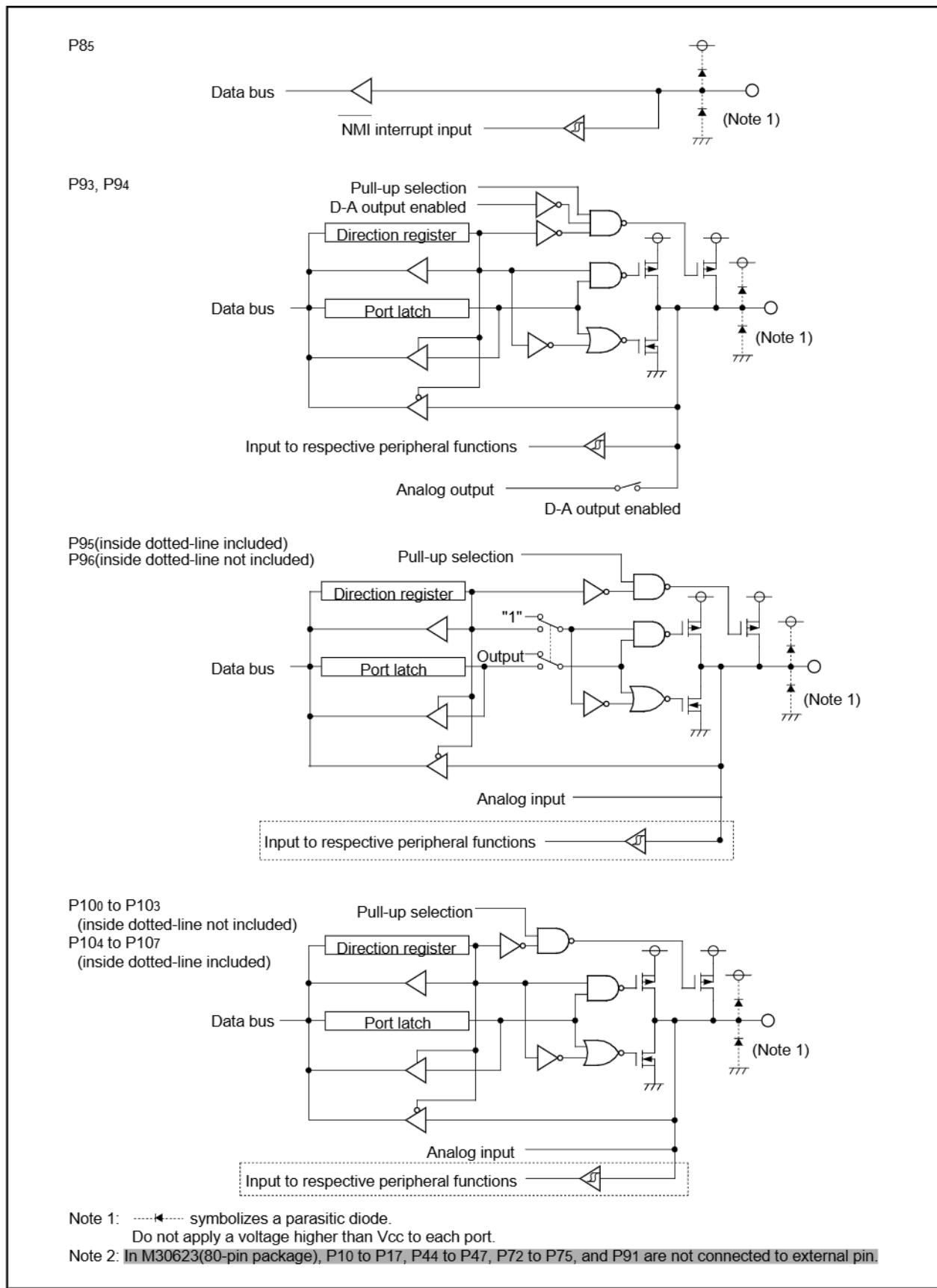

| 0018                                                    |             |                                                               |                   |                                                |             |                                                             |                 |