## 1. INTRODUCTION

## 1.1 DESCRIPTION

The TMS 9902A Asynchronous Communications Controller (ACC) is a peripheral device designed for use with the Texas Instruments 9900 family of microprocessors. The TMS 9902A is fabricated using N-channel, silicon gate, MOS technology. The TMS 9902A is TTL-compatible on all inputs and outputs, including the power supply (+5 V) and single-phase clock. This controller provides the interface between a microprocessor and a serial, asynchronous, communications channel. The ACC performs the timing and data serialization and deserialization functions, facilitating microprocessor control of the asynchronous channel. The TMS 9902A ACC accepts *EIA Standard RS-232-C* protocol.

## 1.2 KEY FEATURES

- Compatible with TMS 9900 and TMS 9995

- Low cost, serial, asychronous interface

- Programmable, five-to-eight-bit, I/O character length

- Programmable 1, 1½, and 2 stop bits

- Even, odd, or no parity

- Fully programmable data rate generation

- Interval timer with resolution from 64 to 16,320 microseconds

- TTL-compatibility, including power supply

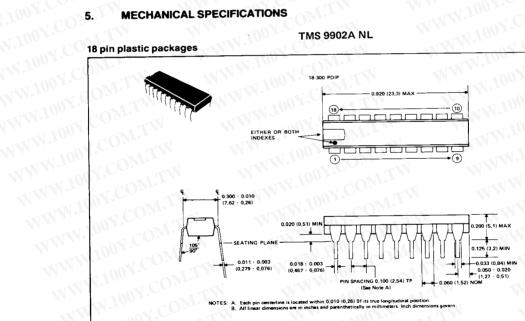

- Standard 18-pin plastic or ceramic package

- N-channel, silicon gate technology

## 1.3 TYPICAL APPLICATION

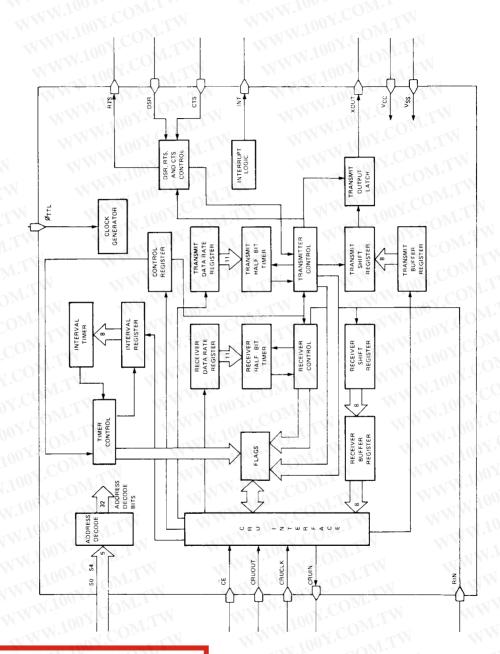

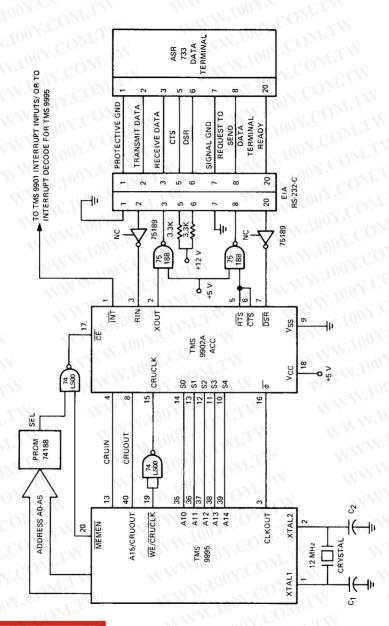

Figure 1 shows a general block diagram of a system incorporating a TMS 9902A ACC. Following is a tutorial discussion of this application. Subsequent sections of this Data Manual detail most aspects of the ACC use.

The TMS 9902A interfaces with the CPU through the <u>communications register unit</u> (CRU). The CRU interface consists of five address select lines (S0-S4), chip enable  $\overline{(CE)}$ , and three CRU lines (CRUIN, CRUOUT, CRUCLK). An additional input to the CPU is the ACC interrupt line (INT). The TMS 9902A occupies 32 bits of CRU space; each of the 32 bits are selected individually by processor address lines A10-A14, which are connected to the ACC select lines S0-S4, respectively. Chip enable  $\overline{(CE)}$  is generated by decoding address lines A0-A9 for CRU cycles. Under certain conditions the TMS 9902A causes interrupts. The interrupt logic shown in Figure 1 can be a TMS 9901.

The ACC interfaces to the asynchronous communications channel on five lines: request to send (RTS), data set ready (DSR), clear to send (CTS), serial transmit data (XOUT), and serial receive data (RIN). The request to send (RTS) goes active (LOW) whenever the transmitter is activated. However, before data transmission begins, the clear to send (CTS) input must be active. The data set ready (DSR) input does not affect the receiver or transmitter. When DSR or CTS changes level, an interrupt is generated.

特力材料886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw ADDRESS BUS A0-A14 A10-A14 S0-S4 DATA 9902 SELECT CONTRO SERIAL TMS 9902A LOGIC TMS 9900 LEVEL ASYNCHRONOUS ASYNCHRONOUS MICROPROCESSO INTERFACE COMMUNICATIONS CENTRAL CRU CONTROLLER PROCESSING UNIT (CPU) TIM 9904 -3TTL CLOCK GENERATOR

FIGURE 1. TYPICAL APPLICATION, TMS 9902A ASYNCHRONOUS COMMUNICATION CONTROLLER (ACC)

LOGIC

INTERRUPT INTERFACE

## 2. ARCHITECTURE

The controller is designed to provide a low cost, serial, asynchronous interface to the 9900 family of microprocessor. The TMS 9902A ACC, diagrammed in Figure 2, has five main subsections: CRU interface, transmitter section receiver section, interval timer, and interrupt section.

## 2.1 CRU INTERFACE

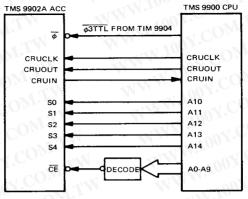

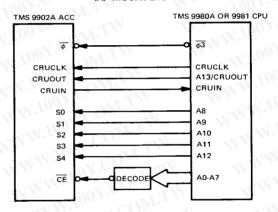

The CRU is the means by which the CPU communicates with the TMS 9902A ACC. The ACC occupies 32 bits CRU read and write space. Figure 3 illustrates CRU interfaces between a TMS 9902A and 9900, 9981 and 990 CRU's. The CRU lines are tied directly to each other as shown. The least significant bits of the address bus a connected to the select lines. In a TMS 9900 CPU system A14-A10 are connected to S4-S0 respectively. The most significant address bits are decoded to select the TMS 9902A via the chip enable (CE) signal. When CE is inactive (HIGH), the CRU interface of the 9902A is disabled.

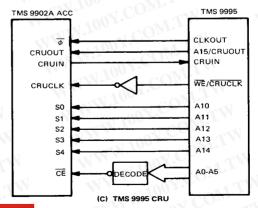

Figure 3(c) illustrates a TMS 9995 CRU interface. The WE/CRUCLK line from the 9995 needs to be inverted the 9902A. The A10-A14 lines are connected to S0-S4 respectively on the 9902. Selection of the 9902 is possible utilizing the A0-A5 lines in conjunction with the MEMEN line.

## NOTE

When  $\overline{CE}$  is inactive (HIGH) the 9902A sets its CRUIN pin to high impedance and disables CRUCLK from coming on chip. This means the CRUIN line can be used as an OR-tied bus. The 9902A is still able to see the select lines even when  $\overline{CE}$  is high.

For those unfamiliar with the CRU concept, the following is a discussion of how to build a CRU interface. The CF is a bit addressable, synchronous, serial interface over which a single instruction can transfer between one and bits serially. Each one of the bits of the CRU space has a unique address and can be read and written to. Duri multi-bit CRU transfers, the CRU address is incremented at the beginning of each CRU cycle to point to the near

3

## (A) TMS 9900 CRU

## (B) TMS 9981 CRU

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

FIGURE 3 - TMS 9902A CRU INTERFACES

^

When a TMS 9900 series CPU executes a CRU Instruction, the processor uses the contents of Workspace Register 12 as a base address. (Refer to the 9900 Microprocessor Data Manual for a complete discussion on how CRU addresses are derived.) The CRU address is brought out on the 15-bit address bus; this means that the least significant bit of R12 is not brought out of the CPU. During CRU cycles, the memory control lines (MEMEN, WE, and DBIN) are all inactive; MEMEN being inactive (HIGH) indicates the address is not a memory address and therefore is a CRU address or external instruction code. Also, when MEMEN is inactive (HIGH) and a valid address is present, address bits A0-A2 must all be zero to constitute a valid CRU address. If address bits A0-A2 are other than all zeroes, they are indicating an external instruction code. In summary, address bits A3-A14 contain the CRU address to be decoded; address bits A0-A2 must be zero; and MEMEN must be inactive (HIGH) to indicate a CRU cycle.

## 2.1.1 CPU Output For CRU

The TMS 9902A ACC occupies 32 bits of output CRU space, of which 23 bits are used: 31 and 21-0. These 23 bits are employed by the CPU to communicate command and control information to the TMS 9902A. Table 1 shows the mapping between CRU address select (S lines) and ACC functions. Each CRU addressable output bit on the ACC is described in detail following Table 1.

TABLE 1

TMS 9902A ACC OUTPUT SELECT BIT ASSIGNMENTS

| ADDRESS <sub>2</sub> |      |     |    | ADDRESS | 21000                 | DESCRIPTION |                                                                                        |  |  |

|----------------------|------|-----|----|---------|-----------------------|-------------|----------------------------------------------------------------------------------------|--|--|

| S0 S1 S2             |      | S2  | S3 | S4      | ADDRESS <sub>10</sub> | NAME        | DESCRIPTION                                                                            |  |  |

| al.                  | 1    | 1   | -1 | 1       | 31                    | RESET       | Reset device                                                                           |  |  |

|                      |      |     |    |         | 30-22                 | 1.7         | Not used                                                                               |  |  |

| 1                    | 0    | 1   | 0  | 1       | 21                    | DSCENB      | Data Set Status Change Interrupt Enable                                                |  |  |

| 1                    | 0    | 1   | 0  | 0       | 20                    | TIMENB      | Timer Interrupt Enable                                                                 |  |  |

| 1                    | 0    | 0   | 1  | -10     | 19                    | XBIENB      | Transmitter Interrupt Enable                                                           |  |  |

| 1                    | 0    | 0   | 1  | 0       | 18                    | RIENB       | Receiver Interrupt Enable                                                              |  |  |

| 1                    | 0    | 0   | 0  | 1       | 17                    | BRKON       | Break On                                                                               |  |  |

| 1                    | 0    | 0   | 0  | 0       | 16                    | RTSON       | Request to Send On                                                                     |  |  |

| 0                    | 1    | . 1 | 1  | 1       | 15                    | TSTMD       | Test Mode                                                                              |  |  |

| 0                    | 1    | 1   | 1  | 0       | 14                    | LDCTRL      | Load Control Register                                                                  |  |  |

| 0                    | 1    | 1   | 0  | 1       | 13                    | LDIR        | Load Interval Register                                                                 |  |  |

| 0                    | . 10 | 1   | 0  | 0       | 12                    | LRDR        | Load Receiver Data Rate Register                                                       |  |  |

| 0                    | 1    | 0   | 1  | 1       | 11                    | LXDR        | Load Transmit Data Rate Register                                                       |  |  |

|                      |      |     |    |         | 10-0                  | Y.CO.       | Control, Interval, Receive Data Rate, Transmit Data Rate and Transmit Buffer Registers |  |  |

Bit 31 (RESET) --

Reset. Writing a one or zero to bit 31 causes the device to reset, consequently disabling all interrupts, initializing the transmitter and receiver, setting  $\overline{RTS}$  inactive (HIGH), setting all register load control flags (LDCTRL, LDIR, LRDR, and LXDR) to a logic one level, and resetting the BREAK flag. No other input or output operations should be performed for  $11 \, \overline{\phi}$  clock cycles after issuing the RESET command.

Bit 30-Bit 22 -

Not used.

| INTERRUPT<br>ENABLE | SELECT<br>BIT | INTERRUPT<br>FLAG | INTERRUPT<br>ENABLED |

|---------------------|---------------|-------------------|----------------------|

| DSCENB              | 21            | DSCH              | DSCINT               |

| TIMENB              | 20            | TIMELP            | TIMINT               |

| XIENB               | 19            | XBRE              | XINT                 |

| RIENB               | 18            | RBRL              | RINT                 |

| Bit 21 (DSCENB) — | Data Set Change Interrupt Enable. Writing a one to bit 21 causes the INT out put to be active (LOW) whenever DSCH (Data Set Status Change) is a logic one Writing a zero to bit 21 causes DSCH interrupts to be disabled. Writing either one or zero to bit 21 causes DSCH to reset. (Refer also to Section 2.5.)                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 20 (TIMENB) — | Timer Interrupt Enable. Writing a one to bit 20 causes the INT output to be active whenever TIMELP (Timer Elapsed) is a logic one. Writing a zero to bit 20 causes TIMELP interrupts to be disabled. Writing either a one or zero to bit 20 causes TIMELP and TIMERR (Timer Error) to reset. (Refer also to Section 2.4 and 2.5.)                                                                     |

| Bit 19 (XBIENB) — | Transmit Buffer Interrupt Enable. Writing a one to bit 19 causes the INT outpu to be active whenever XBRE (Transmit Buffer Register Empty) is a logic one Writing a zero to bit 19 causes XBRE interrupts to be disabled. The state o XBRE is not affected by writing to bit 19. (Refer also to Sections 2.2 and 2.5.                                                                                 |

| Bit 18 (RIENB) —  | Receiver Interrupt Enable. Writing a one to bit 18 causes the INT output to b active whenever RBRL (Receiver Buffer Register Loaded) is a logic one. Writin a zero to bit 18 disables RBRL interrupts. Writing either a one or zero to bit 18 causes RBRL to reset. (Refer also to Sections 2.3 and 2.5.)                                                                                             |

| Bit 17 (BRKON) —  | Break On. Writing a one to bit 17 causes the XOUT (Transmitter Serial Dat Output) to go to a logic zero whenever the transmitter is active and the Transmi Buffer Register (SBR) and the Transmit Shift Register (XSR) are empty. Whill BRKON is set, loading of characters into the XBR is inhibited. Writing a zero to bit 17 causes BRKON to reset and the transmitter to resume normal operation. |

| Bit 16 (RTSON) —  | Request To Send On. Writing a one to bit 16 causes the RTS output to be activ (LOW). Writing a zero to bit 16 causes RTS to go to a logic one after the XSI (Transmit Shift Register) and XBR (Transmit Buffer Register) are empty, an BRKON is reset. Thus, the RTS output does not become inactive (HIGH) unt                                                                                       |

and the Interval Timer to operate 32 times its normal rate. Writing a zero to b 15 re-enables normal device operation. There seldom is reason to enter the termode under normal circumstances, but this function is useful for diagnostic an inspection purposes.

Test Mode. Writing a one to bit 15 causes RTS to be internally connected t

CTS, XOUT to be internally connected to RIN, DSR to be internally held LOW

Register Load Control Flags. Output bits 14-11 determine which of the fivergisters are loaded when writing to bits 10-0. The flags are prioritized as show in Table 2.

TABLE 2

TMS 9902A ACC REGISTER LOAD SELECTION

after character transmission is completed.

| COMITW | REGISTER LOAD CONTROL FLAG STATUS |         |       |                               |  |  |  |

|--------|-----------------------------------|---------|-------|-------------------------------|--|--|--|

| LDCTRL | LDIR                              | LRDR    | LXDR  | W 100                         |  |  |  |

| COM    | ×                                 | ×       | CU x  | Control Register              |  |  |  |

| o T    | 1                                 | ×1003   | ×     | Interval Register             |  |  |  |

| 0      | 0                                 |         | 7 C X | Receive Data Rate Register *  |  |  |  |

| do o   | 0                                 | X x 100 | 1.17  | Transmit Data Rate Register * |  |  |  |

| 0      | 0                                 | 0       | 0     | Transmit Buffer Register      |  |  |  |

<sup>•</sup> If both LRDR and LXDR bits are set, both registers are loaded, assuming LDCTRL and LDIR are disabled; if only one of the registers is to be loaded, only that register bit is set, and the other register bit reset.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Bit 15 (TSTMD)

Bits 14-11 -

Bit 14 (LDCTRL) -

Load Control Register, Writing a one to bit 14 causes LDCTRL to be set to a logic one. When LDCTRL = 1, any data written to bits 0-7 is directed to the Control Register. Note that LDCTRL is also set to a logic one when a one or zero is written to bit 31 (RESET). Writing a zero to bit 14 causes LDCTRL to

zero is written to bit 31 (RESET). Writing a zero to bit 14 causes LDCTRL to reset to a logic zero, disabling loading of the Control Register. LDCTRL is also automatically reset to logic zero when a datum is written to bit 7 of the Control Register. Reset normally occurs as the last bit is written when loading the

Control Register with a LDCR instruction.

Bit 13 (LDIR) -

Load Interval Register. Writing a one to bit 13 causes LDIR to set to a logic one. When LDIR = 1 and LDCTRL = 0, any data written to bits 0-7 is directed to the Interval Register. Note that LDIR is also set to a logic one when a datum is written to bit 31 (RESET); however, Interval Register loading is not enabled

until LDCTRL is set to a logic zero. Writing a zero to bit 13 causes LDIR to be reset to logic zero, disabling loading of the Interval Register. LDIR is also automatically reset to logic zero when a datum is written to bit 7 of the Interval Register. Reset normally occurs as the last bit is written when loading the Interval Register with a LDCR instruction.

Bit 12 (LRDR) -

Register. Reset normally occurs as the last bit is written when loading the Interval Register with a LDCR instruction.

Load Receive Data Rate Register. Writing a one to bit 12 causes LRDR to set to a logic one. When LRDR = 1, LDIR = 0, and LDCTRL = 0. Any data written to

bits 0-10 is directed to the Receive Data Rate Register. Note that LRDR is also set to a logic one when a datum is written to bit 31 (RESET); however, Receive Data Rate Register loading is not enabled until LDCTRL and LDIR are set to a logic zero. Writing a zero bit to 12 causes LRDR to reset to a logic zero, disabling loading of the Receive Data Rate Register. LRDR is also automatically reset to logic zero when a datum is written to bit 10 of the Receive Data Rate Register. Reset normally occurs as the last bit is written when loading the Receive Data Rate Register with a LDCR instruction.

Bit 11 (LXDR) -

Load Transmit Data Rate Register. Writing a one to bit 11 causes LXDR to set to a logic one. When LXDR = 1, LDIR = 0, and LDCTRL = 0, any data written to bits 0-10 is directed to the Transmit Data Rate Register. Note that loading of both the Receive and Transmit Data Rate Registers is enabled when LDCTRL = 0, LDIR = 0, LRDR = 1, and LXDR = 1; thus these two registers may be loaded simultaneously when data is received and transmitted at the same rate. LXDR is also set to a logic one when a datum is written to bit 31 (RESET); however, Transmit Data Rate Register loading is not enabled until LDCTRL and LDIR are at logic zero. Writing a zero to bit 11 causes LXDR to reset to logic zero, consequently disabling loading of the Transmit Data Rate Register. Since bit 11 is the next bit addressed after loading the Transmit Data Rate Register, the register may be loaded and the LXDR flag reset with a single LDCR instruction in which 12 bits (Bits 0-11) are written and zero written to Bit 11.

Bits 14-11 (All Zeroes) —

Bits 10-0 (Data) —

Load Transmit Buffer Register. See Section 2.1.2.5.

Data. Information written to bits 10-0 is loaded into the controlling registers as indicated by LDCTRL, LDIR, LRDR, and LXDR (see Table 2). The different register bits are described in Section 2.1.2 below.

## 2.1.2 Registers

## 2.1.2.1 Control Register

The Control Register is loaded to select character length, device clock operation, parity, and the number of stop bits for the transmitter; control register loading occurs when LDCTRL is active (see Table 2). Table 3 shows the bit address assignments for the Control Register.

TABLE 3

CONTROL REGISTER BIT ADDRESS ASSIGNMENTS

| AD       | DRESS <sub>10</sub> | W    | NAME  | 1003              | DESCRIPTION  Stop Bit Select |                 |       |  |  |

|----------|---------------------|------|-------|-------------------|------------------------------|-----------------|-------|--|--|

| VIV. 100 | 7                   | - 1  | SBS1  | 11.10             |                              |                 |       |  |  |

|          | 6                   | TW   | SBS2  | 100               |                              |                 |       |  |  |

|          | 5                   |      | PENB  | 111               | Parity Enabl                 | le              |       |  |  |

|          | - 177               | PODD | 14.   | Odd Parity Select |                              |                 |       |  |  |

|          | 3                   | 1.1  | CLK4M | -x17\\.\\.\\      | φ Input Divi                 | de Select       |       |  |  |

|          | 2                   |      | = 1   |                   | Not Used                     |                 |       |  |  |

|          | 11                  | M. I | RCL1  | - TON.            | Cha                          | racter Length S | alaat |  |  |

|          | 0                   | TV2  | RCL0  |                   | Total Circ                   | racter Length o |       |  |  |

| 7        | 6 (                 | 5    | 4     | 3                 | 2                            | 1 7             | 0     |  |  |

| SBS1     | SBS2                | PENB | PODD  | CLK4M             | NOT USED                     | RCL1            | RCLO  |  |  |

MSB

Bits 7 and 6

(SBS1 and SBS2) -

Stop Bit Selection. The number of stop bits to be appended to each transmitte character is selected by bits 7 and 6 of the Control Register as shown below. The receiver only tests for a single stop bit, regardless of the status or bits 7 and 6

LSB

STOP BIT SELECTION

| SBS1<br>BIT 7 | SBS2<br>BIT 6 | NUMBER OF TRANSMITTED<br>STOP BITS |

|---------------|---------------|------------------------------------|

| 0             | 0             | 1%                                 |

| 0             | 100           | 2                                  |

| 1             | 0-0           | 1, 1                               |

| 1             |               | LM ANN TOOK                        |

Bits 5 and 4 (PENB and PODD) –

Parity Selection. The type of parity generated for transmission and detected for reception is selected by bits 5 and 4 of the Control Register as shown below When parity is enabled (PENB = 1), the parity bit is transmitted and received in addition to the number of bits selected for the character length. Odd parity is such that the total number of ones in the character and parity bit, exclusive of stop bit(s), are odd. For even parity, the total number of ones are even.

## PARITY SELECTION

| W   | PENB<br>BIT 5 | PODD<br>BIT 4 | PARITY |

|-----|---------------|---------------|--------|

| -43 | 0             | M. To COM     | None   |

| LIN | 0             | 1001          | None   |

|     | 1             | O CO          | Even   |

|     | 1             | 100           | Odd    |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www. 100y. com. tw

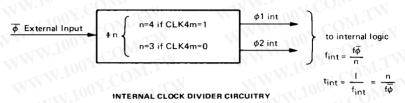

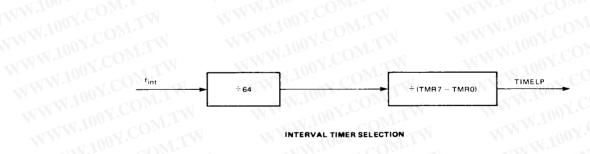

$\phi$  Input Divide Select. The  $\phi$  input to the ACC is used to generate internal dynamic logic clocking and to establish the time base for the Interval Timer Transmitter, and Receiver. The  $\overline{\phi}$  input is internally divided by either 3 or 4 to generate the two-phase internal clocks required for MOS logic, and to establish the basic internal operating frequency (f<sub>int</sub>) and internal clock period (t<sub>int</sub>). When bit 3 of the Control Register is set to a logic one (CLK4M = 1),  $\overline{\phi}$  is internally divided by 4, and when CLK4M = 0,  $\overline{\phi}$  is divided by 3. For example, when  $\overline{\phi}$  = 3 MHz, as in a standard 3 MHz TMS 9900 system, and CLK4M = 0,  $\overline{\phi}$  is internally divided by 3 to generate an internal clock period t<sub>int</sub> of 1 μs. Th figure below shows the operation of the internal clock divider circuitry. The internal clock frequency should be no greater than 1.1 MHz; thus, when  $\overline{\phi}$  > 3.3 MHz, CLK4M should be set to a logic one.

NOTE: fo denotes frequency of o.

Bits 1 and 0 (RCL1 and RCL0) —

Character Length Select. The number of data bits in each transmitted and received character is determined by bits 1 and 0 of the Control Register as shown below:

#### CHARACTER LENGTH SELECTION

| RCL1<br>BIT 1 | RCL0<br>BIT 0 | CHARACTER<br>LENGTH |

|---------------|---------------|---------------------|

| 0             | 0             | 5 Bits              |

| 0             | CON           | 6 Bits              |

| 1             | 1001.0        | 7 Bits              |

| 1 1           | N. T. CON.    | 8 Bits              |

## 2,1,2,2 Interval Register

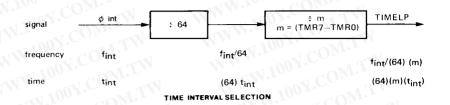

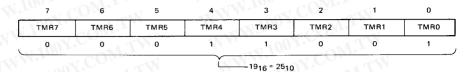

The Interval Register is enabled for loading when LDCTRL = 0 and LDIR = 1 (see Table 2). The Interval Register i used to select the rate at which interrupts are generated by the TMS 9902A Interval Timer. The figure below show the bit assignments for the Interval Register when enabling for loading.

| 7    | 6    | 5    | 4       | 3    | 2       | 1    | 0    |

|------|------|------|---------|------|---------|------|------|

| TMR7 | TMR6 | TMR5 | TMR4    | TMR3 | TMR2    | TMR1 | TMRO |

| MSB  |      |      | -<1 10U | Mo   | . I. d. | 44   | LSB  |

INTERVAL REGISTER BIT ADDRESS ASSIGNMENTS

The figure below illustrates the establishment of the interval for the Interval Timer. For example, if the Interval Register is loaded with a value of  $80_{16}$  ( $128_{10}$ ) the interval at which Timer Interrupts are generated is  $t_{itv}$   $t_{int} \cdot 64 \cdot M = (1 \ \mu s)$  (64) (128) = 8.192 ms when  $t_{int} = 1 \ \mu s$ .  $t_{int} = n/f \phi$  where n = 4 if CLK4M = 1, 3 if CLK4M =

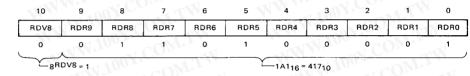

## 2.1.2.3 Receive Data Rate Register

The Receive Data Rate Register (RDR) is enabled for loading when LDCTRL = 0, LDIR = 0, and LRDR = 1 (see Table 2). The Receive Data Rate Register is used to select the bit rate at which data is received. The diagram show the bit address assignments for the Receive Data Rate Register when enabled for loading.

| 10   | 9    | 8     | C 2 72 | 6    | 5    | 4    | 3    | 2      | OP <sub>1</sub> | 0    |

|------|------|-------|--------|------|------|------|------|--------|-----------------|------|

| RDV8 | RDR9 | RDR8  | RDR7   | RDR6 | RDR5 | RDR4 | RDR3 | RDR2   | RDR1            | RDR0 |

| MSB  | M VV | - 400 |        | TV   | N    |      | -1   | 100 x. |                 | LSB  |

#### RECEIVE DATA RATE REGISTER RIT ADDRESS ASSIGNMENTS

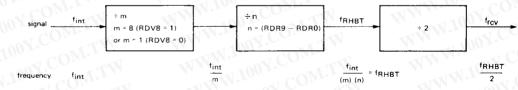

The diagram below illustrates the manner in which the receive data rate is established. Basically, two programmab counters are used to determine the interval for half the bit period of receive data. The first counter divides the interval system clock frequency (f<sub>int</sub>) by either 8 (RDV8 = 1) or 1 (RDV8 = 0). The second counter has ten stages are may be programmed to divide its input signal by any value from 1 (RDR9 — RDR0 = 0000000001) to 1023 (RDR — RDR0 = 1111111111). The frequency of the output of the second counter (f<sub>rhbt</sub>) is double the receive-data rat For example, assume the Receive Data Rate Register is loaded with a value of 11000111000; RDV8 = 1, and RDR — RDR0 = 1000111000 = 23816 = 56810. Thus, for f<sub>int</sub> = 1 MHz, (see Control Register, bit 3) the receive data rate in the second counter of the second counter of

## RECEIVE DATA RATE SELECTION

Quantitatively, the receive-data rate fRCV is described by the following algebraic expression:

$= f_{rcv} = [(1 \times 10^6 \div 8) \div 568] \div 2 = 110.04 \text{ bits per second.}$

$$f_{rcv} = \frac{f_{RHBT}}{2} = \frac{f_{int}}{(2) (m) (n)} = \frac{f_{int}}{(2) (8RDV8) (RDR9 - RDR0)}$$

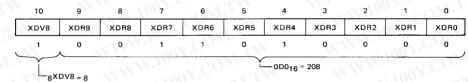

#### 2.1.2.4 Transmit Data Rate Register

The Transmit Data Rate Register (XDR) is enabled for loading when LDCTRL = 0, LDIR = 0, and LXDR = 1 (see Table 2). The Transmit Data Rate Register is used to select the data for the transmitter. The figure below shows the bit address assignments for the Transmit Data Rate Register when enabled for loading.

| 10   | 9    | 8    | 7    | 6    | 5    | 4      | 3        | 2    | 1    | 0    |

|------|------|------|------|------|------|--------|----------|------|------|------|

| XDV8 | XDR9 | XDR8 | XDR7 | XDR6 | XDR5 | XDR4   | XDR3     | XDR2 | XDR1 | XDR0 |

| MSB  | Oo - | Mo-  | 7    |      | -41  | M. Inc | <u> </u> | 1/1- |      | LSB  |

The transmit data rate is selected with the Transmit Data Rate Register in the same manner the receive data rate is selected with the Receive Data Rate Register. The algebraic expression for the Transmit Data Rate f<sub>xmt</sub> is

$$f_{xmt} = \frac{f_{XHBT}}{2} = \frac{f_{int}}{(2) (8^{XDV8}) (XDR9 - XDR0)}$$

For example, if the Transmit Data Rate Register is loaded with a value of 00110100001, XDV8 = 0, and XDR8 – XDR0 = 1A1<sub>16</sub> = 417<sub>10</sub>. If  $f_{int}$  = 1 MHz, the transmit data rate =  $f_{xmt}$  = [(1 x 10<sup>6</sup> ÷ 1) ÷ 417] ÷ 2 = 1199.0 bit per second.

## 2,1,2,5 Transmit Buffer Register

The transmit Buffer Register (XBR) is enabled for loading when LDCTRL = 0, LDIR = 0, LRDR = 0, LXDR = 0 and BRKON = 0 (see Table 2). The Transmit Buffer Register is used to store the next character to be transmitted When the transmitter is active, the contents of the Transmit Buffer Register are transferred to the Transmit Shif Register (XSR) each time the previous character has been completely transmitted (XSR becomes empty). The bi address assignments for the Transmit Buffer Register are shown below:

|    | 7    | 6    | 5     | 4    | 3    | 2    |       | 0    | 1    |

|----|------|------|-------|------|------|------|-------|------|------|

| v/ | XBR7 | XBR6 | XBR5  | XBR4 | XBR3 | XBR2 | XBR1  | XBR0 |      |

| 1  | MSB  | - 11 | 1.100 | COM  |      | -133 | W. Fo | LSB  | F.º. |

#### TRANSMIT BUFFER REGISTER BIT ADDRESS ASSIGNMENTS

All eight bits should be transferred into the register, regardless of the selected character length. The extraneous high order bits will be ignored for transmission purposes; however, loading of bit 7 is internally detected, which cause the Transmit Buffer Register Empty (XBRE) status flag to reset.

## 2.1.3 Input To CPU For CRU

The ACC occupies 32 bits of input CRU space. The CPU reads the 32 bits from the ACC to sense the status of the device. Table 4 shows the mapping between CRU bit address and ACC read data. Each CRU addressable read bit it described following Table 5.

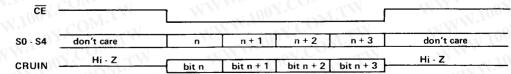

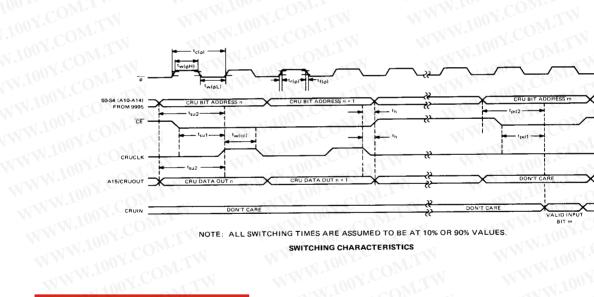

Status and data information is read from the ACC using  $\overline{\text{CE}}$ , S0-S4, and CRUIN. The following figure illustrates the relationship of the signals used to access four bits of data from the ACC.

#### ACC DATA ACCESS SIGNAL TIMING

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

1

causes the load control flag for . Loading of the bit indicated by

| M.                                          | RTSON                                  | 0                | TERS                                                                                    |                  | ·  -    | HCLU   |            | Character Length<br>00 5 | 9             | 1   | œ                    |                   | TMR0           |                 |                  |       | 1.1                        | RDR0   |      |                                                    |        | VDBV                        | 4)-4    |                  |                                                                              |                          | XBR0           |

|---------------------------------------------|----------------------------------------|------------------|-----------------------------------------------------------------------------------------|------------------|---------|--------|------------|--------------------------|---------------|-----|----------------------|-------------------|----------------|-----------------|------------------|-------|----------------------------|--------|------|----------------------------------------------------|--------|-----------------------------|---------|------------------|------------------------------------------------------------------------------|--------------------------|----------------|

| :                                           | BRKON                                  |                  | ER REGIS                                                                                |                  | 1 00    | HCL    |            | Charact<br>00            | 01            | 10  | Ξ                    |                   | TMR            | 1               |                  |       |                            | RDR1   | 00   |                                                    |        | , adv                       | YOY     |                  |                                                                              |                          | XBR1           |

| 9                                           | RIENB                                  | 2                | MIT BUFF                                                                                |                  | 01      |        |            |                          | 4M)           |     |                      |                   | TMR2           |                 | 1                |       | STER                       | RDR2   | 10   |                                                    |        | voo.                        | NOX NOX |                  |                                                                              |                          | XBR2           |

| ā                                           | XBIENB                                 | N m              | ID TRANS                                                                                |                  | EGISTER | CLK4M  | 1.0        | te                       | (\$/(3+CLK4M) |     |                      | REGISTER          | TMR3           |                 | 64 X TN          | 2     | ATE REGI                   | RDR3   | N.)  | )R ÷ 2                                             | 10     | VDB2                        | SHOY    |                  | R ÷ 2                                                                        | EB                       | XBR3           |

| Ş                                           | IIMENB                                 | 4                | A RATE, A                                                                               | 1                | "  -    | 1000   | Y          | y none                   |               | ppo |                      | INTERVAL REGISTER | TMR4           | }               | T = t X 64 X TMR | - Int | RECEIVE DATA RATE REGISTER | RDR4   |      | DV8 + RE                                           | 0,0    | AATE REG                    | YOU'S   | ~(<br>\-         | 0X + 8√<br>-                                                                 | FR REGIST                | XBR4           |

| 15<br>15                                    | DSCENB TIMENB XBIENB RIENB BRKON RISON | 'n               | CONTROL, INTERVAL. RECEIVE DATA RATE, TRANSMIT DATA RATE, AND TRANSMIT BUFFER REGISTERS | M.               |         | PENB   |            | Parity<br>0x none        | 10            |     | M.                   | Ţ                 | TMR5           | 1               | - F              | = _   | RECEIV                     | RDR5   | ADR. | $f_{rev} = f_{int} \div 8 \; RDV8 \div RDR \div 2$ | 1.3    | TRANSMIT DATA RATE REGISTER | - \     | XDR              | $f_{\text{tmt}} = f_{\text{int}} \div 8 \text{ XDV8} \div \text{XDR} \div 2$ | TRANSMIT BUFFER REGISTER | XBR5           |

| SIGNMEN                                     |                                        | 9                | ATE, TRA                                                                                | VV               | 7       | 7696   | <b>√</b>   | 3its   1-1/2             | 2             | Ċ(  | ) <u>M</u>           | V.                | TMR 6          |                 | -                |       |                            | BDR6   |      | frev =                                             |        | TRANS                       | AUNO    | ¥.               | f max                                                                        | TRAN                     | XBR6           |

| TABLE 4. CRU OUTPUT BIT ADDRESS ASSIGNMENTS | 3                                      |                  | VE DATA R                                                                               | N                |         | SBSI   | ,          | Stop Bits<br>00 1.1/     |               | ¥   | <del>بار</del><br>کا |                   | TIMR7          | TV              | V<br>X           | _     | •                          | RDR7   |      |                                                    | H<br>V | 1903                        | ) HOY   | 0                |                                                                              | .C                       | XBR7           |

| BIT ADD                                     |                                        | œ                | AL RECEI                                                                                |                  |         |        | )_<br> V   | 1.1                      | <del>0</del>  |     | , <u> </u>           | 0                 |                |                 | T'               | N     | -                          | 8 DB 8 |      | V                                                  |        | 9000                        | VUH8    | 1 <del>0</del> 1 | 10 <sup>-</sup>                                                              | <u> </u>                 | 30             |

| OUTPUT                                      | 3                                      | Ñ.               | L, INTERV                                                                               | _                | -       | N      | N          |                          | 1.<br>1.      |     | Ŋ.                   |                   | <del>-</del>   | W.              |                  | V     | V                          | врив   | -    | 4                                                  | N      | 0000                        |         | <u>-</u>         | 0                                                                            | ) Y                      | C              |

| 4. CRU                                      |                                        | 0                | CONTRO                                                                                  | _                | -       | V      |            | N<br>N                   | <u> </u>      |     | )( <del>Š</del>      |                   | .C             | 0               | V                | Ţ     | <b>W</b>                   | KDV6   | J_   |                                                    |        | o NOX                       | コノ      | V                | .1                                                                           | 00                       | <u> </u>       |

| TABLE                                       |                                        | . <del>.</del> = | LXDR                                                                                    | _                | -       | -<br>< | 7 <u>-</u> |                          | V             |     | . 10<br>IO           |                   | <br>×          | C <u>C</u>      | Ą                |       |                            | ×      | _    |                                                    | _      | 1                           |         | N                | N <del>-</del>                                                               | 10                       | -              |

| Y.C                                         | 3                                      | 12               |                                                                                         | N-               | ;       | _<br>< | -          | W                        | 4             |     |                      |                   | ×              | (. <del>C</del> |                  |       | V                          | Ţ      | N-   |                                                    |        | >                           | · //    |                  |                                                                              | 1                        | 0              |

|                                             | g                                      | o <sup>E</sup>   |                                                                                         | TV               |         | _<br>< | _          | - 1                      | A.<br>V       |     | V                    |                   | 0 <del>0</del> | יינו<br>מיי     |                  | 70    | Ī                          | •      |      | Ń                                                  | _      | -                           |         |                  | 1                                                                            | V                        | 0              |

| 106                                         | OF .                                   | - <del>4</del>   | ٦                                                                                       | . <u></u><br>1.T | W.      | -      | -          | -                        | _             |     | W.                   |                   | <br>•          | 00              | Y                | Ċ     | 0                          | 0      | 1.7  |                                                    |        | -                           |         |                  | N                                                                            | V                        | •              |

| 10                                          | RESET                                  | ₹                |                                                                                         | W.               | L/      | 1      | _          | -                        | _             |     | 120                  | 1 <sup>1</sup>    | <u> </u>       | 10              | 0                | 1     | <u> </u>                   |        | V.   | T                                                  | W      | -                           |         | _                | 4                                                                            | 11                       | <u>1</u><br>«X |

特力材料886-3-5753170 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

TMS 9902A ACC INPUT SELECT BIT ASSIGNMENTS

|       |          |       |                 |     | TMS 9902A AC          | TABLE 5<br>C INPUT SELECT BIT | T ASSIGNMENTS                                |

|-------|----------|-------|-----------------|-----|-----------------------|-------------------------------|----------------------------------------------|

| so    | AI<br>S1 | DDRES | SS <sub>2</sub> | S4  | ADDRESS <sub>10</sub> | NAME                          | DESCRIPTION                                  |

| - 1 N | 111      | 0 -   | ~ <1            | CU  |                       |                               |                                              |

| 1     | 1        | 1     | 1012            | 1   | 31                    | INT                           | Interrupt                                    |

| 1     |          | N 4º  | 1               | 0   | 30                    | FLAG                          | Register Load Control Flag Set               |

| 1//   | 11       | 1     | 0               | 1   | 29                    | DSCH                          | Data Set Status Change                       |

| 1     | N        | 1     | 0               | 0   | 28                    | CTS                           | Clear to Send                                |

| 1     | M III    | 0     | 10              | 01  | 27                    | D\$R                          | Data Set Ready                               |

| 1     | 1        | 0     | . 1             | 0   | 26                    | RTS                           | Request to Send                              |

| 1     | (1)      | 0     | 0               | 1   | 25                    | TIMELP                        | Timer Elapsed                                |

| 1     | 1        | 0     | 0               | 0   | 24                    | TIMERR                        | Timer Error                                  |

| 1     | 0        | 1     | 1               | 400 | 23                    | XSRE                          | Transmit Shift Register Empty                |

| 1     | 0        | 1     | N.              | 0   | 22                    | XBRE                          | Transmit Buffer Register Empty               |

| 1     | 0        | 1     | 0               | 1   | 21                    | RBRL                          | Receive Buffer Register Loaded               |

| 1     | 0        | 1     | 0               | 0   | 20                    | DSCINT                        | Data Set Status Change Interrupt (DSCH · DSC |

| 1     | 0        | 0     | 1               | 1   | 19                    | TIMINT                        | Timer Interrupt (TIMELP · TIMENB)            |

| 1     | 0        | 0     | 1               | 0   | 18                    | <b>3</b>                      | Not Used (always = 0)                        |

| 1     | 0        | 0     | 0               | 1   | 17                    | XBINT                         | Transmitter Interrupt (XBRE · XBIENB)        |

| 1     | 0        | 0     | 0               | 0   | 16                    | RBINT                         | Receiver Interrupt (RBRL · RIENB)            |

| 0     | 1        | 1     | 1               | 111 | 15                    | RIN                           | Receive Input                                |

| 0     | 1        | 1     | 1               | 0   | 14                    | RSBD                          | Receive Start Bit Detect                     |

| 0     | 1        | 1     | 0               | 1   | 13                    | RFBD                          | Receive Full Bit Detect                      |

| 0     | 1        | 1     | 0               | 0   | 12                    | RFER                          | Receive Framing Error                        |

| 0     | 1        | 0     | 1               | 1   | 11                    | ROVER                         | Receive Overrun Error                        |

| 0     | 1        | 0     | 1               | 0   | 10                    | RPER                          | Receive Parity Error                         |

| 0     | 1        | 0     | 0               | 1   | 9                     | RCVERR                        | Receive Error                                |

| 0     | 1        | 0     | 0               | 0   | 8                     |                               | Not Used (always = 0)                        |

|       |          |       |                 | 4 ' | 7-0                   | RBR7 - RBR0                   | Receive Buffer Register (Received Data)      |

| TW WWW            | + XBINT (Transmitter Interrupt) + RBINT (Receiver Interrupt). The interrupt output (INT) is active (LOW) when this status signal is a logic one. (Refer als to Section 2.6.)                                                                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 30 (FLAG) —   | FLAG = LDCTRL + LDIR + LRDR + LXDR + BRKON. When any of th register load control flags or BRKON is set, FLAG = 1 (see Section 2.1.1)                                                                                                                            |

| Bit 29 (DSCH) —   | Data Set Status Change. DSCH is set when the DSR or CTS input changes state To ensure recognition of the state change, DSR or CTS must remain stable in it new state for a minimum of two internal clock cycles. DSCH is reset by an output to bit 21 (DSCENB). |

| Bit 28 (CTS) —    | Clear To Send. The CTS signal indicates the inverted status of the $\overline{\text{CTS}}$ devicingut.                                                                                                                                                          |

| Bit 27 (DSR) —    | Data Set Ready. The DSR signal indicates the inverted status of the $\overline{\text{DSR}}$ devicingut.                                                                                                                                                         |

| Bit 26 (RTS) =    | Request To Send. The RTS signal indicates the inverted status of the $\overline{\text{RTS}}$ device output.                                                                                                                                                     |

| Bit 25 (TIMELP) - | Timer Elapsed. TIMELP is set each time the Interval Timer decrements to 0                                                                                                                                                                                       |

TIMELP is reset by an output to bit 20 (TIMENB),

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

NWW.100Y.COM.

|          | Bit 23 (XSRE) —                  |

|----------|----------------------------------|

|          | Bit 23 (XSRE) —                  |

|          | Bit 22 (XBRE) -                  |

|          |                                  |

|          |                                  |

|          | DI OA (DODL)                     |

|          | Bit 21 (HBHL) —                  |

|          |                                  |

|          | Bit 20 (DSCINT) -                |

|          |                                  |

|          | Bit 19 (TIMINT) —                |

|          | BIT 19 (TIMINT) —                |

|          | Bit 17 (XBINT) —                 |

|          | Bit 17 (XBINT) —                 |

|          | Bit 16 (RBINT) —  Bit 15 (RIN) — |

|          | Bit 16 (KBIN1) -                 |

|          |                                  |

|          | Bit 15 (RIN) —                   |

|          | Bit 14 (RSBD) —                  |

|          |                                  |

|          | Bit 13 (RFBD) —                  |

|          |                                  |

|          |                                  |

|          | Bit 12 (RFER)                    |

|          |                                  |

|          | Di+ 11 /POVER)                   |

|          | Bit IT (NOVEM)                   |

|          | Bit 10 (RPER) —                  |

|          |                                  |

|          | Bit 10 (RPER) —                  |

|          | 7.100                            |

|          | 886-3-5753170                    |

|          | 86-21-54151736                   |

| 胜特力电子(深圳 | ) 86-755-83298787                |

|          |                                  |

Http://www. 100y. com. tw

2.1.1) is set, When XSRE = 0, transmission of data is in progress. Transmit Buffer Register Empty. When XBRE = 1, the Transmit Buffer Registe does not contain the next character to be transmitted. XBRE is set each time the contents of the Transmit Buffer Register are transferred to the Transmi Shift Register, XBRE is reset by an output to bit 7 of the Transmit Buffe Register (XBR7), indicating that a character has been loaded. Receive Buffer Register Loaded. RBRL is set when a complete character ha been assembled in the Receive Shift Register, and the character is transferred to the Receive Buffer Register. RBRL is reset by an output to bit 18 (RIENB Receiver Interrupt Enable). Data Set Status Change Interrupt. DSCINT = DSCH (Data Set Status Change AND DSCENB (Data Set Status Change Interrupt Enable). DSCINT indicate the presence of an enabled interrupt caused by the changing of state of DSI Timer Interrupt. TIMINT = TIMELP (Timer Elapsed) AND TIMENB (Time Interrupt Enable). TIMINT indicates the presence of an enabled interrupt cause by the interval timer. Transmitter Interrupt. XBINT = XBRE (Transmit Buffer Register Empty) ANI XBIENB (Transmit Buffer Interrupt Enable). XBINT indicates the presence of an enabled interrupt caused by the transmitter. Receiver Interrupt. RBINT = RBRL (Receive Buffer Register Loaded) ANI RIENB (Receiver Interrupt Enable). RBINT indicates the presence of an enable interrupt caused by the receiver. Receive Input. RIN indicates the status of the RIN input to the device. Receive Start Bit Detect, RSBD is set a half bit time after the 1-to-0 transitio of RIN, indicating the start bit of a character. If RIN is not still 0 at such time RSBD is reset. Otherwise, RSBD remains true until the complete character has been received. This bit is normally used only for testing purposes. Receive Full Bit Detect. RFBD is set one bit time after RSBD is set to indicate the sample point for the first data bit of the received character. RSBD is rese when the character has been completely received. This bit is normally used only for testing purposes. Receive Framing Error. RFER is set when a character is received in which the stop bit, which should be a logic one, is a logic zero. RFER should only be rea when RBRL (Receive Buffer Register Loaded) is a one. RFER is reset when character with the correct stop bit is received. Receive Overrun Error. ROVER is set when a new character is received before the RBRL (Receive Buffer Register Loaded) flag is reset, indicating that the CP failed to read the previous character and reset RBRL before the present character is completely received. ROVER is reset when a character is received. RBRL is when the character is transferred to the Receive Buffer Register. Receive Parity Error. RPER is set when a character is received in which the parity is incorrect. RPER is reset when a character with correct parity is receive

Enable).

Timer Error, TIMERR is set whenever the Interval Timer decrements to 0 and TIMELP (Timer Elapsed) is already set, indicating that the occurrence of TIMELP was not recognized and cleared by the CPU before subsequent intervals elapsed. TIMERR is reset by an output to bit 20 (TIMENB, Timer Interrup

Transmit Shift Register Empty. When XSRE = 1, no data is currently being transmitted and the XOUT output is at logic one unless BRKON (see Section Bit 9 (RCVERR) -

Receive Error. RCVERR = RFER (Receive Framing Error) + ROVER (Receive Overrun Error) + RPER (Receive Parity Error). The RCVERR signal indicate the presence of an error in the most recently received character.

Bit 7-Bit 0 (RBR7-RBR0) -

Receive Buffer Register. The Receive Buffer Register contains the most recently received character. For character lengths of fewer than eight bits, the character is right-justified, with unused most significant bit(s) all zero(es). The presence of valid data in the Receive Buffer Register is indicated when RBRL (Receive

## 2.2 TRANSMITTER OPERATION

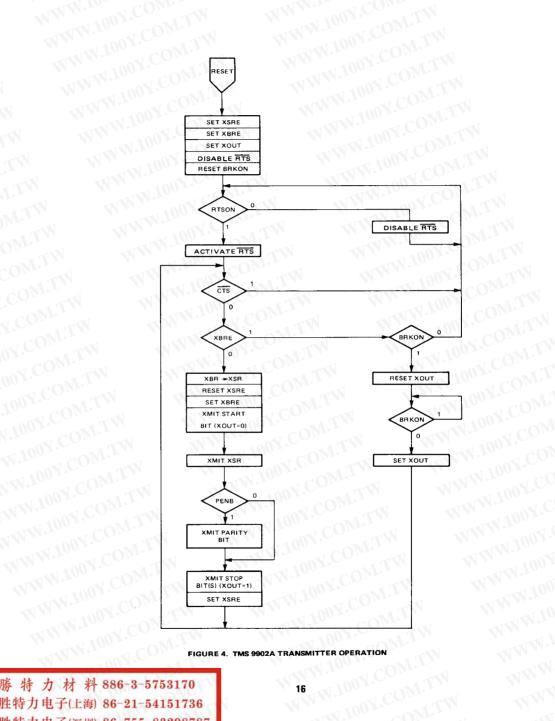

The operation of the transmitter is diagrammed in Figure 4. The transmitter is initialized by issuing the RESE command (output to bit 31), which causes the internal signals XSRE (Transmit Shift Register Empty) and XBR (Transmit Buffer Register Empty) to set, and BRKON to reset. Device outputs  $\overline{\text{RTS}}$  and XOUT are set, placing the transmitter in its idle state. When RTSON (Request-to-Send On) is set by the CPU, the  $\overline{\text{RTS}}$  output becomes active (LOW) and the transmitter becomes active when the  $\overline{\text{CTS}}$  input goes LOW.

Buffer Register Loaded) is a logic one.

## 2.2.1 Data Transmission

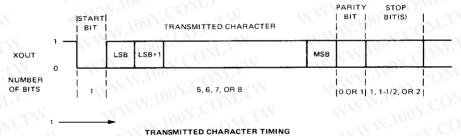

If the Transmit Buffer Register contains a character, transmission begins. The contents of the Transmit Buffer Register are transferred to the Transmit Shift Register, causing XSRE to reset and XBRE to set. The first bit tran mitted (start bit) is always a logic zero. Subsequently, the character is shifted out LSB first. Only the number of bi specified by RCL1 and RCL0 (character length select) of the Control Register are shifted. If parity is enabled, the correct parity bit is next transmitted. Finally the stop bit(s) selected by SBS1 and SBS0 of the Control Register at transmitted. Stop bits are always logic one. XSRE is set to indicate that no transmission is in progress, and the transmitter again tests XBRE to determine if the CPU has yet loaded the next character. The timing for a transmitter character is shown below.

## 2.2.2 BREAK Transmission

The BREAK message is transmitted only if XBRE = 1,  $\overline{\text{CTS}}$  = 0, and BRKON = 1. After transmission of the BREA message begins, loading of the Transmit Buffer Register is inhibited and XOUT is reset. When BRKON is reset by the CPU, XOUT is set and normal operation continues. It is important to note that characters loaded into the Transm Buffer Register are transmitted prior to the BREAK message, regardless of whether or not the character has beel loaded into the Transmit Shift Register before BRKON is set. Any character to be transmitted subsequent to transmission of the BREAK message may not be loaded into the Transmit Buffer Register until after BRKON is reset.

## 2.2.3 Transmission Termination

Whenever XSRE = 1 and BRKON = 0, the transmitter is idle with XOUT set to one. If RTSON is reset at this time  $\overline{RTS}$  device output will go inactive (HIGH), disabling further data transmission until RTSON is again set.  $\overline{RTS}$  will not go inactive, however, until any characters loaded into the Transmit Buffer Register prior to resetting RTSON are transmitted and BRKON = 0.

FIGURE 4. TMS 9902A TRANSMITTER OPERATION

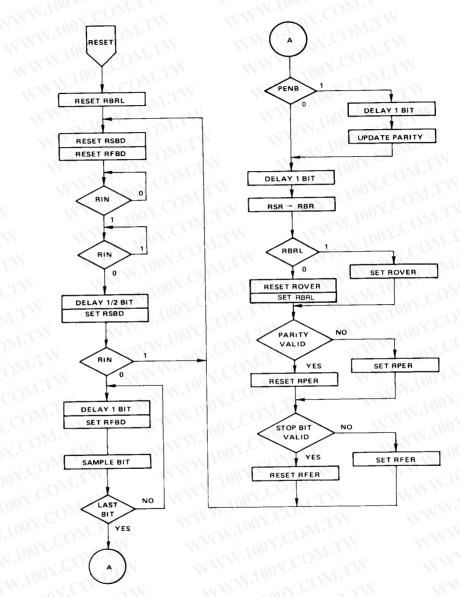

#### 2.3 RECEIVER OPERATION.

## 2.3.1 Receiver Initialization

Operation of the TMS 9902A receiver is diagrammed in Figure 5. The receiver is initialized whenever the CPU issu the RESET command. The RBRL (Receive Buffer Register Loaded) flag is reset to indicate that no character currently in the Receive Buffer Register, and the RSBD (Receive Start Bit Detect) and RFBD (Receive Full B Detect) flags are reset. The receiver remains in the inactive state until a one-to-zero transition is detected on the RI device input.

## 2.3.2 Start Bit Detection

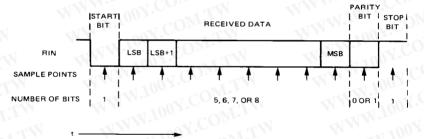

The receiver delays a half bit time and again samples RIN to ensure that a valid start bit has been detected. RIN = 0 after the half-bit delay, RSBD is set and data reception begins. If RIN = 1, no data reception occur

## 2.3.3 Data Reception

In addition to verifying the valid start bit, the half-bit delay after the one-to-zero transition also establishes the sample point for all subsequent data bits in a valid received character. Theoretically, the sample point is in the centrof each bit cell, thus maximizing the limits of acceptable distortion of data cells. After the first full bit delay, the least significant data bit is received and RFBD is set. The receiver continues to delay one-bit intervals and samp RIN until the selected number of bits are received. If parity is enabled, one additional bit is read for parity. After a additional bit delay, the received character is transferred to the Receive Buffer Register, RBRL is set, ROVE (Receive Overrun Error) and RPER (Receive Parity Error) are loaded with appropriate values, and RIN is tested for a valid stop bit. If RIN = 1, the stop bit is valid. RFER (Receive Framing Error), RSBD, and RFBD are reset, and the receiver waits for the next start bit to begin reception of the next character.

If RIN = 0 when the stop bit is sampled, RFER is set to indicate the occurrence of a framing error. RSBD and RFB are reset, but sampling for the start bit of the next character does not begin until RIN = 1. The timing for a receive character is depicted below.

RECEIVED CHARACTER TIMING

## 2.4 INTERVAL TIMER OPERATION

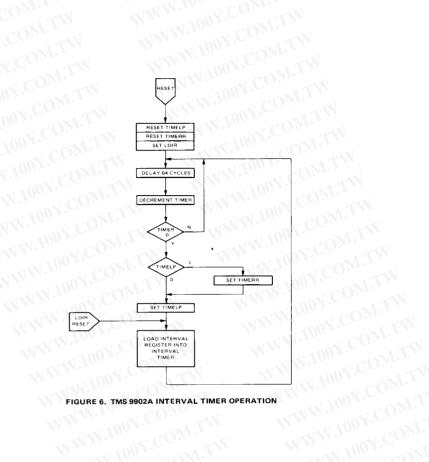

A flowchart of the operation of the Interval Timer is shown in Figure 6. Execution of the RESET command by the CPU causes TIMELP (Timer Elapsed) and TIMERR (Timer Error) to reset and LDIR (Load Interval Register) to see Resetting LDIR causes the contents of the Interval Register to be loaded into the Interval Timer, thus beginning the selected time interval. The timer is decremented every 64 internal clock cycles (every two internal clock cycles whe in Test Mode) until it reaches zero, at which time the Interval Timer is reloaded by the Interval Register and TIMELP is set. If TIMELP was already set, TIMERR is set to indicate that TIMELP was not cleared by the CPI before the next time period elapsed. Each time LDIR is reset, the contents of the Interval Register are loaded into the Interval Timer, thus restarting the timer (refer also to Section 2.1.2.2).

FIGURE 5. TMS 9902A RECEIVER OPERATION

WWW.1007.COM FIGURE 6. TMS 9902A INTERVAL TIMER OPERATION

INTERVAL TIMER SELECTION

L100Y.COM.TW 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

WWW.100Y.C

WT.Mc

LANY COM.TW

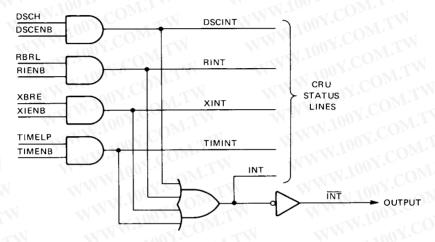

#### INTERRUPTS 2.5

The interrupt output (INT) is active (LOW) when any of the following conditions occurs and the corresponding interrupt has been enabled on the TMS 9902A by the CPU:

- DSR or CTS changes levels (DSCH = 1) (1)

- A character has been received and stored in the Receive Buffer Register (RBRL = 1) (2)

- The Transmit Buffer Register is empty (XBRE = 1) (3)

- The selected time interval has elapsed (TIMELP = 1) (4)

FIGURE 7. INT OUTPUT GENERATION

Figure 7 illustrates the logical equivalent of the ACC interrupt section. Table 6 lists the actions necessary to clear those conditions of the TMS 9902A that cause interrupts.

TABLE 6 TMS 9902A INTERRUPT CLEARING

|          | TABLE 6<br>TMS 9902A INTERRUPT CLEAR | ING                            |

|----------|--------------------------------------|--------------------------------|

| MNEMONIC | CAUSE                                | ACTION TO RESET                |

| DSCINT   | CTS or DSR change state              | Write a bit to DSCENB (bit 21) |

| RINT     | Receive Buffer Full                  | Write a bit to RIENB (bit 18)* |

| XINT     | Transmit Buffer Register Empty       | Load Transmit Buffer           |

| TIMINT   | Timer Elapsed                        | Write a bit to TIMENB (bit 20) |

Writing a zero to clear the interrupt will clear the interrupt and disable further interrupts.

# MMM.100X.COM. 1, TMS 9902A TERMINAL ASSIGNMENTS AND FUNCTIONS

| SIGNATURE         | PIN      | 1/0            | DESCRIPTION                                                                                                                             | -1 COM-                           |

|-------------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| INT               | 100      | 0              | Interrupt — when active (LOW), the $\overline{\text{INT}}$ output indicates that at least one of the interrupt conditions has occurred. | TMS 9902A<br>18-PIN PACKAG        |

| XOUT              | 2        | 00             | Transmitter Serial Data Output line — XOUT, remains inactive (HIGH) when TMS 9902A is not transmitting.                                 | INT 0 1 80                        |

| RIN               | 3        | 10             | Receiver Serial Data Input Line — RCV must be held in the inactive (HIGH) state when not receiving data.                                | RIN 0 3 16 0                      |

|                   | W.       | V.7            | A transition from HIGH to LOW activates the receiver circuitry.                                                                         | CRUIN 0 4 15 0                    |

| CRUIN             | 4        | 0              | Serial data output pin from TMS 9902A to CRUIN                                                                                          | RTS 0 5 14 0                      |

|                   | W        | 444            | input pin of the CPU.                                                                                                                   | CTS 0 6 13 0                      |

| RTS               | 5        | 0              | Request-to-Send output from TMS 9902A to modem, RTS is enabled by the CPU and remains active (LOW)                                      | DSR 0 7 12 0                      |

| N_                | 3/       | W              | during transmission from the TMS 9902A.                                                                                                 | CRUOUT B 110                      |

| СТŠ               | 6        | NV             | Clear-to-Send input from modem to TMS 9902A.  When active (LOW), it enables the transmitter section of TMS 9902A.                       | Vss 0 9 10 0                      |

| DSR               | 7        | <b>√</b> 1√    | Data Set Ready input from modem to TMS 9902A, DSR                                                                                       | generates an interrupt when it ch |

| CRUOUT            | 8        | 1              | Serial data input line to TMS 9902A from CRUOUT line o                                                                                  | of the CPU.                       |

| V <sub>SS</sub>   | 9        | 1              | Ground reference voltage.                                                                                                               |                                   |

| S4 (LSB)          | 10       | 1              | Address Select Lines. The data bit being accessed by th                                                                                 | e CPU interface is specified by   |

| S3<br>S2          | 11<br>12 |                | on S0-S4.                                                                                                                               |                                   |

| S1                | 13       | 1              | W.100 COM.1                                                                                                                             |                                   |

| SO .              | 14       | '              | WW 100Y.Com INTW                                                                                                                        |                                   |

| CRUCLK            | 15       | 1              | CRU Clock. When active (HIGH), indicates valid data on t                                                                                | the CRUOUT line for the 9902A     |

| $\overline{\phi}$ | 16       | ı              | TTL Clock.                                                                                                                              |                                   |

| CE                | 17       | 1              | Chip Enable — when $\overline{\text{CE}}$ is inactive (HIGH), TMS 9903 impedance when $\overline{\text{CE}}$ is inactive (HIGH).        | 2A CRU interface is disabled.     |

| VCC               | 18       | N <sub>E</sub> | Supply voltage (+5 V nominal).                                                                                                          |                                   |

特力材料886-3-5753170 胜特力电子(深圳) 86-755-83298787 WWW.100Y.COM.TW Http://www. 100y. com. tw

WWW.100Y.COM.1

WWW.1003

W.100Y.COM.TW W.100Y.COM.TW

## 3 DEVICE APPLICATION

This section describes the software interface between the CPU and the ACC and discusses some of the design considerations in the use of this device for asynchronous communications applications.

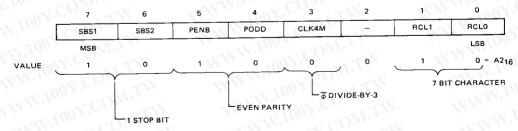

## 3.1 DEVICE INITIALIZATION

The ACC is initialized by the RESET command from the CPU (output bit 31), followed by loading the Control, Interval, Receive Data Rate, and Transmit Data Rate registers. Assume that the value to be loaded into the CRU Base Register (register 12) in order to point to bit 0 is 004016. In this application characters have seven bits of data plus even parity and one stop bit. The  $\overline{\phi}$  input to the ACC is a 3 MHz signal. The ACC divides this signal frequency by three to generate an internal clock frequency of 1 MHz. An interrupt is generated by the Interval Timer every 1.6 milliseconds when timer interrupts are enabled. The transmitter operates at a data rate of 300 bits per second, and the receiver operates at 1200 bits per second.

#### NOTE

To operate both the transmitter and receiver at 300 bits per second, delete the "LDCR @RDR,11" instruction (see below). The "LDCR @XDR,12" instruction will cause both data rate registers to be loaded and LRDR and LXDR to reset.

## 3.1.1 Initialization Program

The initialization program for the configuration described above is shown below. The RESET command disables all interrupts, initializes all controllers, and sets the four register load control flags (LDCTRL, LDIR, LRDR, and LXDR). Loading the last bit of each of the registers causes the load control flag to reset automatically.

| LI   | R12,>40   | INITIALIZE CRU BASE           |

|------|-----------|-------------------------------|

| SBO  | 31        | RESET COMMAND                 |

| LDCR | @ CNTRL,8 | LOAD CONTROL AND RESET LDCTRL |

| LDCR | @ INTVL.8 | LOAD INTERVAL AND RESET LDIR  |

| LDCR | @ RDR,11  | LOAD RDR AND RESET LRDR       |

| LDCR | @ XDR.12  | LOAD XDR AND RESET LXDR       |

|      | 1,003     |                               |

|      |           |                               |

CNTROL BYTE >A2

INTVL BYTE 1600/64

RDR DATA >1A1

XDR DATA >4D0

The RESET command initializes all subcontrollers, disables interrupts, and sets LDCTRL, LDIR, LRDR, and LXDR enabling loading of the control register.

## 3.1.2 Control Register

The options listed in Table 3 in Section 2.1.2.1 are selected by loading the value shown below.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

22

## 3.1.3 Interval Register

To set up the Interval Register to generate an interrupt every 1.6 milliseconds, load the value into the Interval Register to specify the number of 64-microsecond increments in the total interval desired.

25 X 64 MICROSECONDS = 1.6 MILLISECONDS

## 3.1.4 Receive Data Rate Register

To set the data rate for the receiver to 1200 bits per second, load the value into the Receive Data Rate Register shown below:

106 ÷ 1 ÷ 417 ÷ 2 = 1199.04 BITS PER SECOND

## 3.1.5 Transmit Data Rate Register

To program the data rate for the transmitter for 300 bits per second, load the following value into the Transm Data Rate Register.

1 X 106 ÷ 8 ÷ 208 ÷ 2 = 300.48 BITS PER SECOND

## 3.2 DATA TRANSMISSION

The subroutine shown below demonstrates a simple loop for transmitting a block of data.

|       | LI   | R0, LISTAD  | INITIALIZE LIST POINTER                     |

|-------|------|-------------|---------------------------------------------|

|       | LI   | R1, COUNT   | INITIALIZE BLOCK COUNT                      |

|       | LI   | R12, CRUBAS | INITIALIZE CRU BASE                         |

|       | SBO  | 16          | TURN ON TRANSMITTER                         |

| XMTLP | ТВ   | 22          | WAIT FOR XBRE = 1                           |

|       | JNE  | XMTLP       |                                             |

|       | LDCR | *R0+,8      | LOAD CHARACTER INCREMENT POINTER RESET XBRE |

|       | DEC  | R1          | DECREMENT COUNT                             |

|       | JNE  | XMTLP       | LOOP IF NOT COMPLETE                        |

|       | SBZ  | 16          | TURN OFF TRANSMITTER                        |

|       |      |             |                                             |

After initializing the list pointer, block count, and CRU base address, RTSON is set to cause the transmitter and the RTS output to become active. Data transmission does not begin, however, until the CTS input becomes active. After the final character is loaded into the Transmit Buffer Register, RTSON is reset. The transmitter and the RTS output do not become inactive until the final character is transmitted.

## 3.3 DATA RECEPTION

The following software will cause a block of data to be received and stored in memory

| CARRET  | BYTE  | >0D        | N. J. COM                           |

|---------|-------|------------|-------------------------------------|

| RCVBLK  | LI    | R2, RCVLST | INITIALIZE LIST COUNT               |

|         | - EI  | R3, MXRCNT | INITIALIZE MAX COUNT                |

|         | LLOON | R4, CARRET | SET UP END OF BLOCK CHARACTER       |

| RCVLP   | TB    | 21         | WAIT FOR RBRL = 1                   |

| WC V EI | JNE   | RCVLP      |                                     |

|         | STCR  | *R2.8      | STORE CHARACTER                     |

|         | SBZ   | 18         | RESET RBRL                          |

|         | DEC   | R3         | DECREMENT COUNT                     |

|         | JEQ   | RCVEND     | END IF COUNT = 0                    |

|         |       | *R2+,R4    | COMPARE TO EOB CHARACTER, INCREMENT |

|         | СВ    | n2+,n4     | POINTER                             |

|         | JNE   | RCVLP      | LOOP IF NOT COMPLETE                |

| RCVEND  | RT    | TOWN COM   | END OF SUBROUTINE                   |

|         |       |            |                                     |

## 3.4 REGISTER LOADING AFTER INITIALIZATION

The Control, Interval, and Data Rate registers may be reloaded after initialization. For example, it may be desirable to change the interval of the timer. Assume that the interval is to be changed to 10.24 milliseconds; the instruction sequence is:

|        | SBO<br>LDCR | 13<br>@ INTVL2,8 | LOAD REGISTER, RE |  |

|--------|-------------|------------------|-------------------|--|

|        | . 11        |                  |                   |  |

| INTVL2 | BYTE        | 10240/64         |                   |  |

When transmitter interrupts are enabled, caution should be exercised to ensure that a transmitter interrupt does not occur while the load control flag is set. For example, if a transmitter interrupt occurs between execution of the "SBO 13" and the next instruction, the Transmit Buffer is not enabled for loading when the Transmitter Interrupt service routine is entered because the LDIR flag is set. This situation may be avoided by the following sequence:

| 3011100 7001     |                                    |                                       |                                                                                                                     |

|------------------|------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                  | BLWP                               | @ITVCHG                               | CALL SUBROUTINE                                                                                                     |

|                  | TW                                 |                                       |                                                                                                                     |

| ITVCPC           | LIMI<br>MOV<br>SBO<br>LDCR<br>RTWP | 0<br>@24(R13),R12<br>13<br>@ INTVL2,8 | MASK ALL INTERRUPTS<br>LOAD CRU BASE ADDRESS<br>SET FLAG<br>LOAD REGISTER AND RESET FLAG<br>RESTORE MASK AND RETURN |

|                  | M. TV                              |                                       |                                                                                                                     |

| ITVCHG<br>INTVL2 | DATA<br>BYTE                       | ACCWP, ITVCPC<br>10240/64             |                                                                                                                     |

|                  |                                    |                                       |                                                                                                                     |

In this case all interrupts are masked, ensuring that all interrupts are disabled while the load control flag is set

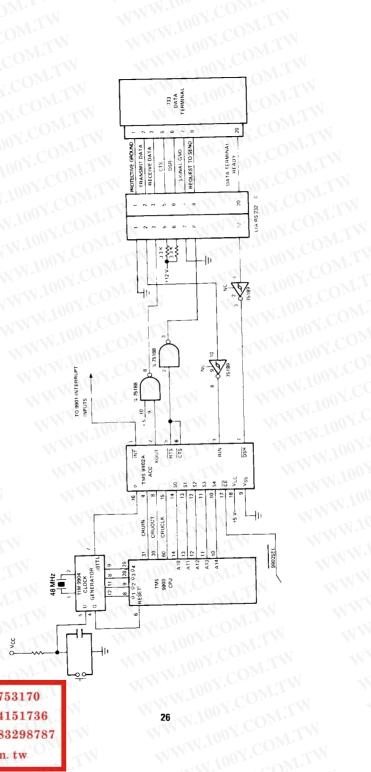

#### 3.5 INTERFACE TO A DATA TERMINAL

Following is a discussion of the TMS 9902A interface to a TI Model 733 data terminal as implemented on the TM 990/100M microcomputer module. Figure 8 diagrams the hardware interface, and Table 7 lists the software interface. The 733 data terminal is an ASCII-code, serial asynchronous, EIA device equipped with a keyboard thermal printer, and digital cassette tape.

#### 3.5.1 Hardware Interface

The hardware interface between the TMS 9902A and the 733 data terminal is shown in Figure 8. The asynchronous communication conforms to *EIA Standard RS-232-C*. The 75188 and 75189 perform the necessary level shifting between TTL levels and RS-232-C levels. The ACC chip enable (9902SEL) signal comes from decode circuitry which looks at A0-A9 on CRU cycles. The interrupt output (INT) of the TMS 9902A is sent to the TMS 9901 for prior tization and encoding. When the 9902A is communicating with a terminal, the RTS pin can be connected to the CT pin because the terminal will always be in the clear-to-send (CTS) condition.