SNLS097C - JULY 2000-REVISED FEBRUARY 2013

# DS36C280 Slew Rate Controlled CMOS EIA-RS-485 Transceiver

Check for Samples: DS36C280

## **FEATURES**

- 100% RS-485 Compliant

- Guaranteed RS-485 Device Interoperation

- Low Power CMOS Design:  $I_{\rm CC}$  500 µA max

- **Adjustable Slew Rate Control** Minimizes EMI Effects

- Built-In Power Up/Down Glitch-Free Circuitry

- Permits Live Transceiver Insertion/Displacement

- SOIC Packages

- Industrial Temperature Range: -40°C to +85°C

- **On-board Thermal Shutdown Circuitry**

- Prevents Damage to the Device in the Event of Excessive Power Dissipation

- Wide Common Mode Range: -7V to +12V

- Receiver Open Input Fail-safe (1) •

- ¼ unit load (DS36C280): ≥128 nodes

- 1/2 unit load (DS36C280T): ≥64 nodes

- ESD (human body model): ≥2 kV

- Non-terminated, Open Inputs only (1)

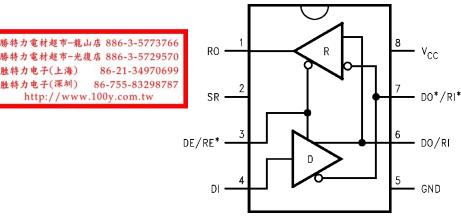

## **Connection and Logic Diagram**

## DESCRIPTION

The DS36C280 is a low power differential bus/line transceiver designed to meet the requirements of RS-485 Standard for multipoint data transmission. In addition, it is compatible with TIA/EIA-422-B.

The slew rate control feature allows the user to set the driver rise and fall times by using an external resistor. Controlled edge rates can reduce switching EMI.

The CMOS design offers significant power savings over its bipolar and ALS counterparts without sacrificing ruggedness against ESD damage. The device is ideal for use in battery powered or power conscious applications. I<sub>CC</sub> is specified at 500 µA maximum.

The driver and receiver outputs feature TRI-STATE capability. The driver outputs operate over the entire common mode range of -7V to +12V. Bus contention or fault situations are handled by a thermal shutdown circuit, which forces the driver outputs into the high impedance state.

The receiver incorporates a fail safe circuit which guarantees a high output state when the inputs are left open <sup>(1)</sup>.

Figure 1. See Package Number D (R-PDSO-G8)

Ā

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

ISTRUMENTS

EXAS

## Truth Table<sup>(1)</sup>

| DRIVER SECTION   |    |                     |         |

|------------------|----|---------------------|---------|

| DE/RE*           | DI | DO/RI               | DO*/RI* |

| Н                | Н  | Н                   | L       |

| Н                | L  | L                   | Н       |

| L                | Х  | Z                   | Z       |

| RECEIVER SECTION |    |                     |         |

| DE/RE*           |    | RI-RI*              | RO      |

| L                |    | ≥+0.2V              | Н       |

| L                |    | ≤-0.2V              | L       |

| Н                |    | Х                   | Z       |

| L                |    | OPEN <sup>(1)</sup> | Н       |

#### (1) Non-terminated, Open Inputs only

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings<sup>(1)(2)</sup>

| Supply Voltage (V <sub>CC</sub> )         | +12V                             |

|-------------------------------------------|----------------------------------|

| Input Voltage (DE/RE*, & DI)              | -0.5V to (V <sub>CC</sub> +0.5V) |

| Common Mode (V <sub>CM</sub> )            |                                  |

| Driver Output/Receiver Input              | ±15V                             |

| Input Voltage (DO/RI, DO*/RI*)            | ±14V                             |

| Receiver Output Voltage                   | -0.5V to (V <sub>CC</sub> +0.5V) |

| Maximum Package Power Dissipation @ +25°C |                                  |

| M Package 1190 mV, derate                 | 9.5 mW/°C above +25°C            |

| Storage Temperature Range                 | −65°C to +150°C                  |

| Lead Temperature                          | +260°C                           |

| (Soldering 4 sec.)                        |                                  |

(1) "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

## **Recommended Operating Conditions**

|                                                  | Min   | Тур  | Max   | Units |

|--------------------------------------------------|-------|------|-------|-------|

| Supply Voltage (V <sub>CC</sub> )                | +4.75 | +5.0 | +5.25 | V     |

| Bus Voltage                                      | -7    |      | +12   | V     |

| Operating Free Air Temperature (T <sub>A</sub> ) |       |      |       |       |

| DS36C280T                                        | -40   | +25  | +85   | °C    |

| DS36C280                                         | 0     | +25  | +70   | °C    |

## Electrical Characteristics<sup>(1)(2)</sup>

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified

| Symbol            | Parameter                            | Conditio                                               | ons                                       | Ref                    | erence                | Min    | Тур   | Max  | Units |

|-------------------|--------------------------------------|--------------------------------------------------------|-------------------------------------------|------------------------|-----------------------|--------|-------|------|-------|

| DIFFERE           | INTIAL DRIVER CHARACTERIS            | TICS                                                   |                                           |                        |                       |        |       |      |       |

| V <sub>OD1</sub>  | Differential Output Voltage          | I <sub>O</sub> = 0 mA (No Load)                        |                                           |                        |                       | 1.5    |       | 5.0  | V     |

| V <sub>OD0</sub>  | Output Voltage                       | $I_0 = 0 \text{ mA}$                                   |                                           |                        | 422)<br>485)          | 0      |       | 5.0  | V     |

| V <sub>OD0*</sub> | Output Voltage                       | (Output to GND)                                        | (Output to GND)                           |                        |                       |        |       | 5.0  | V     |

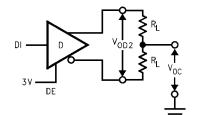

| V <sub>OD2</sub>  | Differential Output Voltage          | $R_L = 50\Omega$                                       |                                           | (422)                  | Figure 2              | 2.0    | 2.8   |      | V     |

|                   | (Termination Load)                   | $R_L = 27\Omega$                                       |                                           | (485)                  |                       | 1.5    | 2.3   | 5.0  | V     |

| $\Delta V_{OD2}$  | Balance of V <sub>OD2</sub>          | $R_L = 27\Omega \text{ or } 50\Omega$                  |                                           |                        | (3)                   |        | 0.4   |      |       |

|                   | V <sub>OD2</sub> - V <sub>OD2*</sub> |                                                        |                                           | (42)                   | 2, 485)               | -0.2   | 0.1   | +0.2 | V     |

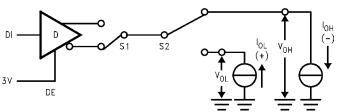

| V <sub>OD3</sub>  | Differential Output Voltage          | R1 = 54Ω, R2 = 375Ω                                    |                                           | Fig                    | gure 3                | 1.5    | 2.0   | 5.0  | V     |

|                   | (Full Load)                          | $V_{\text{TEST}} = -7V$ to +12V                        |                                           |                        |                       |        |       |      |       |

| V <sub>OC</sub>   | Driver Common Mode                   | $R_L = 27\Omega$                                       |                                           | (485)                  | Figure 2              | 0      |       | 3.0  | V     |

|                   | Output Voltage                       | $R_L = 50\Omega$                                       |                                           | (422)                  |                       | 0      |       | 3.0  | V     |

| ΔV <sub>OC</sub>  | Balance of V <sub>OC</sub>           | Balance of $V_{OC}$ $R_L = 27\Omega$ or <sup>(3)</sup> |                                           |                        |                       |        |       |      |       |

|                   | V <sub>OC</sub> - V <sub>OC*</sub>   | $R_L = 50\Omega$                                       |                                           | (42)                   | 2, 485)               | -0.2   |       | +0.2 | V     |

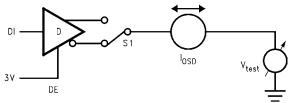

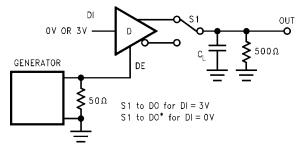

| I <sub>OSD</sub>  | Driver Output Short-Circuit          | V <sub>O</sub> = +12V                                  | (485)                                     |                        |                       | 200    | +250  | mA   |       |

|                   | Current                              | V <sub>O</sub> = -7V                                   |                                           | (4                     | 485)                  |        | -190  | -250 | mA    |

| RECEIVE           | ER CHARACTERISTICS                   |                                                        |                                           |                        |                       |        |       |      |       |

| V <sub>TH</sub>   | Differential Input High              | $V_{O} = V_{OH}, I_{O} = -0.4 \text{ m}$               | $V_{O} = V_{OH}, I_{O} = -0.4 \text{ mA}$ |                        |                       |        | 0.005 |      |       |

|                   | Threshold Voltage                    | $-7V \le V_{CM} \le +12V$                              |                                           | (4)                    |                       | +0.035 | +0.2  | V    |       |

| V <sub>TL</sub>   | Differential Input Low               | $V_{O} = V_{OL}, I_{O} = 0.4 \text{ mA}$               | 1                                         | (422, 485)             |                       |        | 0.005 |      |       |

|                   | Threshold Voltage                    | $-7V \le V_{CM} \le +12V$                              |                                           |                        | -0.2                  | -0.035 |       | V    |       |

| V <sub>HST</sub>  | Hysteresis <sup>(5)</sup>            | $V_{CM} = 0V$                                          |                                           |                        |                       |        | 70    |      | mV    |

| R <sub>IN</sub>   | Input Resistance                     | $-7V \le V_{CM} \le +12V$                              |                                           | DS3                    | 6C280T                | 24     | 68    |      | kΩ    |

| R <sub>IN</sub>   | Input Resistance                     | $-7V \le V_{CM} \le +12V$                              |                                           | DS3                    | 6C280                 | 48     | 68    |      | kΩ    |

| I <sub>IN</sub>   | Line Input Current                   | Other Input = 0V                                       | DS36C280                                  | $V_{IN} = +12$         | 2V                    | 0      | 0.19  | 0.25 | mA    |

|                   | (6)                                  | $DE = V_{IL}, RE^* = V_{IL}$                           |                                           | $V_{IN} = -7$          | V <sub>IN</sub> = −7V |        | -0.1  | -0.2 | mA    |

|                   |                                      | V <sub>CC</sub> = 4.75 to 5.25                         | V <sub>IN</sub> = +12                     | 2V                     | 0                     | 0.19   | 0.5   | mA   |       |

|                   |                                      | or 0V                                                  | $V_{IN} = -7$                             | V                      | 0                     | -0.1   | -0.4  | mA   |       |

| I <sub>ING</sub>  | Line Input Current                   | Other Input = 0V                                       | DS36C280                                  | V <sub>IN</sub> = +12V |                       | 0      | 0.19  | 0.25 | mA    |

|                   | Glitch <sup>(6)</sup>                | $DE = V_{IL}, RE^* = V_{IL}$                           |                                           | $V_{IN} = -7V$         |                       | 0      | -0.1  | -0.2 | mA    |

|                   |                                      | V <sub>CC</sub> = +3.0V                                | V <sub>IN</sub> = +12V                    |                        | 0                     | 0.19   | 0.5   | mA   |       |

|                   |                                      | or 0V $T_A = 25^{\circ}C$                              |                                           | $V_{IN} = -7V$         |                       | 0      | -0.1  | -0.4 | mA    |

| I <sub>B</sub>    | Input Balance Test                   | RS = 500Ω                                              | (42                                       | 22) <sup>(7)</sup>     |                       |        | ±400  | mV   |       |

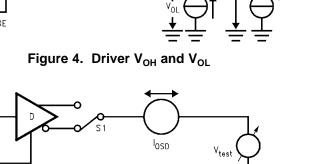

| V <sub>OH</sub>   | High Level Output Voltage            | $I_{OH} = -4 \text{ mA}, V_{ID} = +0$                  | .2V                                       | RO                     |                       | 3.5    | 4.6   |      | V     |

| V <sub>OL</sub>   | Low Level Output Voltage             | $I_{OL} = +4 \text{ mA}, V_{ID} = -0$                  | Figure 12                                 |                        |                       | 0.3    | 0.5   | V    |       |

| I <sub>OSR</sub>  | Short Circuit Current                | V <sub>O</sub> = GND                                   |                                           |                        | RO                    | 7      | 35    | 85   | mA    |

| I <sub>OZR</sub>  | TRI-STATE Leakage Current            | $V_0 = 0.4V$ to 2.4V                                   | -                                         |                        |                       |        |       | ±1   | μA    |

|                   | CHARACTERISTICS                      | 1                                                      |                                           |                        |                       |        | 1     | 1    |       |

(1) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD1</sub> and V<sub>OD2</sub>.

(2)

- All typicals are given for:  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$ . Delta  $|V_{OD2}|$  and Delta  $|V_{OC}|$  are changes in magnitude of  $V_{OD2}$  and  $V_{OC}$ , respectively, that occur when input changes state. (3)

- Threshold parameter limits specified as an algebraic value rather than by magnitude. Hysteresis defined as  $V_{HST} = V_{TH} V_{TL}$ . (4)

- (5)

- $I_{IN}$  includes the receiver input current and driver TRI-STATE leakage current. (6)

- For complete details of test, see RS-485. (7)

EXAS STRUMENTS

www.ti.com

## Electrical Characteristics<sup>(1)(2)</sup> (continued)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified

| Symbol           | Parameter                | Condition               | Reference     | Min             | Тур | Max             | Units |    |

|------------------|--------------------------|-------------------------|---------------|-----------------|-----|-----------------|-------|----|

| V <sub>IH</sub>  | High Level Input Voltage |                         |               | 2.0             |     | V <sub>CC</sub> | V     |    |

| V <sub>IL</sub>  | Low Level Input Voltage  |                         |               | GND             |     | 0.8             | V     |    |

| I <sub>IH</sub>  | High Level Input Current | $V_{IH} = V_{CC}$       | DE/RE*,<br>DI |                 |     | 2               | μΑ    |    |

| IIL              | Low Level Input Current  | $V_{\rm CC} = 5.0V$     |               |                 |     |                 | -2    | μΑ |

|                  |                          | $V_{CC} = +3.0V$        | $V_{IL} = 0V$ |                 |     |                 | -2    | μΑ |

|                  |                          | SR = 0V                 | R = 0V        |                 |     |                 | -1    | mA |

| I <sub>CCR</sub> | Power Supply Current     | Driver OFF, Receiver C  |               |                 | 200 | 500             | μA    |    |

| I <sub>CCD</sub> | (No Load)                | Driver ON, Receiver OFF |               | V <sub>cc</sub> |     | 200             | 500   | μΑ |

## Switching Characteristics<sup>(1)(2)(3)</sup>

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified

| Symbol            | Parameter                                     | Conditions                             | Reference             | Min | Тур  | Max  | Units |

|-------------------|-----------------------------------------------|----------------------------------------|-----------------------|-----|------|------|-------|

| DRIVER CI         | HARACTERISTICS                                |                                        |                       |     |      | •    | •     |

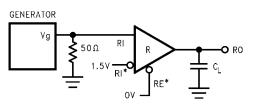

| t <sub>PHLD</sub> | Differential Propagation<br>Delay High to Low | $R_L = 54\Omega, C_L = 100 \text{ pF}$ | Figure 6, Figure 7    | 10  | 399  | 1000 | ns    |

| t <sub>PLHD</sub> | Differential Propagation<br>Delay Low to High |                                        |                       | 10  | 400  | 1000 | ns    |

| t <sub>SKD</sub>  | Differential Skew                             |                                        |                       | 0   | 4    | 10   |       |

|                   | t <sub>PHLD</sub> - t <sub>PLHD</sub>         |                                        |                       | 0   | 1    | 10   | ns    |

| t <sub>r</sub>    | Rise Time                                     | SR = Open                              |                       |     | 2870 |      | ns    |

| t <sub>f</sub>    | Fall Time                                     |                                        |                       |     | 3070 |      | ns    |

| t <sub>r</sub>    | Rise Time                                     | SR = 100 kΩ                            |                       |     | 1590 |      | ns    |

| t <sub>f</sub>    | Fall Time                                     |                                        |                       |     | 1640 |      | ns    |

| t <sub>r</sub>    | Rise Time                                     | SR = Short                             |                       | 100 | 337  | 1000 | ns    |

| t <sub>f</sub>    | Fall Time                                     |                                        |                       | 100 | 348  | 1000 | ns    |

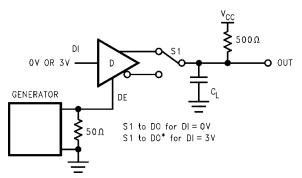

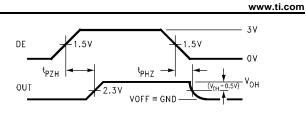

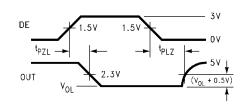

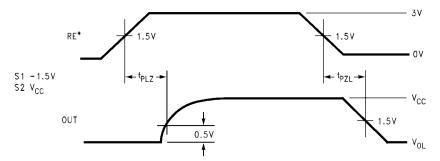

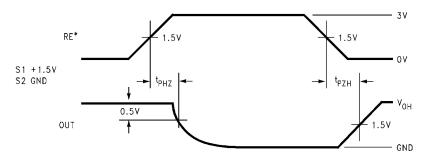

| t <sub>PHZ</sub>  | Disable Time High to Z                        | C <sub>L</sub> = 15 pF                 | Figure 8, Figure 9    |     | 1100 | 2000 | ns    |

| t <sub>PLZ</sub>  | Disable Time Low to Z                         |                                        | Figure 10, Figure 11  |     | 500  | 800  | ns    |

| t <sub>PZH</sub>  | Enable Time Z to High                         | C <sub>L</sub> = 100 pF                | Figure 8, Figure 9    |     | 300  | 500  | ns    |

| t <sub>PZL</sub>  | Enable Time Z to Low                          |                                        | Figure 10, Figure 11  |     |      |      | ns    |

| RECEIVER          | CHARACTERISTICS                               |                                        |                       |     |      |      |       |

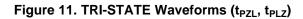

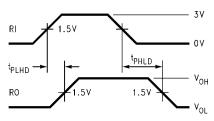

| t <sub>PHL</sub>  | Propagation Delay<br>High to Low              | C <sub>L</sub> = 15 pF                 |                       | 30  | 210  | 400  | ns    |

| t <sub>PLH</sub>  | Propagation Delay<br>Low to High              |                                        | Figure 13, Figure 14  | 30  | 190  | 400  | ns    |

| t <sub>SK</sub>   | Skew,  t <sub>PHL</sub> - t <sub>PLH</sub>    |                                        |                       | 0   | 20   | 50   | ns    |

| t <sub>PLZ</sub>  | Output Disable Time                           | C <sub>L</sub> = 15 pF                 |                       |     | 50   | 150  | ns    |

| t <sub>PHZ</sub>  |                                               |                                        | Figure 15, Figure 16, |     | 55   | 150  | ns    |

| t <sub>PZL</sub>  | Output Enable Time                            |                                        | Figure 17             |     | 40   | 150  | ns    |

| t <sub>PZH</sub>  |                                               |                                        |                       |     | 45   | 150  | ns    |

All typicals are given for: V<sub>CC</sub> = +5.0V, T<sub>A</sub> = + 25°C.

C<sub>L</sub> includes probe and jig capacitance.

SR = GND for all Switching Characteristics unless otherwise specified.

Copyright © 2000-2013, Texas Instruments Incorporated

### SNLS097C -JULY 2000-REVISED FEBRUARY 2013

$R_{2}$

R2

R 1

Figure 3. Driver V<sub>OD3</sub>

## PARAMETER MEASUREMENT INFORMATION

DI

3V DF

Figure 2. Driver  $V_{OD2}$  and  $V_{OC}$

**Q** DO GENERATOR DI Ş R D ≶ 50 N 3V **ð** do\* DE С

### Figure 6. Driver Differential Propagation Delay Test Circuit

90%

٥v

1.5V

V<sub>test</sub> =

-7V to +12V

Figure 7. Driver Differential Propagation Delays

CP = CROSSING POINT

<sup>t</sup>PHLD

90%

0٧

10%

Vtest = -7V to +12V

Figure 5. Driver I<sub>OSD</sub>

Product Folder Links: DS36C280

DI

DO\*

DO

t<sub>PLHD</sub>

10%

$Vo = DO - DO^*$

1.5V

## DS36C280

### SNLS097C-JULY 2000-REVISED FEBRUARY 2013

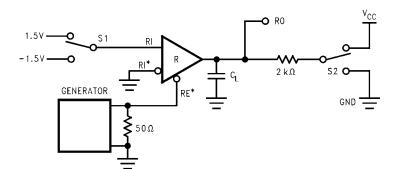

Figure 8. TRI-STATE Test Circuit (t<sub>PZH</sub> , t<sub>PHZ</sub>)

Figure 10. TRI-STATE Test Circuit (t<sub>PZL</sub>, t<sub>PLZ</sub>)

Figure 12. Receiver  $V_{\text{OH}}$  and  $V_{\text{OL}}$

Figure 9. TRI-STATE Waveforms (t<sub>PZH</sub>, t<sub>PHZ</sub>)

Figure 13. Receiver Differential Propagation Delay Test Circuit

Figure 14. Receiver Differential Propagation Delay Waveforms

SNLS097C -JULY 2000-REVISED FEBRUARY 2013

Figure 15. Receiver TRI-STATE Test Circuit

Figure 16. Receiver Enable and Disable Waveforms (t<sub>PLZ</sub>, t<sub>PZL</sub>)

Figure 17. Receiver Enable and Disable Waveforms ( $t_{PHZ}$ ,  $t_{PZH}$ )

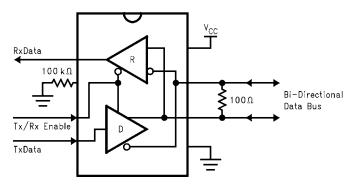

## **Typical Application Information**

Figure 18. Typical Pin Connection

SNLS097C – JULY 2000 – REVISED FEBRUARY 2013

| Pin # | Name            | Description                                                                                                                                                                                                                                                |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | RO              | Receiver Output: When DE/RE* (Receiver Enable) is LOW, the receiver is enabled (ON), if DO/RI $\geq$ DO*/RI* by 200 mV, RO will be HIGH. If DO/RI $\leq$ DO*/RI* by 200 mV, RO will be LOW. Additionally RO will be HIGH for OPEN (Non-terminated) inputs. |

| 2     | SR              | Slew Rate Control: A resistor connected to Ground controls the Driver Output rising and falling edge rates.                                                                                                                                                |

| 3     | DE/RE*          | Combined Driver and Receiver Output Enable: When signal is LOW the receiver output is enabled and the driver outputs are in TRI-STATE (OFF). When signal is HIGH, the receiver output is in TRI-STATE (OFF) and the driver outputs are enabled.            |

| 4     | DI              | Driver Input: When DE/RE* is HIGH, the driver is enabled, if DI is LOW, then DO/RI will be LOW and DO*/RI* will be HIGH. If DI is HIGH, then DO/RI is HIGH and DO*/RI* is LOW.                                                                             |

| 5     | GND             | Ground Connection                                                                                                                                                                                                                                          |

| 6     | DO/RI           | Driver Output/Receiver Input, 485 Bus Pin.                                                                                                                                                                                                                 |

| 7     | DO*/RI*         | Driver Output/Receiver Input, 485 Bus Pin.                                                                                                                                                                                                                 |

| 8     | V <sub>CC</sub> | Positive Power Supply Connection: Recommended operating range for V <sub>CC</sub> is +4.75V to +5.25V.                                                                                                                                                     |

### Table 1. DEVICE PIN DESCRIPTIONS

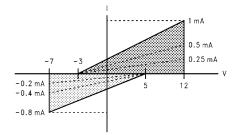

## Unit Load

A unit load for a RS-485 receiver is defined by the input current versus the input voltage curve. The gray shaded region is the defined operating range from -7V to +12V. The top border extending from -3V at 0 mA to +12V at +1 mA is defined as one unit load. Likewise, the bottom border extending from +5V at 0 mA to -7V at -0.8 mA is also defined as one unit load (see Figure 19). A RS-485 driver is capable of driving up to 32 unit loads. This allows upto 32 nodes on a single bus. Although sufficient for many applications, it is sometime desirable to have even more nodes. For example an aircraft that has 32 rows with 4 seats per row could benefit from having 128 nodes on one bus. This would allow signals to be transferred to and from each individual seat to 1 main station. Usually there is one or two less seats in the last row of the aircraft near the restrooms and food storage area. This frees the node for the main station.

The DS36C278, the DS36C279, and the DS36C280 all have ½ unit load and ¼ unit load (UL) options available. These devices will allow upto 64 nodes or 128 nodes guaranteed over temperature depending upon which option is selected. The ½ UL option is available in industrial temperature and the ¼ UL is available in commercial temperature.

First, for a  $\frac{1}{2}$  UL device the top and bottom borders shown in Figure 19 are scaled. Both 0 mA reference points at +5V and -3V stay the same. The other reference points are +12V at +0.5 mA for the top border and -7V at -0.4 mA for the bottom border (see Figure 19). Second, for a  $\frac{1}{4}$  UL device the top and bottom borders shown in Figure 19 are scaled also. Again, both 0 mA reference points at +5V and -3V stay the same. The other reference points at +5V and -3V stay the same. The other reference points are +12V at +0.25 mA for the top border and -7V at -0.2 mA for the bottom border (see Figure 19).

The advantage of the ½ UL and ¼ UL devices is the increased number of nodes on one bus. In a single master multi-slave type of application were the number of slaves exceeds 32, the DS36C278/279/280 may save in the cost of extra devices like repeaters, extra media like cable, and/or extra components like resistors.

The DS36C279 and DS36C280 have addition feature which offer more advantages. The DS36C279 has an automatic sleep mode function for power conscious applications. The DS36C280 has a slew rate control for EMI conscious applications. Refer to the sleep mode and slew rate control portion of the application information section in the corresponding datasheet for more information on these features.

Figure 19. Input Current vs Input Voltage Operating Range

FXAS

**NSTRUMENTS**

www.ti.com

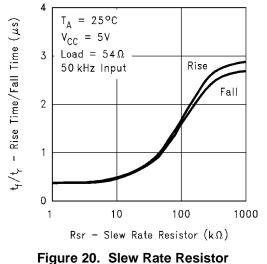

### **Slew Rate Control**

The DS36C280 features an adjustable slew rate control. This feature allows more control over EMI levels than tradition fixed edge rate devices. The slew rate control may be adjusted with or without any external components. The DS36C280 offers both low power ( $I_{CC}$  500 µA max) and low EMI for an RS-485 interface.

The slew rate control is located at pin two of the device and only controls the driver output edges. The slew rate control pin (SR) may be left open or shorted to ground, with or without a resistor. When the SR pin is shorted to ground without a resistor, the driver output edges will transition typically 350 ns. When the SR pin is left open, the driver output edges will transition typically 3  $\mu$ s. When the SR pin is shorted to ground with a resistor, the driver output edges will transition between 350 ns and 3  $\mu$ s depending on the resistor value. Refer to the slew rate versus resistor value curve in this datasheet for determining resistor values and expected typical slew rate value. Please note, when slowing the edge rates of the device will decrease the maximum data rate also.

vs Differential Rise/Rise/Fall Time

SNLS097C – JULY 2000-REVISED FEBRUARY 2013

#### 10 Submit Documentation Feedback

Copyright © 2000–2013, Texas Instruments Incorporated

## **REVISION HISTORY**

| Changes from Revision B (February 2013) to Revision C |                                                    |   |  |  |  |  |

|-------------------------------------------------------|----------------------------------------------------|---|--|--|--|--|

| •                                                     | Changed layout of National Data Sheet to TI format | 9 |  |  |  |  |

NSTRUMENTS

www.ti.com

**EXAS**

Page

## PACKAGING INFORMATION

| Orderable Device |          | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan | Lead/Ball Finish | MSL Peak Temp | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|----------|--------------|--------------------|------|----------------|----------|------------------|---------------|--------------|-------------------------|---------|

|                  | (1)      |              | Drawing            |      | uty            | (2)      | (6)              | (3)           |              | (4/5)                   |         |

| DS36C280M/NOPB   | OBSOLETE | SOIC         | D                  | 8    |                | TBD      | Call TI          | Call TI       | 0 to 70      | 36C28<br>0M             |         |

| DS36C280MX/NOPB  | OBSOLETE | SOIC         | D                  | 8    |                | TBD      | Call TI          | Call TI       | 0 to 70      | 36C28<br>0M             |         |

| DS36C280TM/NOPB  | OBSOLETE | SOIC         | D                  | 8    |                | TBD      | Call TI          | Call TI       | 0 to 70      | 36C28<br>0TM            |         |

| DS36C280TMX/NOPB | OBSOLETE | SOIC         | D                  | 8    |                | TBD      | Call TI          | Call TI       | 0 to 70      | 36C28<br>0TM            |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

5-Nov-2017

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

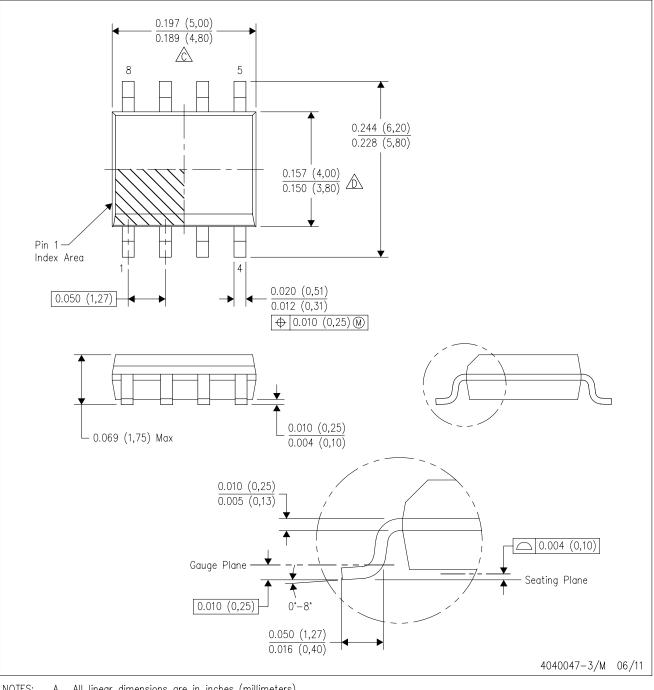

## **MECHANICAL DATA**

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- 🖄 Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.