# **Dual Output Driver**

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

UC1706 UC2706 UC3706

#### **FEATURES**

- Dual, 1.5A Totem Pole Outputs

- 40nsec Rise and Fall into 1000pF

- Parallel or Push-Pull Operation

- Single-Ended to Push-Pull Conversion

- High-Speed, Power MOSFET Compatible

- Low Cross-Conduction Current Spike

- Analog, Latched Shutdown

- Internal Deadband Inhibit Circuit

- Low Quiescent Current

- 5 to 40V Operation

- Thermal Shutdown Protection

- 16-Pin Dual-In-Line Package

- 20-Pin Surface Mount Package

#### DESCRIPTION

The UC1706 family of output drivers are made with a high-speed Schottky process to interface between low-level control functions and high-power switching devices - particularly power MOSFET's. These devices implement three generalized functions as outlined below.

First: They accept a single-ended, low-current digital input of either polarity and process it to activate a pair of high-current, totem pole outputs which can source or sink up to 1.5A each.

Second: They provide an optional single-ended to push-pull conversion through the use of an internal flip-flop driven by double-pulse-suppression logic. With the flip-flop disabled, the outputs work in parallel for 3.0A capability.

Third: Protection functions are also included for pulse-by-pulse current limiting, automatic deadband control, and thermal shutdown.

These devices are available in a two-watt plastic "bat-wing" DIP for operation over a 0°C to 70°C temperature range and, with reduced power, in a hermetically sealed cerdip for -55°C to +125°C operation. Also available in surface mount Q and L packages.

# TRUTH TABLE

|     | INV   | N.L    | OUT |

|-----|-------|--------|-----|

| 101 | H     | H. H.  | TIL |

|     | _LV.1 | HON    | Н   |

| 4   | H     | 00 / F |     |

|     | LIVI  | F CO   | LN  |

$\frac{\text{OUT} = \text{INV and N.I.}}{\text{OUT} = \text{INV or N.I.}}$

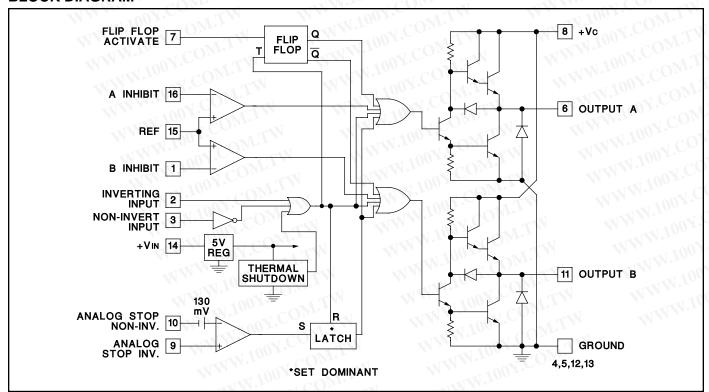

# **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| ABSOLUTE MAXIMUM R              | ATINGS                                   |            |

|---------------------------------|------------------------------------------|------------|

|                                 | NPkg                                     | JPkg       |

|                                 |                                          |            |

|                                 |                                          |            |

| Output Current (Each Output, So |                                          | MM 100X.Co |

|                                 | ±500mA                                   | ±500mA     |

|                                 |                                          |            |

|                                 |                                          |            |

|                                 | 5.5V                                     |            |

|                                 | Vin                                      |            |

|                                 | (See Note) 2W                            | 1\/\       |

| Power Dissipation at T (Leads/C | Case) = 25°C 5W                          | 2          |

| (See Note)                      | MAN ST COM                               | NNN.       |

|                                 | 55°C to                                  |            |

|                                 | 65°C to                                  |            |

| Lead Temperature (Soldering 1   | 0 Seconds)                               | 0°C        |

|                                 | ect to the four ground pins which mus    |            |

|                                 | e into, negative out of the specified tr |            |

| ingoing in our onto all poolity |                                          | an oonoon  |

Packaging sections of the Databook for thermal limitations and considerations of package.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

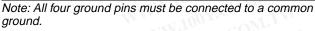

**CONNECTION DIAGRAMS**

#### DIL-16, SOIC-16 (TOP VIEW) J or N Package, DW Package B INHIBIT 16 A INHIBIT INV. INPUT **INHIBIT REF** 15 N.I. INPUT 14 VIN **GROUND GROUND** 13 **GROUND** 12 **GROUND** A OUTPUT **B OUTPUT** 11 FLIP/FLOP 10 STOP NON-INV. STOP INV. Vc 8

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for TA = -55°C to +125°C for the UC1706,  $-25^{\circ}$ C to  $+85^{\circ}$ C for the UC2706 and  $0^{\circ}$ C to  $+70^{\circ}$ C for the UC3706; VIN = VC = 20V. TA = TJ.

| PARAMETERS               | TEST CONDITIONS            | MIN           | TYP  | MAX  | UNITS |

|--------------------------|----------------------------|---------------|------|------|-------|

| VIN Supply Current       | VIN = 40V                  | TW            | 8    | 10   | mA    |

| Vc Supply Current        | Vc = 40V, Outputs Low      | III.          | 4    | 5    | mA    |

| Vc Leakage Current       | VIN = 0, VC = 30V, No Load | $0M_{T_{I}}$  | .05  | 0.1  | mA    |

| Digital Input Low Level  | 001. CM.TW WW. 100X.       | TIMO          |      | 0.8  | V     |

| Digital Input High Level | MAN TOOK!                  | 2.2           | N    |      | V     |

| Input Current            | VI = 0                     | $G_{O_{M_2}}$ | -0.6 | -1.0 | mA    |

| Input Leakage            | VI = 5V                    |               | .05  | 0.1  | mA    |

UC1706 UC2706 UC3706

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for  $TA = -55^{\circ}C$  to  $+125^{\circ}C$  for the UC1706,  $-25^{\circ}C$  to  $+85^{\circ}C$  for the UC2706 and  $0^{\circ}C$  to  $+70^{\circ}C$  for the UC3706; VIN = VC = 20V. TA = TJ.

| PARAMETERS              | TEST CONDITIONS                           | MIN                      | TYP         | MAX | UNITS |

|-------------------------|-------------------------------------------|--------------------------|-------------|-----|-------|

| Output High Sat., Vc-Vo | Io = -50mA                                | N                        |             | 2.0 | V     |

|                         | COM.                                      | -XXI                     |             |     |       |

| Output Low Sat., Vo     | Io = 50mA                                 |                          |             | 0.4 | V     |

| CO TW WWW.              | Io = 500mA                                | TW                       |             | 2.5 | V     |

| Inhibit Threshold       | VREF = 0.5V                               | 0.4                      |             | 0.6 | V     |

| COM.                    | VREF = 3.5V                               | 3.3                      |             | 3.7 | V     |

| Inhibit Input Current   | VREF = 0                                  | Dir                      | <b>–</b> 10 | -20 | μΑ    |

| Analog Threshold        | Vcm = 0 to 15V, for the UC2706 and UC3706 | 100                      | 130         | 160 | mV    |

| ON CONTRACTOR WINN      | Vcm = 0 to 15V, for the UC1706            | 80                       | 130         | 160 | mV    |

| Input Bias Current      | VcM = 0                                   | CON                      | -10         | -20 | μΑ    |

| Thermal Shutdown        | N. July COM.                              | $^{\circ}$ CO $_{N_{i}}$ | 155         |     | °C    |

# TYPICAL SWITCHING CHARACTERISTICS: VIN = VC = 20V, TA = 25°C. Delays measured to 10% output change.

| PARAMETERS                                 | TEST CONDITIONS                               | OUTPUT CL = |           | UNITS |    |

|--------------------------------------------|-----------------------------------------------|-------------|-----------|-------|----|

| From Inv. Input to Output:                 |                                               | open        | 1.0       | 2.2   | nF |

| Rise Time Delay                            | TW.100 COM.1                                  | 110         | 130       | 140   | ns |

| 10% to 90% Rise                            | WILLIAM WILLIAM                               | 20          | 40        | 60    | ns |

| Fall Time Delay                            | MILLION TO THE WAY                            | 80          | 90        | 110   | ns |

| 90% to 10% Fall                            | AMM. TON'COM. TAN MAN                         | 25          | 30        | 50    | ns |

| From N. I. Input to Output:                | MAN, Inc. COM.                                | NW.10       | N.CC      | )Mr.  | W  |

| Rise Time Delay                            | M. TAN. TOO. COM: I.                          | 120         | 130       | 140   | ns |

| 10% to 90% Rise                            | MM 100X.COM.TW                                | 20          | 40        | 60    | ns |

| Fall Time Delay                            | WWW. 100Y. CO. TW                             | 100         | 120       | 130   | ns |

| 90% to 10% Fall                            | MMM. T. COM.                                  | 25          | 30        | 50    | ns |

| Vc Cross-Conduction Current Spike Duration | Output Rise                                   | 25          | 1.10      | of CO | ns |

|                                            | Output Fall                                   | 0           | $N^{100}$ | 10(   | ns |

| Inhibit Delay                              | Inhibit Ref. = 1V, Inhibit Inv. = 0.5 to 1.5V | 250         | X 10      | 01.   | ns |

| Analog Shutdown Delay                      | Stop Non-Inv. = 0V, Stop Inv. = 0 to 0.5V     | 180         | N A       | OUY.  | ns |

## **CIRCUIT DESCRIPTION**

#### **Outputs**

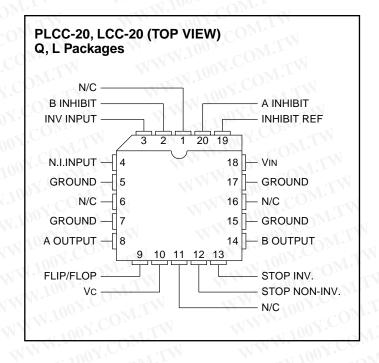

The totem-pole outputs have been designed to minimize cross-conduction current spikes while maximizing fast, high-current rise and fall times. Current limiting can be done externally either at the outputs or at the common Vc pin. The output diodes included have slow recovery and should be shunted with high-speed external diodes when driving high-frequency inductive loads.

#### Flip/Flop

Grounding pin 7 activates the internal flip-flop to alternate the two outputs. With pin 7 open, the two outputs operate simultaneously and can be paralleled for higher current operation. Since the flip-flop is triggered by the digital input, an off-time of at last 200nsec must be provided to allow the flip/flop to change states. Note that the circuit logic is configured such that the "OFF" state is defined as the outputs low.

#### **Digital Inputs**

With both an inverting and non-inverting input available, either active-high or active-low signals may be accepted. These are true TTL compatible inputs—the threshold is approximately 1.2V with no hysteresis; and external pull-up resistors are not required.

#### **Inhibit Circuit**

Although it may have other uses, this circuit is included to eliminate the need for deadband control when driving relatively slow bipolar power transistors. A diode from each inhibit input to the opposite power switch collector will keep one output from turning-on until the other has turned-off. The threshold is determined by the voltage on pin 15 which can be set from 0.5 to 3.5V. When this circuit is not used, ground pin 15 and leave 1 and 16 open.

UC1706 UC2706 UC3706

# **CIRCUIT DESCRIPTION (cont.)**

## **Analog Shutdown**

This circuit is included to get a latched shutdown as close to the outputs as possible, from a time standpoint. With an internal 130mV threshold, this comparator has a common-mode range from ground to (VIN-3V). When not used, both inputs should be grounded. The time required for this circuit to latch is inversely proportional to the amount of overdrive but reaches a minimum of 180nsec. As with the flip-flop, an input off-time of at least 200nsec is required to reset the latch between pulses.

# **Supply Voltage**

With an internal 5V regulator, this circuit is optimized for

use with a 7 to 40V supply; however, with some slight response time degradation, it can also be driven from 5V. When VIN is low, the entire circuit is disabled and no current is drawn from Vc. When combined with a UC1840 PWM, the Driver Bias switch can be used to supply VIN to the UC1706. VIN switching should be fast as if Vc is high, undefined operation of the outputs may occur with VIN less than 5V.

#### **Thermal Considerations**

Should the chip temperature reach approximately 155°C, a parallel, non--inverting input is activated driving both outputs to the low state.

#### **APPLICATIONS**

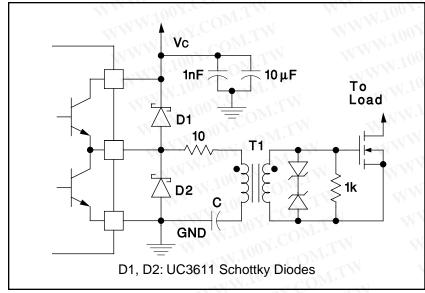

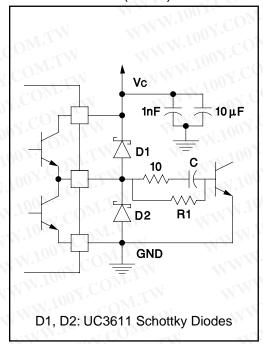

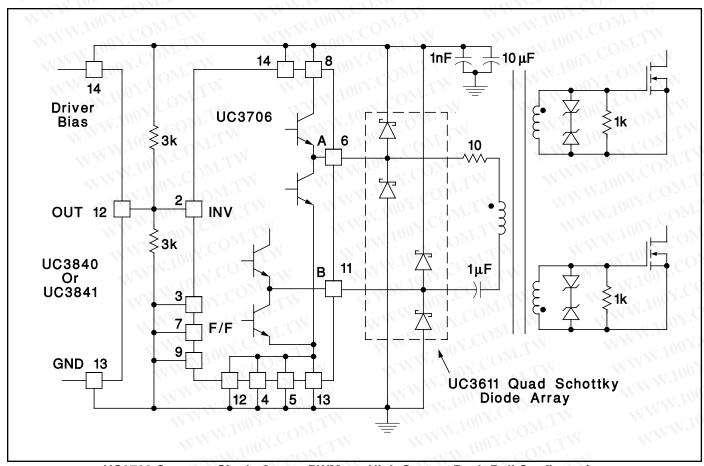

**Power MOSFET Drive Circuit**

Power MOSFET Drive Circuit Using Negative Bias Voltage and Level Shifting to Ground Referenced PWMs

**Transformer Coupled MOSFET Drive Circuit**

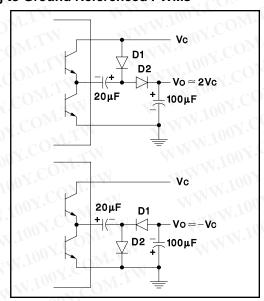

**Charge Pump Circuits**

# APPLICATIONS (cont'd)

**Power Bipolar Drive Circuit**

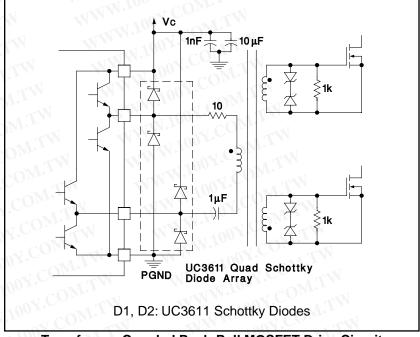

**Transformer Coupled Push-Pull MOSFET Drive Circuit**

UC3706 Converts Single Output PWMs to High Current Push-Pull Configuration

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products, www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Copyright © 2001, Texas Instruments Incorporated