# HM6148HLP Series

### 1024-word × 4-bit High Speed Static CMOS RAM

#### **■** FEATURES

- Low Power Standby and Low Power Operation;

Standby: 5μW (typ.), Operation: 175mW (typ.)

- Fast Access Time: 45/55ns (max)

- Capability of Battery Back Up Operation

- Single 5V Supply

- Completely Static RAM: No Clock or Timing Strobe Required

- No Peak Power-On Current

- No Change of tacs with Short Deselected Time

- Equal Access and Cycle Time

- Directly TTL Compatible: All Inputs and Outputs

- Three State Output

- Pin-Out Compatible with Intel 2148H

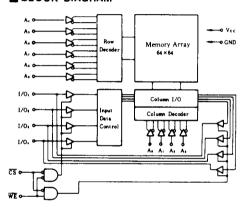

#### **■ BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                   | Symbol | Ratings      | Unit |

|------------------------|--------|--------------|------|

| Terminal Voltage *     | V 7    | -0.5 to +7.0 | ٧    |

| Power Dissipation      | Pτ     | 1.0          | W    |

| Operating Temperature  | T.,.   | 0 to +70     | ·c   |

| Storage Temperature    | Tite   | -55 to +125  | ·c   |

| Storage Temperature ** | T,     | -10 to +85   | .c   |

\* with respect to GND.  $V_{IL,n,n} = -3.5 \text{ V (Pulse width } \pm 20 \text{ ns.)}$

\* \* under bias.

#### TRUTH TABLE

| C S | WE | Mode         | Vcc Current | I/O Pin | Reference Cycle  |

|-----|----|--------------|-------------|---------|------------------|

| Н   | ×  | Not selected | Isa, Isa,   | High Z  |                  |

| L   | н  | Read         | Icc         | Dout    | Read Cycle 1, 2  |

| L   | L  | Write        | Icc .       | Din     | Write Cycle 1, 2 |

勝 特 力 材 料 886-3-5773766 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

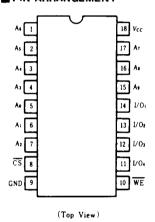

#### **■ PIN ARRANGEMENT**

## ■ RECOMMENDED DC OPERATING CONDITIONS (Ta-0 to +70°C)

| Item           | Symbol | min           | typ | max | Unit |

|----------------|--------|---------------|-----|-----|------|

| Supply Voltage | Vcc    | 4.5           | 5.0 | 5.5 | v    |

|                | GND    | 0             | 0   | 0   | v    |

| Input Voltage  | VIH    | 2.2           | -   | 6.0 | v    |

| Input voitage  | VIL    | <b>-0.5 *</b> |     | 0.8 | v    |

<sup>+ -3.0</sup> V (Pulse width 20ns)

## **TITLE 10.1** DC AND OPERATING CHARACTERISTICS (Ta=0 to +70°C, $Vcc=5V\pm10\%$ , GND=0V)

| Parameter                          | Symbol          | Test Conditions                                                                     | min      | typ* | max | Unit |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------|----------|------|-----|------|

| Input Leakage Current              | I <sub>L1</sub> | Vcc-max, VGND to Vcc                                                                | _        | _    | 2.0 | μA   |

| Output Leakage Current             | ILO             | CS-VIN, VINO-GND to Vcc                                                             | _        |      | 2.0 | μΑ   |

| Operating Power Supply Current (1) | Icc             | $\overline{CS} = V_{IL}, I_{I \times 0} = 0 \text{mA}$                              | <u> </u> | 35   | 80  | mA   |

| Operating Power Supply Current (2) | Icci            | min. cycle, CS - VIL, IIVO - 0mA                                                    | _        | 50   | 100 | mA.  |

| Standby Power Supply Current (1)   | Is.             | CS - VIN                                                                            | T =      | 5    | 20  | mA   |

| Standby Power Supply Current(2)    | Isat            | $\overline{CS} \ge V_{CC} - 0.2V$ , $V_{IN} \le 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$ | _        | 1    | 50  | μA   |

| Output Low Voltage                 | Vol             | Io1 - 8mA                                                                           | T -      | _    | 0.4 | v    |

| Output High Voltage                | Von             | Ion 4.0mA                                                                           | 2.4      | _    |     | v    |

<sup>\*</sup> Typical limits are at  $V_{cc}=5.0$ V, Ta=+25°C and specified loading.

### **TAPACITANCE** $(Ta=25 \, ^{\circ}\text{C}, f=1 \, \text{MHz})$

| Item                     | Symbol | Test Conditions | typ | mex | Unit |

|--------------------------|--------|-----------------|-----|-----|------|

| Input Capacitance        | C.,    | V., -0V         | -   | 5   | pF   |

| Input/Output Capacitance | C1.0   | V1.0-0V         | -   | 7   | pF   |

Note). This parameter is sampled and not 100% tested.

## $\blacksquare$ AC CHARACTERISTICS ( $V_{cc} = 5 \text{V} \pm 10\%$ , Ta = 0 to +70 °C)

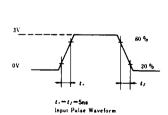

### ●RISE/FALL TIME

| Item            | Symbol    | min | typ | max | Unit |

|-----------------|-----------|-----|-----|-----|------|

| Input Rise Time | t.        | -   | 5   | 100 | ns   |

| Input Fall Time | $\iota_j$ | _   | 5   | 100 | ns   |

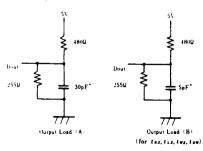

#### **•AC TEST CONDITIONS**

Input pulse levels: GND to 3.0V Input rise and fall times: 5ns

Input and Output timing reference levels: 1.5V

Output load: See Figure

\* Including scope & jig.

## **EAC CHARACTERISTICS** (Ta-0 to $+70^{\circ}$ C, $V_{cc}-5V\pm10\%$ , unless otherwise noted.) • READ CYCLE

| •.                                   | Symbol            | HM6148HLP-45 |     | HM6148HLP-55 |     |      |

|--------------------------------------|-------------------|--------------|-----|--------------|-----|------|

| Item                                 |                   | min          | max | min          | max | Unit |

| Read Cycle Time                      | lac .             | 45           | _   | 55           | _   | ns   |

| Address Access Time                  | LAA               | -            | 45  | _            | 55  | ns   |

| Chip Select Access Time              | LACS              | _            | 45  | _            | 55  | ns   |

| Output Hold from Address Change      | ton               | 5            |     | 5            | _   | ns   |

| Chip Selection to Output in Low Z    | t <sub>LZ</sub> * | 10           | _   | 10           | _   | ns   |

| Chip Deselection to Output in High Z | tuz*              | 0            | 20  | 0            | 20  | ns   |

| Chip Selection to Power Up Time      | tpu               | 0            | _   | 0            | _   | ns   |

| Chip Deselection to Power Down Time  | t <sub>PD</sub>   | _            | 30  | -            | 30  | ns   |

<sup>\*</sup> Transition is measured ±500mV from steady state voltage with Load (B). This parameter is sampled and not 100% tested. At any temperature and voltage condition fuz max is less than faz min.

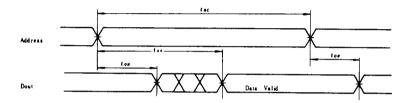

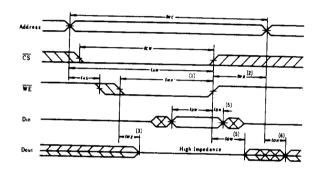

## ●TIMING WAVEFORM OF READ CYCLE NO.1 (1)(2)

## ● TIMING WAVEFORM OF READ CYCLE NO.2 (1)(3)

Notes) 1. WE is High for Read Cycle.

Device is continuously selected, CS = V<sub>i.t.</sub>

Address Valid prior to or coincident with CS transition Low.

#### • WRITE CYCLE

| Item                                             | Symbol | HM6148HLP-45 |     | HM6148HLP-55 |     | T            |  |

|--------------------------------------------------|--------|--------------|-----|--------------|-----|--------------|--|

|                                                  |        | min          | max | min          | max | Unit         |  |

| Write Cycle Time                                 | fwc .  | 45           | _   | 55           |     | <del> </del> |  |

| Chip Selection to End of Write                   | tor    | 40           |     | 50           |     | ns           |  |

| Address Valid to End of Write                    | l av   | 40           |     | 50           |     | ns           |  |

| Address Setup Time                               | las    | 0            |     | 0            |     | ns           |  |

| Write Pulse Width                                | twe    | 35           |     | 40           |     | ns           |  |

| Write Recovery Time                              | ive    | 5            |     |              |     | ns           |  |

| Data Valid to End of Write                       | t pw   | 20           |     | 5            |     | ns           |  |

| Data Hold Time                                   | I DH   | 0            |     | 20           |     | ns           |  |

| Write Enabled to Output in High Z.               |        |              |     | 0            |     | ns           |  |

| Output Active from End of Write.                 | twz    | 0            | 15  | 0            | 20  | ns           |  |

| Transition is measured ±500 mV from steady state | tow    | 0            | -   | 0            | _   | ns           |  |

$<sup>\</sup>Phi$  Transition is measured  $\pm 500\,\text{mV}$  from steady state voltage with Load B. This parameter is sampled and not 100% tested.

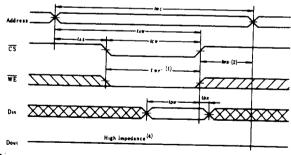

# ullet TIMING WAVEFORM OF WRITE CYCLE NO.1 ( $\overline{WE}$ Controlled)

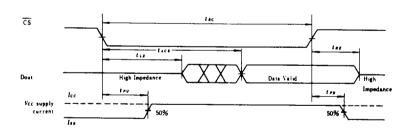

## • TIMING WAVEFORM OF WRITE CYCLE NO.2 (CS Controlled)

Notes of Timing Waveform of Write:

- 1. A write occurs during the overlap of a low  $\overline{CS}$  and a low  $\overline{WE}$  ( $t_{\pi\pi}$ ) 2. Let as measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high to the end of write cycle.

- for as measured from the earlier of CS or WE going high to the end of write cycle.

During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

If the CS bw transition occurs samukaneously with the WE low transition or after the WE transition, the output buffers remain in a high impedance state.

If CS is low during this period, I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.

Dout is the same phase of write data of this write cycle.

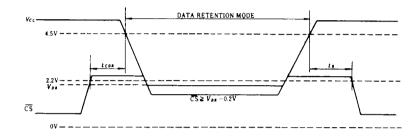

### ■LOW Vcc DATA RETENTION CHARACTERISTICS (0°C ≤ Ta≤70°C)

| Parameter                            | Symbol          | Test Conditions                                                         | min     | typ | max         | Unit |

|--------------------------------------|-----------------|-------------------------------------------------------------------------|---------|-----|-------------|------|

| Vcc for Data Retention               | V <sub>DA</sub> |                                                                         | 2.0     | _   | _           | v    |

| Data Retention Current               | Iccor           | $\overline{CS} \ge V_{cc} - 0.2V$ $V_{cc} \ge V_{cc} - 0.2V \text{ or}$ | _       | _   | 30°<br>20** | μA   |

| Chip Deselect to Data Retention Time | ICDA            | 0V ≤ V.,≤0.2V                                                           | 0       | _   | _           | ns   |

| Operation Recovery Time              | I R             |                                                                         | tnc (1) | _   | _           | ns   |

Note) 1, tac-Read Cycle Time.

• Vcc-3.0V • • Vcc-2.0V

### ●LOW Vcc DATA RETENTION WAVEFORM