### 512K SPI Low Power Serial SRAM

| Part Number | Vcc Range  | MHz (max) | Density | Temp. Ranges | Package |

|-------------|------------|-----------|---------|--------------|---------|

| IP12B512C-T | 2.7 - 3.6V | 20        | 512Kb   | -20℃ to +70℃ | TSSOP-8 |

| IP12B512I-T | 2.7 - 3.6V | 20        | 512Kb   | -40℃ to +85℃ | TSSOP-8 |

#### Features:

- Max Clock 20MHz

- SPI-Compatible Interface (Mode0 and Mode3)

- Low-Power CMOS Technology:

- Operating current: max. 2mA @ 1MHz

- Standby current: typ. 10uA @ +25℃

- 65.536 x 8-bit Organisation

- 32-Byte Page

- Hold pin for pausing communication

- Sequential Read/Write

- Flexible operating modes

- Byte read and write (BYTE)

- Page mode (PAGE)

- Pagestart Sequential mode (PSEQ)

- Virtual chip mode (VRTM)

- Infinite read/writes to memory array

- Temperature range

- -20℃ to +70℃ (Consumer grade)

- -40℃ to +85℃ (Industrial grade)

- RoHS compliant package

# 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### **Description:**

The IPSiLog Semiconductor GmbH serial SRAM family IP12xxxxx includes several integrated memory devices including this 512Kb serially accessed Static Random Access Memory, internally organized as 64K words by 8 bits each. The devices are designed and fabricated using state of the art advanced CMOS technology to provide both high-speed performance and low power. The devices operate with a single chip select (/CS) input and are accessed by a simple serial interface that is SPI-compatible. A single data in and data out line is used along with a clock to access data within the devices. The IP12xxxxx devices include a /HOLD pin that allows communication with the device to be paused without deselecting the device. While paused, input transitions except /CS pin will be ignored. The devices can operate over a temperature range of -20°C to +70°C (Consumer grade) and -40°C to +85°C (Industrial grade), both are available in space-saving 8-lead TSSOP package.

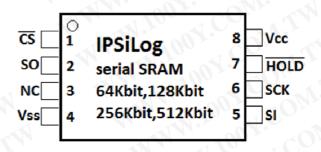

#### **Pin Function Table**

| Pin Name  | Pin Function       |

|-----------|--------------------|

| <u>CS</u> | Chip Select Input  |

| SO        | Serial data Output |

| NC        | 1                  |

| Vss       | Ground             |

| SI        | Serial data Input  |

| SCK       | Serial Clock Input |

| HOLD      | Hold Input         |

| Vcc       | Supply Voltage     |

#### **Package Outline**

# **Functional pin description**

| Pin Name | Pin Function       |        | Functional pin description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cs       | Chip Select Input  | Input  | A low level selects the device and a high level puts the device in standby mode. If /CS is brought high (device deselected), SO goes to high-impedance state. /CS must be driver low after power-up prior to any sequence being started.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| so       | Serial data Output | Output | Data is shifted out bit by bit after each falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC       | 1 1 1              | J «    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Vss      | Ground             |        | VSS is the reference for the VCC supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SI       | Serial data Input  | Input  | Receives instructions, addresses and data, latched on the rising edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCK      | Serial Clock Input | Input  | Synchronizes all activities between the SRAM and controller. All incoming addresses, data and instructions are latched on the rising edge of SCK. Data out is updated on SO after the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HOLD     | Hold Input         | Input  | A high level is required for normal operation. Once the device is selected and a serial sequence is started, this input may be taken low to pause serial communication without resetting the serial sequence. The pin must be brought low while SCK is low for immediate use. If SCK is not low, the Hold function will not be invoked until the next SCK high to low transition. The device must remain selected during this sequence. So is high-impedance during the Hold time and SI and SCK are ignored. To resume operations, /HOLD must be pulled high while the SCK pin is low. Lowering the /HOLD input at any time will take the SO output to high-impedance. The Hold functionality can be disabled by bit0 of the STATUS register. |

| Vcc      | Supply Voltage     | N.L    | During all operations, VCC must be held stable and within the specified valid range: VCC(min) to VCC(max).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

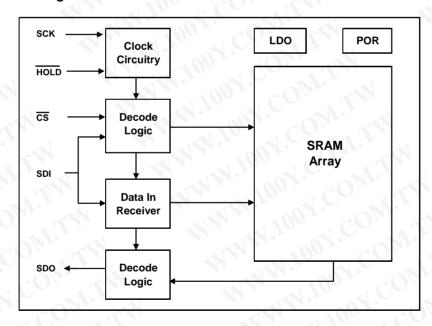

# **Functional Block Diagram**

#### **Absolute Maximum Ratings †**

| Vcc                                    | 4.4V (for IP12B512x) |

|----------------------------------------|----------------------|

| All inputs and outputs relative to Vss | 0.3V to Vcc +0.3V    |

| Storage temperature                    |                      |

| Operating temperature                  |                      |

| Operating temperature                  |                      |

| Soldering temperature and time         |                      |

| ESD protection on all pins             | 2kV                  |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside those indicated in the operating section of this specification, is not implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

# **Operating Characteristics (Over Specified Temperature Range)**

| Item                   | Symbol | Min.      | Тур           | Max       | Unit | Test Condition                        |

|------------------------|--------|-----------|---------------|-----------|------|---------------------------------------|

| Supply Voltage         | Vcc    | 2.7       | 3.0           | 3.6       | V    | IP12B512x-T                           |

| Input High Voltage     | VIH    | 0.7 * Vcc |               | Vcc +0.3  | V    | 100 CD, 41                            |

| Input Low Voltage      | VIL    | -0.3      | (             | 0.2 * Vcc | V    | · · · · · · · · · · · · · · · · · · · |

| Output High Voltage    | VOH    | Vcc - 0.5 |               |           | V    | IOH = -0.4mA                          |

| Output Low Voltage     | VOL    | 1         | - <del></del> | 0.2       | V    | IP12B512x-T, IOL = 1.0mA              |

| Input Leakage Current  | ILH    | ) > <     | 17-           | +- 0.5    | uA   | CS = Vcc, Vin =0 to Vcc               |

| Output Leakage Current | ILO    |           | ,-            | +- 0.5    | uA   | CS = Vcc, Vout =0 to Vcc              |

| Read/Write             | lcc1   |           |               | 2         | mΑ   | F = 1MHz, lout = 0                    |

| Operating Current      | lcc2   |           | )             | 7         | mA   | F = 10MHz, lout = 0                   |

|                        | lcc3   |           |               | 12        | mΑ   | F = fmax, lout = 0                    |

| Standby Current        | ISB1   | 1         | 10 Note1      | 15        | uA   | CS = Vcc , Vin = Vss or Vcc @25℃      |

|                        | ISB2   | ·         | // E.         | 150       | uA   | CS = Vcc , Vin = Vss or Vcc @85℃      |

| Input Capacitance      | CIN    | 1         |               | 6 Note2   | pF   | Vin = 0V, F = 1MHz, Ta = 25℃          |

| I/O Capacitance        | CIO    |           | 22-           | 6 Note2   | pF   | Vin = 0V, F = 1MHz, Ta = 25℃          |

Note1: Typical values are measured at Vcc=VccTyp and 25℃ and are not 100% tested

Note2: Characterized value, not tested in production

# **Timing test conditions**

| Item                                     |                      |

|------------------------------------------|----------------------|

| Input Pulse Level                        | 0.1* Vcc to 0.9* Vcc |

| Input Rise and Fall Time                 | 5ns                  |

| Input and Output Timing Reference Levels | 0.5* Vcc             |

| Output Load                              | CL = 100pF           |

| Operating Temperature (IP12B512C)        | -20℃ to +70℃         |

| Operating Temperature (IP12B512I)        | -40℃ to +85℃         |

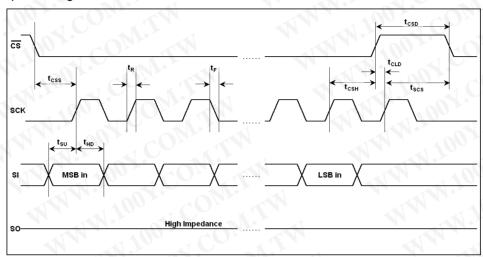

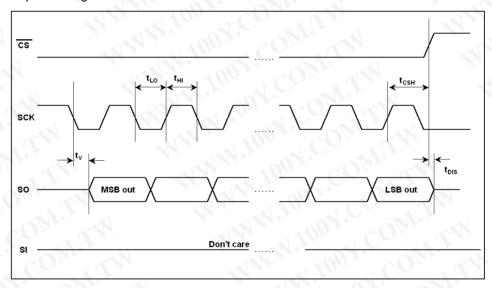

# Timing (over specified temperature range)

| Item                        | Symbol | Min. | Max. | Unit | Test Condition |

|-----------------------------|--------|------|------|------|----------------|

| Clock Frequency             | fCLK   |      | 20   | MHz  | Vcc = 3.0V     |

| Clock Rise Time             | tR     | 44   | 2    | us   |                |

| Clock Fall Time             | tF     | W    | 2    | us   |                |

| Clock High Time             | tHI    | 25   |      | ns   |                |

| Clock Low Time              | tLO    | 25   |      | ns   |                |

| Clock Delay Time            | tCLD   | 25   |      | ns   | 10,            |

| CS Setup Time               | tCSS   | 25   |      | ns   |                |

| CS Hold Time                | tCSH   | 50   | 177  | ns   |                |

| CS Disable Time             | tCSD   | 25   |      | ns   |                |

| SCK to CS                   | tSCS   | 5    |      | ns   | 100            |

| Data Setup Time             | tSU    | 10   |      | ns   | W. Ohr.        |

| Data Hold Time              | tHD    | 10   | 4-1- | ns   | 1              |

| Output Valid From Clock Low | tV     |      | 25   | ns   |                |

| Output Hold Time            | tHO    | 0    |      | ns   | 41 0           |

| Output Disable Time         | tDIS   | N    | 20   | ns   | 100 3.         |

| HOLD Setup Time             | tHS    | 10   | <    | ns   |                |

| HOLD Hold Time              | tHH    | 10   |      | ns   | 100            |

| HOLD Low to Output High-Z   | tHZ    | 10   |      | ns   |                |

| HOLD High to Output Valid   | tHV    |      | 50   | ns   | 100            |

# Serial Input Timing

# Serial Output Timing

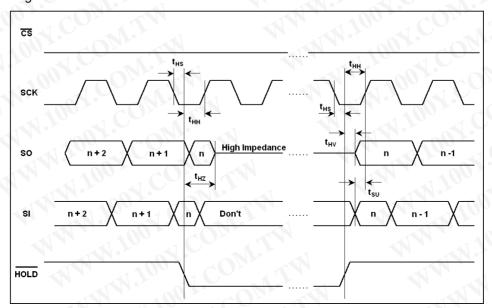

# Hold timing

### **Description of Functional Operation**

#### **Basic Operation**

The 512Kb serial SRAM is designed to interface directly with a standard 4wire Serial Peripheral Interface (SPI) implemented in many standard micro-controllers. If the device has no SPI-Hardware interface, the necessary protocol can be applied using standard I/O-port by programming (Software-SPI). The serial SRAM contains an 8-bit instruction register and is accessed via the SI pin. The /CS pin must be low and the /HOLD pin must be high for the entire operation. Data is clocked in, starting on the first rising edge of SCK after /CS goes low. If the clock line is shared by several devices, the user can assert the /HOLD input and put the device into a Hold mode. After releasing the /HOLD pin, the operation will resume from the point where it was held. The transfer sequence for all instructions, addresses and data is MSB first, LSB last.

#### Instruction Set

| Instruction Name | Instruction Format (binary) | Instruction Format (hex) | Description                                     |

|------------------|-----------------------------|--------------------------|-------------------------------------------------|

| READ             | 0000 0011                   | 0x03                     | Read memory data beginning at selected address  |

| WRITE            | 0000 0010                   | 0x02                     | Write memory data beginning at selected address |

| RDSR             | 0000 0101                   | 0x05                     | Read status register                            |

| WRSR             | 0000 0001                   | 0x01                     | Write status register                           |

| RDMI             | 0000 1110                   | 0x0E                     | Read Memory Size                                |

#### **READ Operations**

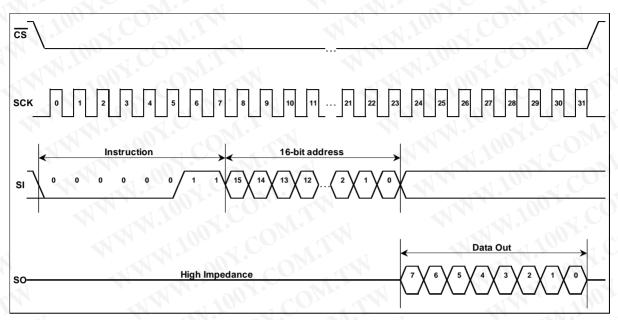

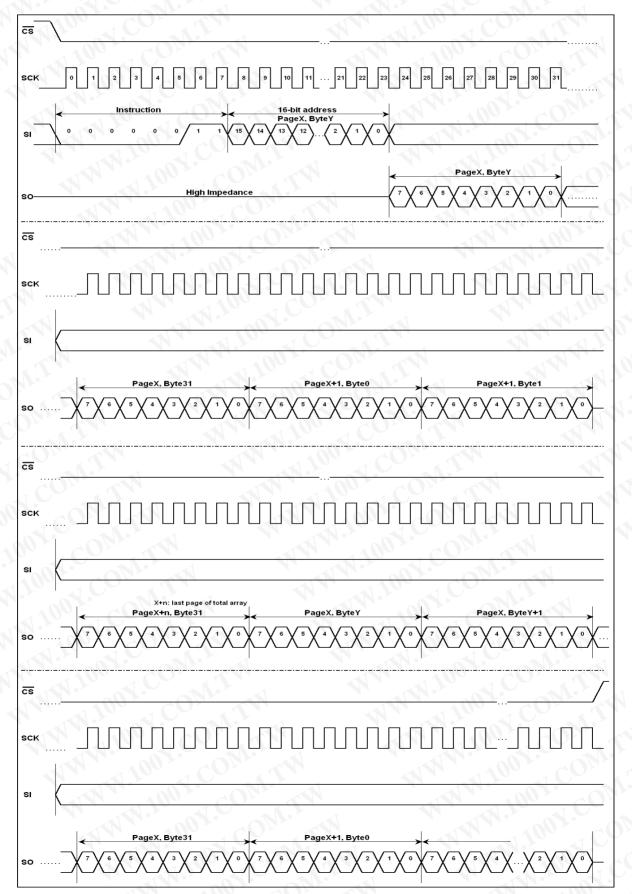

The serial SRAM READ is selected by pulling /CS low. First, the 8-bit READ instruction is transmitted to the device followed by the 16-bit address with the first bit as MSB. After the READ instruction and addresses are sent, the data stored at that address in memory is shifted out on the SO pin after the output valid time from the clock edge.

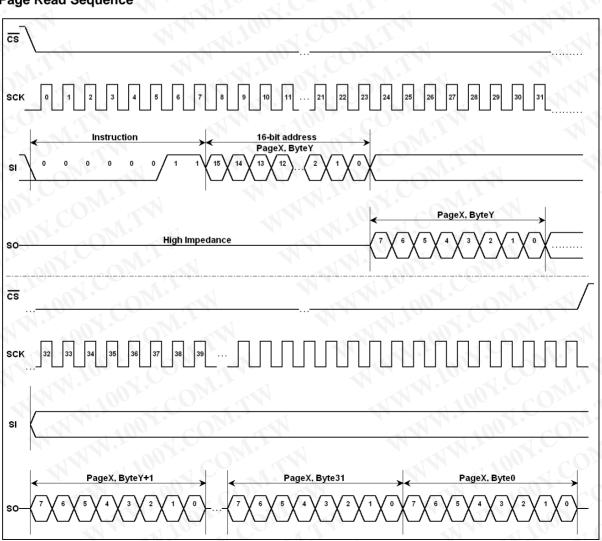

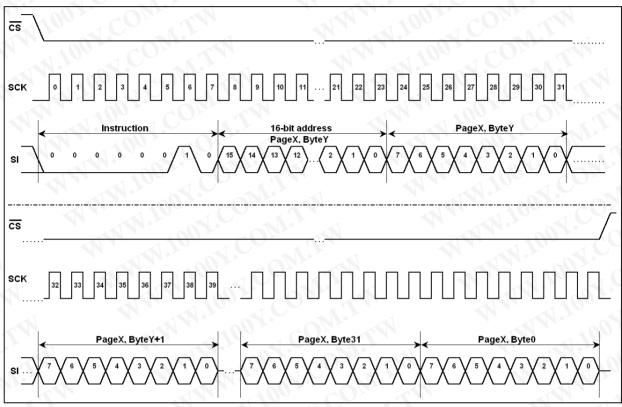

If operating in page mode, after the initial byte of data is shifted out, the data stored at the next memory location on the page can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each byte of data is read out. This can be continued for the entire page length of 32 bytes. At the end of the page, the addresses pointer wraps back to the 0 byte address within the page and the operation can be continuously looped over the 32 bytes of the same page.

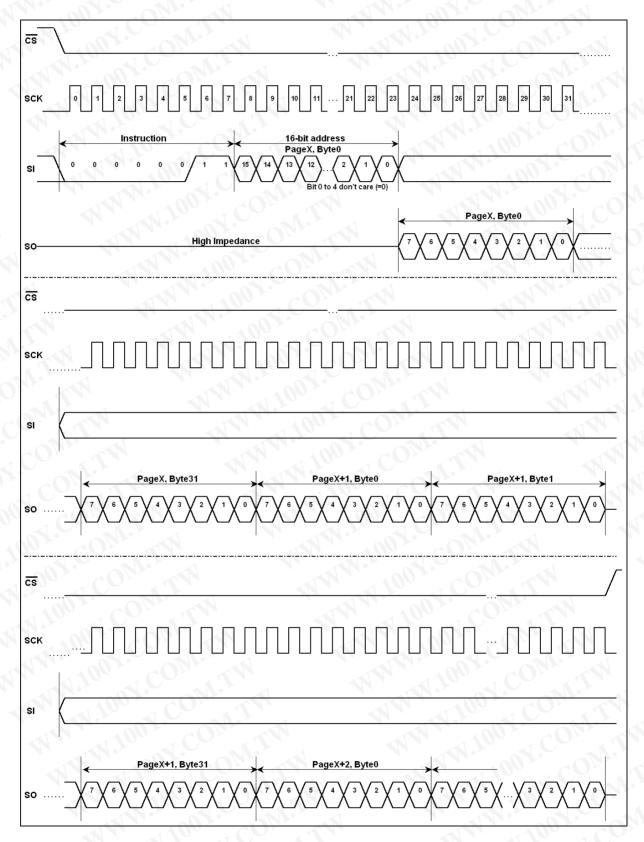

If operating in pagestart sequential (PSEQ) mode, the operation is always starting at the address 00h of the selected page by default. After the initial byte of data is shifted out, the data stored at the next memory location can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each byte of data is read out. This can be continued for the entire array and when the highest address is reached (FFFFh), the address counter wraps to the address 0000h. This allows the pagestart sequential (PSEQ) read cycle to be continued indefinitely. All READ operations are terminated by pulling /CS high.

If operating in virtual chip (VRTM) mode, after the initial byte of data is shifted out, the data stored at the next memory location can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each byte of data is read out. This can be continued for the entire array and when the highest address is reached (FFFFh), the address counter wraps to the address that was selected as the starting address of the virtual chip command. This allows the virtual chip (VRTM) read cycle to be continued indefinitely within the selected start-address and the highest address of the full array. All READ operations are terminated by pulling /CS high.

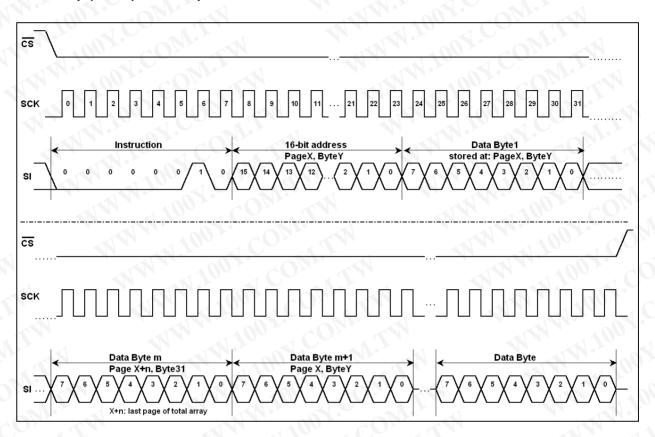

# **Byte Read Sequence**

# Page Read Sequence

# Pagestart Sequential (PSEQ) Read Sequence

# Virtual Chip (VRTM) Read Sequence

#### **Write Operations**

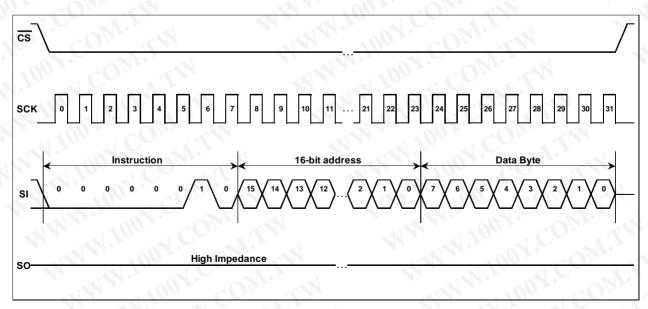

The serial SRAM WRITE is selected by enabling /CS low. First, the 8-bit WRITE instruction is transmitted to the device followed by the 16-bit address with the first bit as MSB. After the WRITE instruction and addresses are sent, the data to be stored in memory is shifted in on the SI pin.

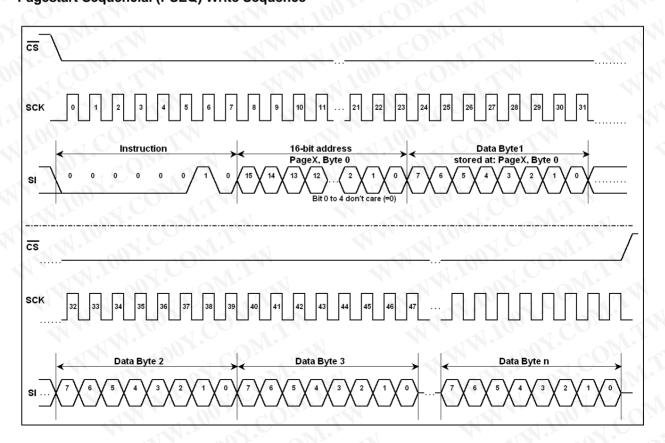

If operating in page mode, after the initial byte of data is shifted in, additional data bytes can be written as long as the address requested is sequential on the same page. Simply write the data on SI pin and continue to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each byte of data is written in. This can be continued for the entire page length of 32 bytes long. At the end of the page, the addresses pointer will be wrapped to the 0 byte address within the page and the operation can be continuously looped over the 32 bytes of the same page. The new data will replace data already stored in the memory locations.

If operating in pagestart sequencial (PSEQ) mode, the operation is always starting at the address 00h of the selected page by default. After the initial byte of data is shifted in, additional data bytes can be written to the next sequential memory locations by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each byte of data is read out. This can be continued for the entire array and when the highest address is reached (FFFFh), the address counter wraps to the address 0000h. This allows the pagestart sequencial (PSEQ) write cycle to be continued indefinitely. Again, the new data will replace data already stored in the memory locations.

If operating in virtual chip (VRTM) mode, after the initial byte of data is shifted in, additional data bytes can be written to the next sequential memory locations by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each byte of data is read out. This can be continued for the entire array and when the highest address is reached (FFFFh), the address counter wraps to the address that was selected as the starting address of the virtual chip command. This allows the virtual chip write cycle to be continued indefinitely within the selected start-address and the highest address of the full array. Again, the new data will replace data already stored in the memory locations.

All WRITE operations are terminated by pulling /CS high.

#### **Byte Write Sequence**

# Page Write Sequence

# Pagestart Sequencial (PSEQ) Write Sequence

# Virtual chip (VRTM) Write Sequence

#### Status register

| Bit 7 | Bit 6 | Bit 5                      | Bit 4        | Bit 3      | Bit 2            | Bit 1      | Bit 0 |           |

|-------|-------|----------------------------|--------------|------------|------------------|------------|-------|-----------|

| МС    | DDE   | Reserved 0                 | Reserved 0   | Reserved ( | Reserved C       | Reserved 0 | HOLD  |           |

|       |       |                            |              |            |                  |            |       |           |

| 0     | 0     | = Byte Mode                | e (default)  | 0          | = Hold (default) |            |       |           |

| 0     | 1     | = Virtual chip Mode (VRTM) |              |            |                  |            |       | = No Hold |

| 1     | 0     | = Page Mod                 | le           |            |                  | 7          |       |           |

| 11    | 1     | = Pagestart                | Sequencial ( | PSEQ) Mod  | е                |            |       |           |

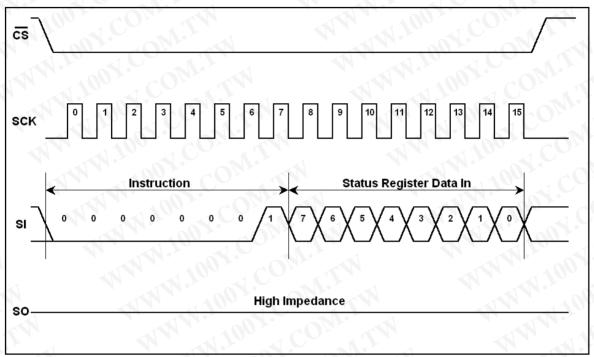

# WRITE Status Register Instruction (WRSR)

This instruction provides the ability to write the status register and select among several operating modes. Several of the register bits must be set to a low '0' if any of the other bits are written. The timing sequence to write to the status register is shown below, followed by the organization of the status register.

# **Write Status Register Sequence**

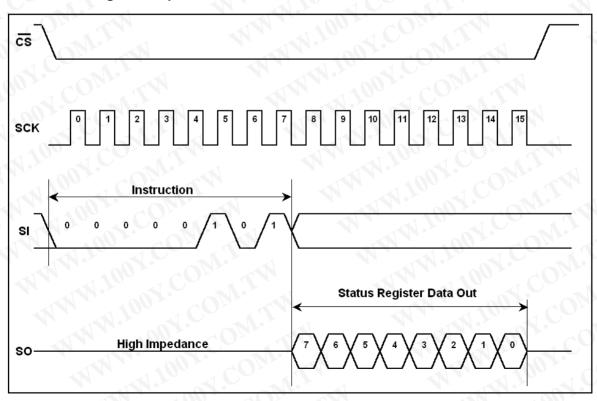

READ Status Register Instruction (RDSR)

This instruction provides the ability to read the Status register. The register may be read at any time by performing the following timing sequence.

## **READ Status Register Sequence**

# Memory size register

| 10,     | Bit 0 | Bit 1  | Bit 2 | Bit 3 | Bit 4    | Bit 5    | Bit 6    | Bit 7    |

|---------|-------|--------|-------|-------|----------|----------|----------|----------|

|         |       | y size | Memor |       | Reserved | Reserved | Reserved | Reserved |

|         | read  | read   | read  | read  | read     | read     | read     | read     |

| 64Kbit  | 0     | 0      | 0     | 0     |          |          |          |          |

| 128Kbit | 100   | 0      | 0     | 0     |          |          |          |          |

| 256Kbit | 0     | 1      | 0     | 0     |          |          |          |          |

| 512Kbit | 1     | 1      | 0     | 0     |          |          |          |          |

**READ Memory size Register Instruction (RDMI)**This instruction provides the ability to read the Memory size register. The register may be read at any time by performing the following timing sequence.

## **READ Memory size Register Sequence**

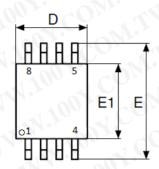

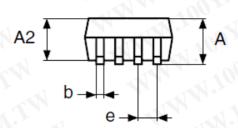

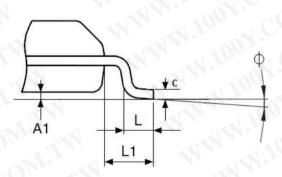

# **Packaging information**

# 8 - Lead Plastic Thin Shrink Small Outline - 4.4mm TSSOP

| Parameter                | Symbol | Min.    | Nom.               | Max. |  |

|--------------------------|--------|---------|--------------------|------|--|

| Number of Pins           | N      | M4.     | 8                  |      |  |

| Lead Pitch               | е      |         | 0.65 BSC           |      |  |

| Overall hight            | Α      | -1-     |                    | 1.1  |  |

| Molded Package Thickness | A2     | 0.85    |                    | 0.95 |  |

| Standoff                 | A1     | 0.05    | (- <del>1</del> 2) | 0.15 |  |

| Overall width            | E      | 6.3     | 6.4                | 6.5  |  |

| Molded Package Width     | E1     | 4.3     | 4.4                | 4.5  |  |

| Molded Package Length    | D      | 2.9     | 3.0                | 3.1  |  |

| Foot Lenght              | L      | 0.5     | 0.6                | 0.7  |  |

| Footprint                | <1 L1  | 1.0 REF |                    |      |  |

| Foot Angle               | ф      | 0°      | A                  | 8°   |  |

| Lead Thickness           | С      | 0.13    |                    | 0.18 |  |

| Lead Width               | b      | 0.19    | 12.1               | 0.25 |  |

Units: [mm]

BSC: Basic Dimension. Theoretically exact value without tolerances.

REF: Reference Dimension, usually without tolerance, for information purpose only.

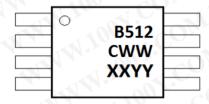

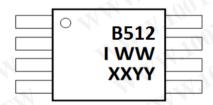

# **Package Marking Information**

#### Example:

**B**: Vcc Range 2.7 - 3.6V

**512**: Memory Size 512Kbit

C: Temp Range -20℃ to +70℃

WW: Week code (week of Januar 1 is "01")

XX: Traceability code

YY: Year code (last two digits of calendar year)

#### Example:

**B**: Vcc Range 2.7 - 3.6V

**512**: Memory Size 512Kbit

I: Temp Range -40℃ to +85℃

WW: Week code (week of Januar 1 is "01")

XX: Traceability code

YY: Year code (last two digits of calendar year)

# **Ordering Information**

| Ordering Number | Vcc Range  | Density | Temp. Ranges | <b>Packages</b> | Shipping Method |

|-----------------|------------|---------|--------------|-----------------|-----------------|

| IP12B512C-TR    | 2.7 - 3.6V | 512Kb   | -20℃ to +70℃ | TSSOP-8         | Tape & Reel     |

| IP12B512C-TU    | 2.7 - 3.6V | 512Kb   | -20℃ to +70℃ | TSSOP-8         | Tube            |

| IP12B512I-TR    | 2.7 - 3.6V | 512Kb   | -40℃ to +85℃ | TSSOP-8         | Tape & Reel     |

| IP12B512I-TU    | 2.7 - 3.6V | 512Kb   | -40℃ to +85℃ | TSSOP-8         | Tube            |

#### **Revision History**

| Revision # | Date       | Change description         |

|------------|------------|----------------------------|

| 1.0        | March 2011 | Initial productive release |

|            |            |                            |

|            |            |                            |

|            |            |                            |

|            | 40 h       | (A) (A) (A)                |

#### **Trademarks and Notice**

**IPSiLog** is a registered trademark of IPSiLog Semiconductor GmbH. All other trademarks mentioned herein are property of their respective companies.

IPSiLog reserves the right to change or modify the information contained in this data sheet and the products described therein and the right to change or discontinue work on any product without prior notice.

IPSiLog does not convey any license under its patent rights nor the rights of others. Charts, drawings and schedules contained in this data sheet are provided for illustration purposes only and they vary depending upon specific applications. IPSiLog makes no warranty or guarantee regarding suitability of these products for any particular purpose, nor does IPSiLog assume any liability arising out of the application or use of any product or circuit described herein.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, and prevention of over voltage/current levels and other abnormal operating conditions.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control), or for any use where chance of failure is intolerable. IPSiLog does not authorize use of its products as critical components in any application in which the failure of the product may be expected to result in significant injury or death, including life support device or systems and critical medical instruments.