特力材料886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

# TC358768XBG

# **Functional Specification**

**Tentative**

#### NOTICE OF DISCLAIMER

- 2 The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled

- 3 by any of the authors or developers of this material or MIPI. The material contained herein is provided on

- 4 an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS

- 5 AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all

- 6 other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if

- any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of

- 8 accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of

- 9 negligence.

- All materials contained herein are protected by copyright laws, and may not be reproduced, republished,

- 11 distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express

- prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related

- 13 trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and

- cannot be used without its express prior written permission.

- 15 ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET

- 16 POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD

- 17 TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY

- 18 AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR

- 19 MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

- 20 GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL,

- 21 CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

- 22 CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR

- 23 ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL,

- 24 WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

- 25 DAMAGES.

- Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is

- 27 further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the

- 28 contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document;

- and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance

- 30 with the contents of this Document. The use or implementation of the contents of this Document may

- 31 involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents,

- patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI

- does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any

- 34 IPR or claims of IPR as respects the contents of this Document or otherwise.

- 35 Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

- 36 MIPI Alliance, Inc.

- 37 c/o IEEE-ISTO

- 38 445 Hoes Lane

- 39 Piscataway, NJ 08854

- 40 Attn: Board Secretary

#### **HISTORY**

| Revision | Date                                                                                                                                                                                                                                                                   | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Rev 0.20 | 04/05/2011                                                                                                                                                                                                                                                             | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Rev 0.21 | 04/29/2011                                                                                                                                                                                                                                                             | Add Parallel Vertical/Horizontal Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Rev 0.22 | 05/05/2011                                                                                                                                                                                                                                                             | Updated for DSITX registers Updated Chapter 4 for PCLK option                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Rev 0.23 | 05/10/2011                                                                                                                                                                                                                                                             | Updated - Section 3.2 (Pin Layout) - Section 6 (Package)                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Rev 0.24 | 05/16/2011                                                                                                                                                                                                                                                             | Fixed typo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Rev 0.25 | 05/18/2011                                                                                                                                                                                                                                                             | Fixed typo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Rev 0.26 | 06/29/2011                                                                                                                                                                                                                                                             | Fixed typo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Rev 0.27 | 07/20/2011                                                                                                                                                                                                                                                             | Add DSITX register                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Rev 0.28 | 07/23/2011                                                                                                                                                                                                                                                             | Added 0x238 and 0x23C registers Fixed typo Add section 3.7                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Rev 0.29 | 07/27/2011                                                                                                                                                                                                                                                             | Fixed typo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Rev 0.30 | 08/06/2011                                                                                                                                                                                                                                                             | <ul> <li>Add more register descriptions.</li> <li>Rename some registers to reflect their content.</li> <li>Change TX DCS command to TX DSI Command Packet, re-wrote section 3.6</li> <li>RXFIFO (0x0430) → DSICMD_RDFIFO, DSI_STATUS → RDFIFO_STATUS</li> <li>Remove old section 3.7, Change CMQ (0x0500) → DSI_CONFW register and rename the original DSI_CONTROL (0x040C) to DSI_CONFR</li> <li>Remove I2C internal design description</li> <li>Change SPI frame size to 32-bit</li> </ul> |  |  |  |  |

| Rev 0.31 | <ol> <li>Typo Corrections</li> <li>SYSCLK → (MIPI) HSByteClk</li> <li>Add supporting of 0x39 DCS Long Write (limited to 8 bytes) Packet</li> <li>Update paragraph 4.1.2 and Figure 4-1, adding "PClk toggles before accessing/programming 768" requirement.</li> </ol> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Rev 0.32 | 09/01/2011                                                                                                                                                                                                                                                             | <ol> <li>Add 32-bit write requirement to MIPI Related Registers</li> <li>Add FIFOStatus Register</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

#### **REFERENCES**

- 1. MIPI DSI, "mipi\_DSI\_specification\_v01-02-00, June 28, 2010"

- 2. MIPI DCS "DRAFT mipi\_DCS\_specification\_v01-02-00\_r0-02, December 2008"

- 3. MIPI D-PHY, "mipi\_D-PHY\_specification\_v01-00-00, May 14, 2009"

- 4. I2C bus specification, version 2.1, January 2000, Philips Semiconductor

#### **Table of content**

| 1 | Overview                                                  |       |

|---|-----------------------------------------------------------|-------|

| 2 | Features                                                  | 12    |

| 3 | External Pins                                             | SŠ 14 |

|   | 3.1 TC358768XBG BGA72 Pin Count Summary                   |       |

|   | 3.2 Pin Layout                                            |       |

|   | 3.3 System Overview                                       |       |

|   | 3.4 DSI TX Protocol                                       |       |

|   | 3.4.1 Video Mode Transmission                             |       |

|   | 3.4.2 Pixel Format                                        |       |

|   | 3.5 DSI TX Video Packet Operation                         |       |

|   | 3.6 DSI TX Command Packet Operation                       |       |

|   | 3.6.1 TX Short Packet (DCS) Write Command                 |       |

|   | 3.6.2 TX Long Packet Write Command                        |       |

|   | 3.6.3 TX (Short) Packet Read Command                      |       |

|   | 3.7 Parallel Input (RGB)                                  |       |

|   | 3.7.1 Overview                                            |       |

|   | 3.7.2 Timing Diagrams for Video signals (Vsync and Hsync) |       |

|   | 3.8 I2C Slave Interface                                   |       |

|   | 3.8.1 Overview                                            |       |

|   | 3.8.2 I2C Write Access Translation                        |       |

|   | 3.8.3 I2C Read Access Translation                         |       |

|   | 3.9 SPI Slave Interface                                   |       |

|   | 3.9.1 Clocking Modes                                      |       |

|   | 3.9.1.1 Timing Diagram                                    |       |

|   | 3.9.1.2 Providing Register Address over SPI Interface     |       |

|   | 3.9.1.3 SPI Write Access Translation                      |       |

|   | 3.9.1.4 SPI Read Access Translation                       |       |

|   | 3.9.2 Full Duplex                                         | 32    |

|   | 3.9.2.1 Back-2-back writes                                |       |

|   | 3.9.2.2 Back-2-back reads                                 |       |

|   | 3.9.2.3 Write-after-Read                                  |       |

|   | 3.9.2.4 Read-after-Write                                  |       |

|   | 3.9.2.5 NOP-after-Read                                    |       |

| 4 | Clock and System                                          | 30    |

|   | 4.1.1 Example of PLL Generated Clock Frequency            |       |

|   | 4.1.2 TC358768XBG Power Up Procedure                      |       |

|   | 4.1.3 TC358768XBG Power Down Procedure                    |       |

| 5 | RegFile Block                                             | 3(    |

| J | 5.1 Register Map                                          |       |

|   | 5.2 Register Description                                  |       |

|   | 5.2.1 Chip and Revision ID (ChipID: 0x0000)               |       |

|   | 5.2.2 System Control Register (SysCtl:0x0000)             |       |

|   | 5.2.3 Input Control Register (InputCtl: 0x0004)           |       |

|   | 5.2.4 FiFo Control Register (FiFoCtl: 0x0006)             |       |

|   | 5.2.5 Data Format Control Register (DataFmt: 0x0008)      |       |

|   | 5.2.6 Data i official togistor (Data int. 5.0000)         |       |

TC358768XBG Functional Spec

Page 5 of 92

| 5.2.6  | GPIO Enable Register (GPIOEn: 0x000E)                          | 44 |

|--------|----------------------------------------------------------------|----|

| 5.2.7  | GPIO Direction Register (GPIODir: 0x0010)                      |    |

| 5.2.8  | GPIO Pin Value Register (GPIOPin: 0x0012)                      | 44 |

| 5.2.9  | GPIO Output Value Register (GPIOOut: 0x0014)                   | 45 |

| 5.2.10 | PLL Control Register 0 (PLLCtl0: 0x0016)                       | 45 |

| 5.2.11 | PLL Control Register 1 (PLLCtl1: 0x0018)                       | 46 |

|        | DSITX Data Type Register (DSITX_DT: 0x0050)                    |    |

|        | FIFO Status Register (FIFOSTATUS: 0x00F8)                      |    |

| 5.2.14 | Clock Lane DPHY TX Control register (CLW_DPHYCONTTX: 0x0100)   | 48 |

|        | Data Lane 0 DPHY TX Control register (D0W_DPHYCONTTX:0x0104)   |    |

|        | Data Lane 1 DPHY TX Control Register (D1W_DPHYCONTTX: 0x0108)  |    |

|        | Data Lane 2 DPHY TX Control Register (D2W_DPHYCONTTX: 0x010C)  |    |

| 5.2.18 | Data Lane 3 DPHY TX Control Register (D3W_DPHYCONTTX: 0x0110)  | 54 |

|        | Clock Lane DPHY Control Register (CLW_CNTRL: 0x0140)           |    |

| 5.2.20 | Data Lane 0 DPHY Control Register (D0W_CNTRL: 0x0144)          | 56 |

|        | Data Lane 1 DPHY Control Register (D1W_CNTRL: 0x0148)          |    |

| 5.2.22 | Data Lane 2 DPHY Control Register (D2W_CNTRL:0x014C)           | 58 |

|        | Data Lane 3 DPHY Control Register (D3W_CNTRL: 0x0150)          |    |

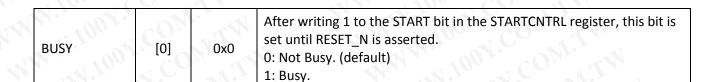

|        | STARTCNTRL (STARTCNTRL: 0x0204)                                |    |

|        | STATUS (STATUS: 0x0208)                                        |    |

| 5.2.26 | LINEINITCNT (LINEINITCNT: 0x0210)                              | 61 |

| 5.2.27 | LPTXTIMECNT (LPTXTIMECNT: 0x0214)                              | 61 |

| 5.2.28 | TCLK_HEADERCNT (TCLK_HEADERCNT: 0x0218)                        | 62 |

| 5.2.29 | TCLK_TRAILCNT (TCLK_TRAILCNT: 0x021C)                          | 64 |

| 5.2.30 | THS_HEADERCNT (THS_HEADERCNT: 0x0220)                          | 64 |

|        | TWAKEUP (TWAKEUP: 0x0224)                                      |    |

| 5.2.32 | TCLK_POSTCNT (TCLK_POSTCNT: 0x0228)                            | 66 |

| 5.2.33 | THS_TRAILCNT (THS_TRAILCNT: 0x022C)                            | 66 |

| 5.2.34 | HSTXVREGCNT (HSTXVREGCNT: 0x0230)                              | 67 |

| 5.2.35 | HSTXVREGEN (HSTXVREGEN: 0x0234)                                | 68 |

|        | TXOPTIONCNTRL (TXOPTIONCNTRL: 0x0238)                          |    |

|        | BTACNTRL1 (BTACNTRL1: 0x023C)                                  |    |

|        | DSI Command Read FIFO STATUS Register (RDFIFO_STATUS: 0x0410)  |    |

|        | DSI Command Read Data FIFO Register (DSICMD_RDFIFO: 0x0430)    |    |

|        | DSI Configuration Read Register (DSI_CONFR: 0x040C)            |    |

|        | DSI Configuration Register (DSI_CONFW: 0x0500)                 |    |

| 5.2.42 | DSI START Register (DSI_START: 0x0518)                         | 74 |

| 5.2.43 | DSI Command Packet Start Transmit Register (DSICMD_TX: 0x0600) | 75 |

| 5.2.44 | DCS Command Type Register (DSICMD_TYPE: 0x0602)                | 75 |

|        | DSI Command Packet Word Count Register (DSICMD_WC: 0x0604)     |    |

|        | DSI Command Packet Data Register 0 (DSICMD_WD0: 0x0610)        |    |

|        | DSI Command Packet Data Register 1 (DSICMD_WD1: 0x0612)        |    |

|        | DSI Command Packet Data Register 2 (DSICMD_WD2: 0x0614)        |    |

|        | DSI Command Packet Data Register 3 (DSICMD_WD3: 0x0616)        |    |

|        | DSI Event Mode Register (DSI_EVENT: 0x0620)                    |    |

|        | DSI Vsync Width Register 1 (DSI_VSW: 0x0622)                   |    |

| 5.2.52 | DSI VBPR Register (DSI_VBPR: 0x0624)                           | 78 |

|        | DSI Vertical Active Register (DSI_VACT: 0x0626)                |    |

| 5.2.54 | DSI Hsync Width Register (DSI_HSW: 0x0628)                     | 79 |

Page 6 of 92

| 5   | 5.2.55 DSI HBPR Register (DSI_HBPR: 0x062A)              | 79 |

|-----|----------------------------------------------------------|----|

| , E | 5.2.56 DSI Horizontal Active Register (DSI_HACT: 0x062C) | 79 |

| 6 P | Package                                                  | 81 |

| 7 E | Electrical Characteristics                               | 83 |

|     | 1 Absolute Maximum Ratings                               |    |

|     | 2 Recommended Operating Condition                        |    |

|     | 3 DC Electrical Specification                            |    |

| 8 T | iming Definitions                                        | 85 |

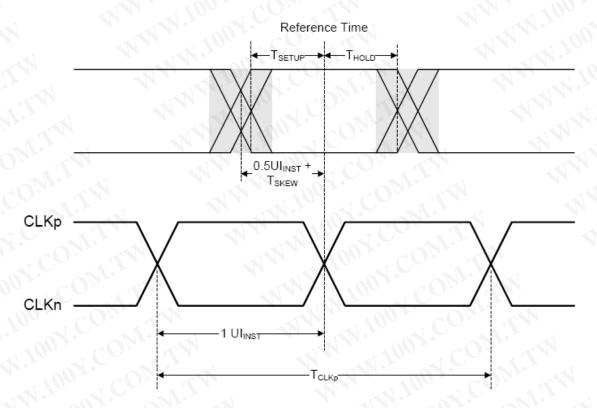

|     | 1 MIPI – 2 Timings                                       |    |

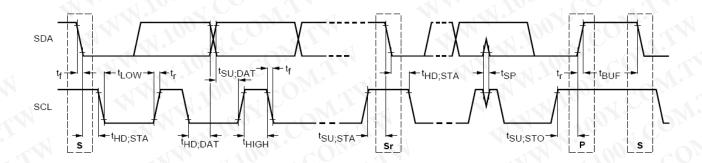

| 8.2 | 2 I2C Timings                                            | 88 |

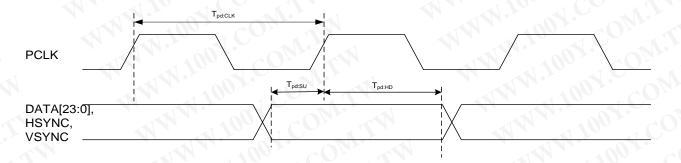

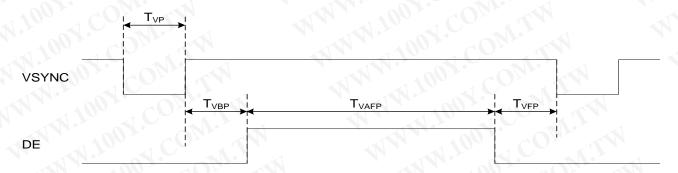

| 8.3 | 3 Parallel Port Input Timings                            | 90 |

|     | 4 SPI Input/Output Timings                               |    |

| J | ile di Figures                                                               |    |

|---|------------------------------------------------------------------------------|----|

|   | Figure 1-1 System Overview with TC358768XBG in RGB to DSI-TX                 | 11 |

|   | Figure 3-1 TC358768XBG 64-Pin Layout                                         | 16 |

|   | Figure 3-2 TC358768XBG Data/Controls Flow in RGB to DSI-TX                   | 17 |

|   | Figure 3-3 DSI Short Command Packet Assembly                                 |    |

|   | Figure 3-4 DSI Long Command Packet Assembly                                  |    |

|   | Figure 3-5 DSICMD_RXFIFO Data Arrangement                                    |    |

|   | Figure 3-6 VSYNC/HSYNC/DE Timing Diagram – Pulse mode                        |    |

|   | Figure 3-7 VSYNC/HSYNC/DE Timing Diagram – Event mode                        |    |

|   | Figure 3-8 I2C Write Transfers Translated to Register Write Accesses         |    |

|   | Figure 3-9 I2C Read Transfers to Register Read Accesses                      |    |

|   | Figure 3-10 SPI basic operation                                              |    |

|   | Figure 3-11 SPI transfer                                                     | 30 |

|   | Figure 3-12 Register Write Transfer over SPI (transfer size=32 bits)         | 31 |

|   | Figure 3-13 Register Write Transfer over SPI (transfer size=32 bits)         |    |

|   | Figure 3-14 Register Read (Normal) Transfer over SPI (transfer size=32 bits) |    |

|   | Figure 3-15 Back-2-Back Write Transfers over SPI                             |    |

|   | Figure 3-16 Back-2-Back Read Transfers over SPI                              |    |

|   | Figure 3-17 Write-after-Read Transfer over SPI                               |    |

|   | Figure 3-18 Read-after-Write Transfer over SPI                               | 34 |

|   | Figure 3-19 NOP-after-Read Transfer over SPI                                 | 35 |

|   | Figure 4-1 Power On Sequence                                                 |    |

|   | Figure 4-2 Power Down Sequence                                               | 38 |

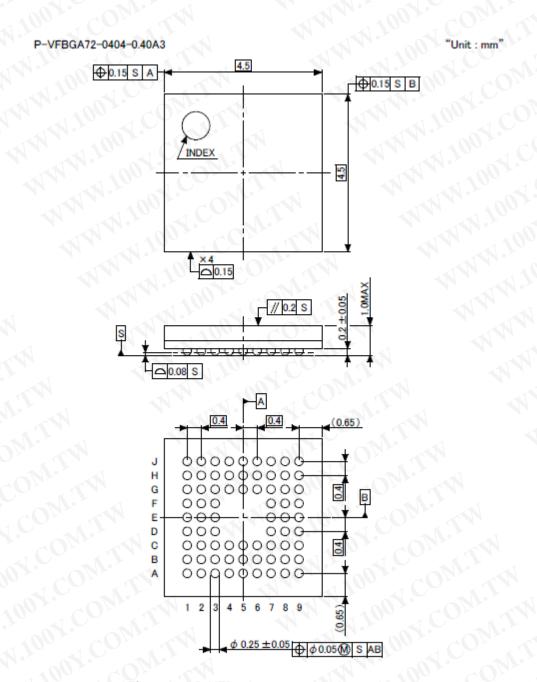

|   | Figure 6-1 P-VFBGA72-0404-0.40A3 package                                     | 81 |

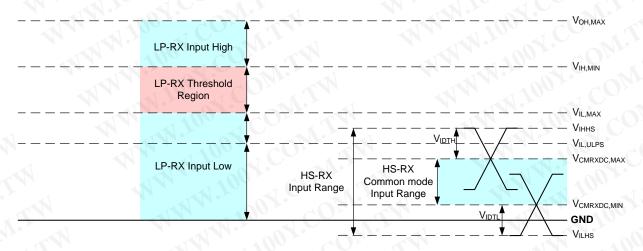

|   | Figure 8-1 Signaling and voltage levels                                      |    |

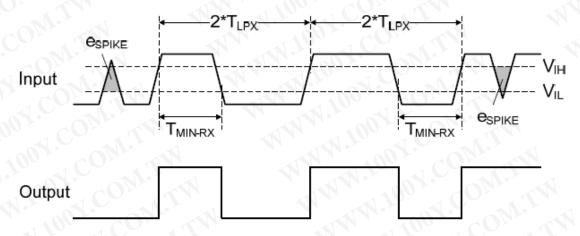

|   | Figure 8-2 Input Glitch Rejection                                            | 86 |

|   | Figure 8-3 Data to clock timing reference                                    | 87 |

|   | Figure 8-4 Parallel Input timing                                             | 90 |

|   | Figure 8-5 Parallel Vertical timing                                          |    |

|   | Figure 8-6 Parallel Horinzontal timing                                       |    |

|   | Figure 8-7 SPI timing (data valid on second active clock edge)               | 92 |

| S | t of Tables                                     |    |

|---|-------------------------------------------------|----|

|   | Table 3-1 TC358768XBG Functional Signal List    |    |

|   | Table 3-2 BGA72 Pin Count Summary               | 15 |

|   | Table 3-3 Supports Data Types                   | 18 |

|   | Table 3-4 24-bit Unpacked Data bus              |    |

|   | Table 3-5 SPI Clocking modes                    |    |

|   | Table 4-1 Possible PLL parameters               |    |

|   | Table 4-2 Controllers' Operating Frequency      |    |

|   | Table 4-3 Power On Sequence Timing              |    |

|   | Table 4-4 Power Down Sequence Timing            |    |

|   | Table 5-1 Register Map                          | 39 |

|   | Table 5-2 Chip and Revision ID                  |    |

|   | Table 5-3 System Control Register               |    |

|   | Table 5-4 Input Control Register                |    |

|   | Table 5-5 FiFo Control Register                 |    |

|   | Table 5-6 Data Format Control Register          |    |

|   | Table 5-7 GPIO Direction Register               |    |

|   | Table 5-8 GPIO Direction Register               |    |

|   | Table 5-9 GPIO Pin Value Register               |    |

|   | Table 5-10 GPIO Output Value Register           |    |

|   | Table 5-11 PLL Control Register 0               |    |

|   | Table 5-12 PLL Control Register 1               |    |

|   | Table 5-13 DSITX Data Type Register             | 47 |

|   | Table 5-13 FIFO Status Register                 | 47 |

|   | Table 5-14 Clock Lane DPHY TX Control register  | 48 |

|   | Table 5-15 Data Lane 0 DPHY TX Control register |    |

|   | Table 5-16 Data Lane 1 DPHY TX Control Register | 51 |

|   | Table 5-17 Data Lane 2 DPHY TX Control Register | 53 |

|   | Table 5-18 Data Lane 2 DPHY TX Control Register | 54 |

|   | Table 5-19 Clock Lane DPHY Control Register     | 55 |

|   | Table 5-20 Data Lane 0 DPHY Control Register    | 56 |

|   | Table 5-21 Data Lane 1 DPHY Control Register    |    |

|   | Table 5-22 Data Lane 2 DPHY Control Register    | 58 |

|   | Table 5-23 Data Lane 2 DPHY Control Register    | 59 |

|   | Table 5-24 STARTCNTRL                           |    |

|   | Table 5-25 STATUS                               |    |

|   | Table 5-26 LINEINITCNT                          |    |

|   | Table 5-27 LPTXTIMECNT                          |    |

|   | Table 5-28 TCLK_HEADERCNT                       |    |

|   | Table 5-29 TCLK_TRAILCNT                        |    |

|   | Table 5-30 THS_HEADERCNT                        |    |

|   | Table 5-31 TWAKEUP                              |    |

|   | Table 5-32 TCLK_POSTCNT                         |    |

|   | Table 5-33 THS_TRAILCNT                         |    |

|   | Table 5-34 HSTXVREGCNT                          | 67 |

Page 9 of 92

| Table 5-35 HSTXVREGEN                                 | 68 |

|-------------------------------------------------------|----|

| Table 5-36 TXOPTIONCNTRL                              | 69 |

| Table 5-37 DSI Command Read FIFO STATUS               | 70 |

| Table 5-38 DSI Command Read Data FIFO Register        | 71 |

| Table 5-39 DSI Configuration Read Register            |    |

| Table 5-40 DSI Configuration Write Register           |    |

| Table 5-41 DSI_START                                  |    |

| Table 5-42 DSI Command Packet Start Transmit Register | 75 |

| Table 5-43 DSI Command Packet Type Register           |    |

| Table 5-44 DSI Command Packet Word Count Register     | 76 |

| Table 5-45 DSI Command Packet Data Register 0         | 76 |

| Table 5-46 DSI Command Packet Data Register 1         |    |

| Table 5-47 DSI Command Packet Data Register 2         | 77 |

| Table 5-48 DSI Command Packet Data Register 3         |    |

| Table 5-49 DSI Event Mode Register                    | 77 |

| Table 5-50 DSI Vsync Width Register                   | 78 |

| Table 5-51 DSI VBPR Register                          |    |

| Table 5-52 DSI VACT Register                          | 79 |

| Table 5-53 DSI Hsync Width Register                   | 79 |

| Table 5-54 DSI HBPR Register                          | 79 |

| Table 5-55 DSI Horizontal Active Register             | 80 |

| Table 6-1 P-VFBGA72-0404-0.40A3 Mechanical Dimension  | 82 |

| Table 8-1 DC specifications                           | 85 |

| Table 8-2 High Speed AC specifications                | 86 |

| Table 8-3 Low Power AC characteristics                | 86 |

| Table 8-4 Data-Clock timing specification             | 87 |

| Table 8-5 Parallel Input timing                       |    |

| Table 8-6 Parallel Vertical timing                    |    |

| Table 8-7 Parallel Horizontal timing                  |    |

| Table 8-8 SPI timing                                  | 92 |

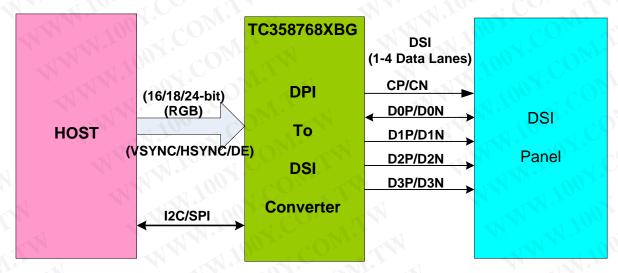

#### 1 Overview

The Parallel Port to MIPI DSI (TC358768XBG) is a bridge device that converts RGB to DSI. All internal registers can be access through I2C or SPI. .

Figure 1-1 System Overview with TC358768XBG in RGB to DSI-TX

#### 2 Features

Below are the main features supported by TC358768XBG.

#### **DSI-TX** Interface

- ♦ MIPI DSI compliant (Version 1.02.00 June 28, 2010)

- Support DSI Video Mode data transfer

- DCS Command for panel register access

- Supports up to 1 Gbps per data lane

- ♦ Supports 1,2,3 or 4 data lanes

- Supports video data formats

- RGB888/666/565

#### RGB Interface

- Supports data formats

- 24-bit data bus

- ♦ RGB888/666/565 data formats

- ♦ Up to 166 MHz input clock

- ♦ Support VSYNC/HSYNC polarity option (default LOW)

- Support DE polarity option (default High)

I2C/SPI Slave Interface (Option to select either I2C or SPI interface)

- ♦ I2C Interface (when CS=L)

- Support for normal (100KHz), fast mode (400 KHz) and Special mode (1 MHz)

- Configure all TC358768XBG internal registers

- Writing to DCS registers will trigger DCS Command transmits over DSI

- ♦ SPI interface (when CS =H)

- SPI interface support for up to 25 MHz operation.

- Configure all TC358768XBG internal registers

- Writing to DCS registers will trigger DCS Command transmits over DSI

#### **GPIO** signals

- ♦ 2 GPIO signals

- Two GPIO signals can be configured as SPI signals (SPI\_SS and SPI\_MISO)

- Or One GPIO signal can be configured as Interrupt output signal (INT).

#### System

♦ Clock and power management support to achieve low power states.

Confidential

Page 12 of 92

#### Power supply inputs

Core and MIPI D-PHY: 1.2V

I/O: 1.8V - 3.3V

#### **Power Consumption**

720P @60fps: DPI Clk: 74.25 MHz, DSIClk: 219.6 MHz → 52.4 mW 1080P @60fps: DPI Clk: 148.5 MHz, DSIClk: 471.6 MHz → 91.3 mW

## 3 External Pins

TC358768XBG resides in BGA72 pin packages. The following table gives the signals of TC358768XBG and their function.

Table 3-1 TC358768XBG Functional Signal List

| Group                       | Pin Name            | I/O | Type | Initial                     | Function                                                                                                         | Note  |

|-----------------------------|---------------------|-----|------|-----------------------------|------------------------------------------------------------------------------------------------------------------|-------|

|                             | RESX                |     | Sch  | -                           | System reset input, active low                                                                                   |       |

|                             | REFCLK              |     | N    | -                           | Reference clock input (6MHz – 40MHz)                                                                             |       |

| System:<br>Reset &<br>Clock | MSEL                |     | N    | W -                         | Mode Select 1'b0: Test mode 1'b1: Normal mode                                                                    |       |

| (4)                         | cs                  | 1.0 | N    | 7                           | Configuration Select - When CS=L, enable I2C interface - When CS=H, enable SPI interface                         | CO1   |

|                             | MIPI_CP             |     | PHY  | 1.                          | MIPI-DSI clock positive                                                                                          |       |

|                             | MIPI_CN             |     | PHY  |                             | MIPI-DSI clock negative                                                                                          |       |

|                             | MIPI_D0P            |     | PHY  |                             | MIPI-DSI Data 0 positive                                                                                         |       |

|                             | MIPI_D0N            | 100 | PHY  | 0                           | MIPI-DSI Data 0 negative                                                                                         | .1    |

| MIPI-DSI                    | MIPI_D1P            |     | PHY  |                             | MIPI-DSI Data 1 positive                                                                                         |       |

| (10)                        | MIPI_D1N            |     | PHY  |                             | MIPI-DSI Data 1 negative                                                                                         |       |

|                             | MIPI_D2P            |     | PHY  |                             | MIPI-DSI Data 2 positive                                                                                         | . 00  |

|                             | MIPI_D2N            |     | PHY  | 10                          | MIPI-DSI Data 2 negative                                                                                         |       |

|                             | MIPI_D3P            |     | PHY  | )                           | MIPI-DSI Data 3 positive                                                                                         | . 6   |

|                             | MIPI_D3N            |     | PHY  | 216                         | MIPI-DSI Data 3 negative                                                                                         | A 1 3 |

| I2C                         | I2C SCL             | OD  | Sch  | $M_{\mathcal{F}_{\bullet}}$ | I2C serial clock or SPI_SCLK                                                                                     | 4mA   |

| (2)                         | I2C SDA             | OD  | Sch  |                             | I2C serial data or SPI_MOSI                                                                                      | 4mA   |

| ON                          | PD[23:0]            |     | N    | 700                         | Parallel Port Input Data<br>Note: PD[23:16] can be config to be<br>GPIO[10:3]                                    |       |

| Parallel<br>Port            | VSYNC               | L   | N    | 110                         | Parallel port VSYNC signal                                                                                       | MA    |

| (28)                        | HSYNC               | I   | N    | 11-                         | Parallel port HSYNC signal                                                                                       |       |

| (-5)                        | DE                  | ı   | N    |                             | Parallel Port DE signal                                                                                          | N     |

|                             | PCLK                | ı   | N    |                             | Parallel Port Clock signal                                                                                       |       |

| GPIOx<br>(2)                | GPIO[2:1]           | I/O | N    |                             | GPIO[2:1] signals - (GPIO[1] option to become SPI_SS or INT signal) - (GPIO[2] option to become SPI_MISO signal) | 4mA   |

| 10                          | VDDC (1.2V)         | NA  |      | . 4                         | VDD for Internal Core (3)                                                                                        |       |

| POWER                       | VDDIO (1.8V – 3.3V) | NA  |      |                             | VDDIO is for IO power supply (4)                                                                                 |       |

| (9)                         | VDD_MIPI (1.2V)     | NA  |      |                             | VDD for the MIPI (2)                                                                                             | 4     |

| Ground<br>(17)              | vss                 | NA  | N    |                             | Ground                                                                                                           | N     |

#### 3.1 TC358768XBG BGA72 Pin Count Summary

## **Table 3-2 BGA72 Pin Count Summary**

| Group Name       | Pin<br>Count | Notes                   |

|------------------|--------------|-------------------------|

| SYSTEM           | 4            |                         |

| DSLIF            | 10           | 41/1 4 10° 1 C          |

| I2C              | 2            | . M                     |

| GPIOx            | 2            | 111, 11, 10             |

| Parallel Port IF | 28           | 100                     |

| POWER            | 9            | IO, MIPI and Core Power |

| GROUND           | 17           | 100                     |

| TOTAL            | 72           |                         |

#### 3.2 Pin Layout

| <b>A</b> 1 | A2   | АЗ    | A4                   | A5         | A6    | A7        | A8       | A9       |

|------------|------|-------|----------------------|------------|-------|-----------|----------|----------|

| VSS        | PD17 | PD19  | PD21                 | PD23       | GPIO2 | I2C_SCL   | MSEL     | VSS      |

| B1         | B2   | В3    | В4                   | <b>B</b> 5 | В6    | B7        | B8       | В9       |

| VDDC       | PD16 | PD18  | PD20                 | PD22       | GPIO1 | I2C_SDA   | RESX     | VDDIO    |

| C1         | C2   | C3    | C4                   | C5         | C6    | <b>C7</b> | C8       | C9       |

| PD15       | PD14 | VSS   | VSS                  | VSS        | VSS   | VDD_MIPI  | MIPI_D3P | MIPI_D3N |

| D1         | D2   | D3    | Mr.                  |            |       | D7        | D8       | D9       |

| PD13       | PD12 | VSS   |                      |            |       | VSS       | MIPI_D2P | MIPI_D2N |

| E1         | E2   | E3    | $G_{O_{\Sigma_{+}}}$ |            |       | E7        | E8       | E9       |

| VSS        | VSS  | VDDC  | ~O)                  |            | N     | VDD_MIPI  | MIPI_CP  | MIPI_CN  |

| F1         | F2   | F3    | 1.0                  | M.         | ~1    | F7        | F8       | F9       |

| VSS        | VSS  | VSS   | J.C                  |            |       | VSS       | MIPI_D1P | MIPI_D1N |

| G1         | G2   | G3    | G4                   | <b>G</b> 5 | G6    | G7        | G8       | G9       |

| PD11       | PD10 | VDDIO | VSS                  | VSS        | VDDIO | VDDIO     | MIPI_D0P | MIPI_D0N |

| H1         | H2   | НЗ    | H4                   | H5         | H6    | H7        | Н8       | Н9       |

| VDDC       | PD8  | PD6   | PD4                  | PD2        | PD0   | PCLK      | DE       | cs       |

| J1         | J2   | J3    | J4                   | J5         | J6    | J7        | J8       | J9       |

| VSS        | PD9  | PD7   | PD5                  | PD3        | PD1   | REFCLK    | VSYNC    | HSYNC    |

Figure 3-1 TC358768XBG 64-Pin Layout

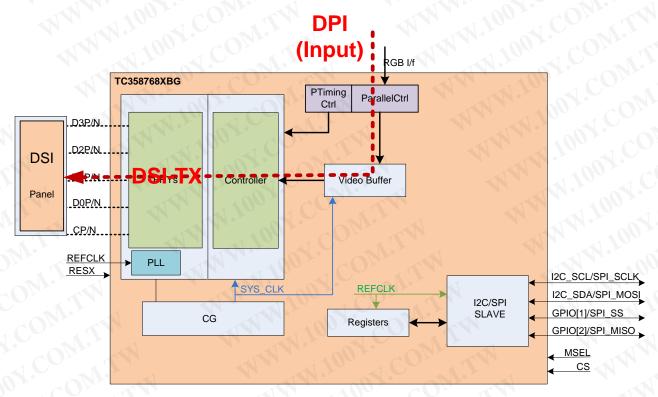

#### 3.3 System Overview

TC358768XBG received the data/controls from RGB then transmits them out to MIPI DSI TX. Host uses I2C/SPI interface to configure all TC358768XBG internal registers.

Figure 3-2 TC358768XBG Data/Controls Flow in RGB to DSI-TX

## 3.4 DSI TX Protocol

Table below shows all the data types that supported in TC358768XBG.

**Table 3-3 Supports Data Types**

| Data Type | Description                                           | Packet<br>Size |

|-----------|-------------------------------------------------------|----------------|

| 0x01      | Sync Event, V Sync Start                              | Short          |

| 0x11      | Sync Event, V Sync End                                | Short          |

| 0x21      | Sync Event, H Sync Start                              | Short          |

| 0x31      | Sync Event, H Sync End                                | Short          |

| 0x08      | End of Transmission packet (EoTp)                     | Short          |

| 0x02      | Color Mode (CM) Off Command                           | Short          |

| 0x12      | Color Mode (CM) On Command                            | Short          |

| 0x22      | Shut Down Peripheral Command                          | Short          |

| 0x32      | Turn On Peripheral Command                            | Short          |

| 0x03      | Generic Short WRITE, no parameters                    | Short          |

| 0x13      | Generic Short WRITE, 1 parameter                      | Short          |

| 0x23      | Generic Short WRITE, 2 parameters                     | Short          |

| 0x04      | Generic READ, no parameters                           | Short          |

| 0x14      | Generic READ, 1 parameter                             | Short          |

| 0x24      | Generic READ, 2 parameters                            | Short          |

| 0x05      | DCS Short WRITE, no parameters                        | Short          |

| 0x15      | DCS Short WRITE, 1 parameter                          | Short          |

| 0x06      | DCS READ, no parameters                               | Short          |

| 0x37      | Set Maximum Return Packet Size                        | Short          |

| 0x29      | Generic Long Write (Max 8 byte for register access)   | Long           |

| 0x39      | DCS Long Write (Max 8 byte for register access)       | Long           |

| 0x0E      | Packed Pixel Stream, 16-bit RGB, 5-6-5 Format         | Long           |

| 0x1E      | Packed Pixel Stream, 18-bit RGB, 6-6-6 Format         | Long           |

| 0x2E      | Loosely Packed Pixel Stream, 18-bit RGB, 6-6-6 Format | Long           |

| 0x3E      | Packed Pixel Stream, 24-bit RGB, 8-8-8 Format         | Long           |

#### 3.4.1 Video Mode Transmission

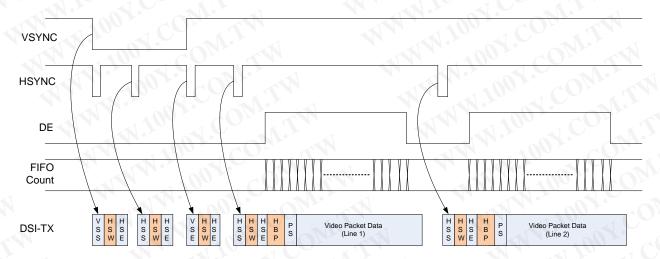

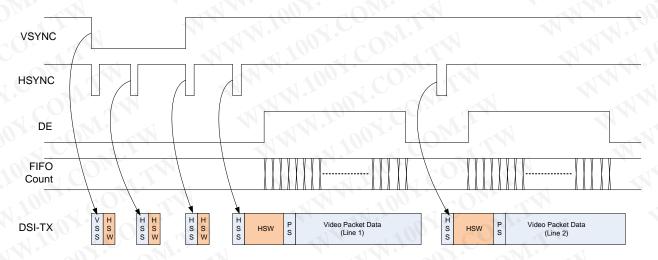

In Video mode, TC358768XBG transmits all video timing events and pixel data in proper sequence and time. Video timing events are transmitted in these DSI short packets: VSYNC Start, VSYNC End, HSYNC Start, and HSYNC End. They are multiplexed with null (or blank) packets (or transitioned to LP idle cycle) and pixel data packets in the DSI serial link such that their reception at the chip will reflect in signal transition on VSYNC and HSYNC at proper timing for the receiving display panel. Pixel data is expected to be transmitted using Pixel Stream packet types (Data Type ID = 0x0E, 0x1E, 0x2E or 0x3E.).

VSYNC Start, VSYNC End, HSYNC Start and HSYNC End are trigger by RGB VSYNC and HSYNC pulse. Refer to Figure 3-6 for more information.

Video Line byte count must be configs into Word Count Register 1 (WordCnt1) before starting transfer video over RGB.

#### 3.4.2 Pixel Format

The chip supports RGB-565, RGB-666 packed or loose, and RGB-888 pixel formats in video data packets.

In video mode transmission, pixel format is differentiated by the data type ID in the header of pixel stream packets received. Data type ID must be configured into DSITX\_DT register before starting video transmission.

#### 3.5 DSI TX Video Packet Operation

Below describes the TC358768XBG sequence for transmit out the video data onto DSI TX.

- 1) Configures all registers.

- 2) Enable Parallel Input port.

- 3) Detects VSYNC transition

- a. If detect VSYNC transition from HIGH to LOW. Transmits VSYNC Start packet.

- b. Detect HSYNC pulse (generate Hsync Start, Hsync End packets accordingly)

- c. If detect VSYNC transition from LOW to HIGH. Transmits VSYNC End packet. Go to step "4"

- 4) Detect HSYNC pulse (generate Hsync Start, Hsync End packets accordingly). Once detect DE transition from LOW to HIGH then go to step "5".

- 5) Wait for the Video buffer reaches the programmable "FIFO Level" go to step "6"

- Transmits Video packet (one line) then go to step "7"

- 7) Detects HSYNC pulse (generate Hsync Start, Hsync End packets accordingly). If detect DE transition from LOW to HIGH then go to step "5"

- a. If detect VSYNC transition from HIGH to LOW. Transmits VSYNC Start packet, go to step "3"

Note: Assume VSYNC/HSYNC are active LOW.

#### 3.6 DSI TX Command Packet Operation

Below describes the TC358768XBG sequence for transmitting out DSI, including DCS, Command over DSI TX. Host can use either I2C or SPI interface to access to TC358768XBG registers.

By programming the following registers, TC358768XBG will generate/transmit DSI command packets. ECC and CRC are generated and attached automatically by the hardware.

- DSICMD\_TX (Register 0x0600)

- Contains DSI Command Packet Start Transmit bit.

- DSICMD\_TYPE (Register 0x0602)

- Contains DSI (short or long) CommandPacket Type

- Contains DSI Packet Data ID

- DSICMD\_WC (Register 0x0604)

- Contains DSI Command Packet Word Count

- DSICMD\_WD0, DSICMD\_WD1, DSICMD\_WD2, DSICMD\_WD3 (0x0610 0x0616)

- Contains DSI Command Packet Data Bytes (total 8 bytes)

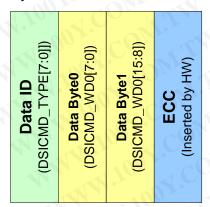

#### 3.6.1 TX Short Packet (DCS) Write Command

The relationship/assembly of a short DSI packet respect to the DSICMD\_\*\* registers are illustrated in Figure 3-3. The command code, either DCS command or Panel specific command, is stored in Data Byte 0 while Data Byte1 contains either command parameter or "0x00".

Figure 3-3 DSI Short Command Packet Assembly

The step-by-step procedure is listed below with two examples:

- 1 Set register DSICMD TYPE[PkType] = 0x10 for DSI short packet.

- 2 Choose desired DCS Short Write Command in register DSICMD\_TYPE[DATA\_ID] = 0x05 or 0x15 for DCS Command without parameter or with 1 parameter, respectively.

- 3 Be sure to set 0x0000 in DSICMD WC register.

- 4 Program DCS command code (as specified in MIPI DCS Command Spec in DSICMD\_WD0[7:0].

Confidential

- 5 If DSICMD\_TYPE[DATA\_ID] = 0x15, set DCS Command Parameter in DSICMD\_WD0[15:8]. Otherwise set "0x00" in DSICMD\_WD0[15:8].

- 6 Set DSICMD TX = 0x01 to start DCS Write Short packet.

#### Example1: TX DCS Short Command: Exit\_Sleep\_Mode (0x11), no parameter

```

0x0602 = 0x1005 (Short packet, Data ID = 0x05)

0x0604 = 0x0000 (WC1,WC0=0 for DSC short write)

0x0610 = 0x0011 (Data1= 0,DCS Command)

0x0600 = 0x0001 (Start transfer)

```

Example2: TX DCS Short Command: Set\_Pixel\_Format (0x3A), 1 parameter (DPI RGB888

```

0x0602 = 0x1015 (Short packet, Data ID = 0x15)

0x0604 = 0x0000 (WC1,WC0=0 for DSC short write)

0x0610 = 0x703A (DPI RGB888,DCS Command)

0x0600 = 0x0001 (Start transfer)

```

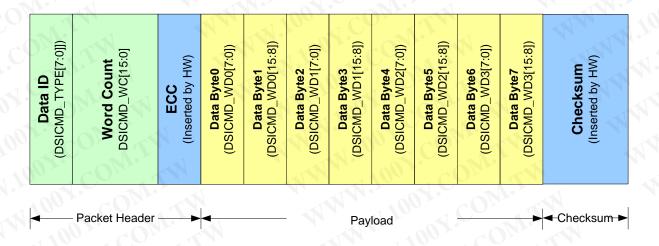

#### 3.6.2 TX Long Packet Write Command

The relationship/assembly of a long DSI packet respect to the DSICMD\_\*\* registers are illustrated in Figure 3-4. The command code, either DCS command or Panel specific command, is stored in Data Byte 0 while Data Byte1 to Data 7contains either command parameters. The maximum word count for DSI Long Command is limited to 8 bytes. For a single byte command code, the maximum parameters length can be 7 bytes.

Figure 3-4 DSI Long Command Packet Assembly

The step-by-step procedure is listed below with an examples:

- 1 Set register DSICMD\_TYPE[PkType] = 0x40 for DSI long packet.

- 2 Choose desired DSI Long Write Packet/Command, ex, 0x19 for Generate Long Write Packet, in register DSICMD\_TYPE[DATA\_ID] field.

- 3 Set DSICMD\_WC register to the correct word count, number of data bytes in the packet.

- 4 Fill update to 8-bytes of data in registers DSICMD\_WD0, 1, 2 & 3 in sequence.

- 5 For DCS Long Write Command, the command code should be set at register DSICMD\_WD0[7:0].

- 6 Set DSICMD\_TX = 0x01 to start DCS Write Short packet.

Example: TX Generic Long Write Packet with 4 bytes of Data: 0x12, 0x34, 0x56, 0x78

#### 3.6.3 TX (Short) Packet Read Command

All the DSI Read packet are short packets. After issuing any read command, TC358768 will automatically performs bus turn around and the data returned will be stored in register DSICMD\_RDFIFO for Application Processor to read. DSICMD\_RDFIFO is a 32 x 8 FIFO, which means TC35768 can accept up to 32 byte of data per DSI Read command. TC35768 is expected to send DSI "Set Maximum Return Packet Size" short packet (Data ID = 0x37) to the DSI Rx to indicate how many bytes it needs to read in the following read command(s). The sequence are:

1 Inform DSI Rx the desired bytes to read by sending "Maximum Return Packet Size" short packet

```

0x0602 = 0x1037 (Short packet, Data ID = 0x37)

0x0604 = 0x0000 (WC1,WC0=0 for Short Packet)

0x0610 = 0x0008 (Read 8-byte of Data, 2 parameters)

0x0600 = 0x0001 (Start transfer)

```

2 Issue a DCS Read Command get\_power\_mode (0x0A)

```

0x0602 = 0x1006 (Short packet, Data ID = 0x06, DCS Read, no parameter)

0x0604 = 0x0000 (WC1,WC0=0 for DSC Short Packet)

0x0610 = 0x000A (Data1, DCS Command)

0x0600 = 0x0001 (Start transfer)

```

3 TC35768 performs Bus Turn Around (BTA) automatically to let DSI Rx to send one byte of

Confidential

Page 23 of 92

- a. The received data will be pushed into DSICMD\_RDFIFO (0x0430), where Host can read the data from

- b. Host can monitor registers bit RDFIFO STATUS[5] when asserted data arrived.

- c. Host needs to track the data which is read into DSICMD\_RDFIFO if multiple read commands were issued before it fetch the data.

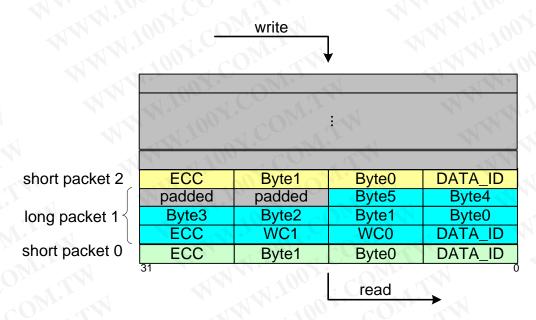

TC358768 does not extract data out of each LP packets received from DSIRx, a whole packet is stored into DSICMD\_RXFIFO, packed into 32-bit boundary as shown in Figure 3-5 below. It is up to the Host to fetch and interpret the data.

Figure 3-5 DSICMD\_RXFIFO Data Arrangement

#### 3.7 Parallel Input (RGB)

#### 3.7.1 Overview

24-bit parallel input interface is capable to transfer various types of data formats (RGB888/666/565). The signal connections for these types are shown in below Table.

Pin Usage Mode **Data Type** PD[23:0] Comment 0 {R[7:0],G[7:0],B[7:0]} 1 pixel/PClk **RGB888 RGB888** 1 {R[1:0]G[1:0],B[1:0],R[7:2],G[7:2],B[7:2]} 1 pixel/PClk {2'b0,R[5:0],2'b0,G[5:0],2'b0,B[5:0]} 1 pixel/PClk **RGB666** 0 **RGB666** 1 {6'b0,R[5:0],G[5:0],B[5:0]} 1 pixel/PClk {2'b0,R[4:0],3'b0,G[5:0],2'b0,B[4:0],1'b0} **RGB565** 0 1 pixel/PClk 1 {3'b0,R[4:0],2'b0,G[5:0],3'b0,B[4:0]} 1 pixel/PClk **RGB565** 2 1 pixel/PClk **RGB565** {8'b0,R[4:0],G[5:0],B[4:0]}

Table 3-4 24-bit Unpacked Data bus

The Parallel Input controller received the video data from external RGB transmitter. It then packed these into 32-bit data format then transfers the packed data into the Video buffer. The 32-bit data format is showed in Table 3-5.

Parallel Input controller is operated with PCLK only. All asynchronous logic is handled inside Video buffer Controller

#### 3.7.2 Timing Diagrams for Video signals (Vsync and Hsync)

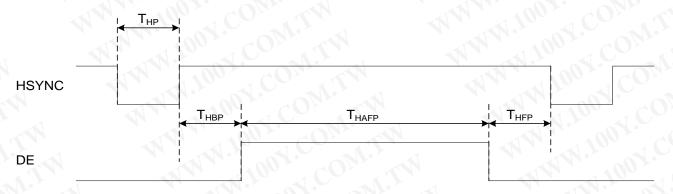

Below Figures show the timing relationship between HSYNC, VSYNC, DE and DSI-TX.

Figure 3-6 VSYNC/HSYNC/DE Timing Diagram - Pulse mode

Figure 3-7 VSYNC/HSYNC/DE Timing Diagram - Event mode

#### 3.8 I2C Slave Interface

#### 3.8.1 Overview

TC358768XBG supports an I2C slave function. The I2C module supports the following features:

- Fail safe I2C pad operation

- Up to 400 KHz fast mode operation or 1MHz for special mode operation.

- Supports 7 bit slave addresses recognition (slave address=7'b0000 111X)

- No support for general call address

- Supports 16 bit index value for TC358768XBG I2C slave access

The I2C slave function supports a fixed slave address only and does not support general call address. The I2C slave function does not require any programmable configuration parameters.

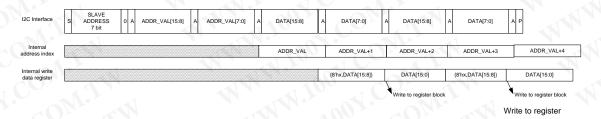

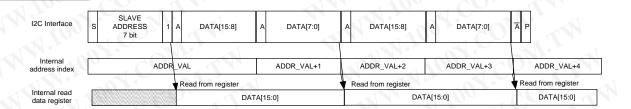

#### 3.8.2 I2C Write Access Translation

Registers in TC358768XBG are 16 bit aligned. This implies that I2C accesses to registers should always be done on 16 bit boundaries. The I2C slave will update an internal 16-bit write data register indexed by the Isb of the internal address index. Write access to TC358768XBG registers over the register interface is performed when a byte of data has been received and the internal address index has hit a 16-bit boundary. This mechanism allows 16-bit aligned registers to be updated simultaneously based on the register address value presented on the I2C bus interface. Note that data transferred on the I2C bus is sent MSB first.

Figure 3-8 I2C Write Transfers Translated to Register Write Accesses

#### 3.8.3 I2C Read Access Translation

Registers in TC358768XBG are 16 bit aligned. This implies that I2C accesses to registers should always be done on 16 bit boundaries. The I2C slave will update an internal 16-bit read data register when it received the I2C read command or when a byte transfer has completed and the internal address index has hit a 16-bit boundary. Data from the internal read register indexed by the Isb of the internal address index is then transferred over the I2C bus. This mechanism allows 16-bit aligned registers to be read without any side effects. Note that data transferred on the I2C bus is sent MSB first.

Figure 3-9 I2C Read Transfers to Register Read Accesses

#### 3.9 SPI Slave Interface

The TC358768XBG Bridge Chip incorporates a SPI Slave Interface port which Host can drive to configure registers in the chip.

The following features are supported:

- Slave select pin supported

- Clock Polarity and Phase selectable

- Transfer Frame size of 32 bits

- Slave speed is up to 25 MHz

- Supports 16 bit index value for TC358768XBG SPI slave access

The basic operation of SPI interface is shown below where the standard 4-wire interface is used for transactions between the Host (SPI Master) and TC358768XBG (SPI Slave).

The Host asserts (active low) the Slave Select signal (SPI\_SS) when it wants to initiate a read or write transaction. This is followed by the Host sending 32 pulses on the SPI Clock signal (SPI\_SCK). In this spec., the bit slots are assumed numbered 31 to 0 from left to right.

Once the intended 16 bits (for TC358768XBG register address and command) and the additional data bits have been transferred, the Host de-asserts the Slave Select signal (SPI\_SS) to indicate end of frame transfer.

This is shown in a simplistic way in the figure below (16 bits transfer size shown in the figure).

Figure 3-10 SPI basic operation

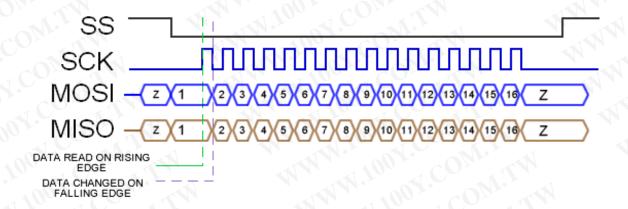

#### 3.9.1 Clocking Modes

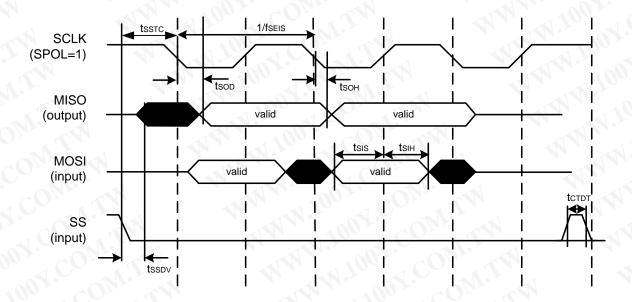

The SPI slave function supports one clocking mode which shown below.

**Table 3-5 SPI Clocking modes**

| Mode | SPOL | SPHA | Drive<br>Edge | Sample<br>Edge | Comments                                                 |

|------|------|------|---------------|----------------|----------------------------------------------------------|

| 3    | 1    | 1    | negedge       | posedge        | Master/Slave drive first data on first active clock edge |

#### 3.9.1.1 Timing Diagram

In this transfer format, the first bit value is captured on the second clock edge. This will be on a rising edge. The levels on the MOSI and MISO signals always change with the inactive clock edges on SCLK. The inactive clock edge will be the falling edge. It will idle high.

Figure 3-11 SPI transfer

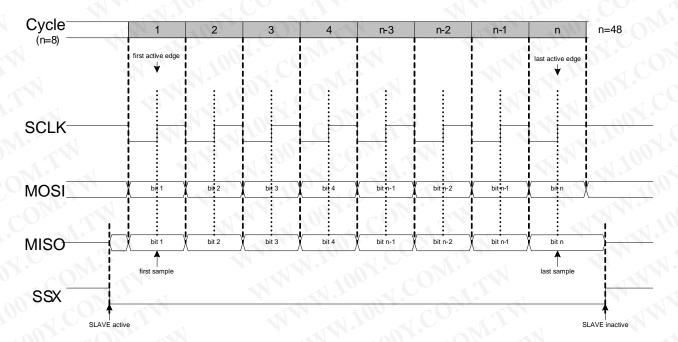

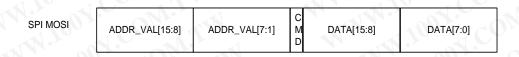

#### 3.9.1.2 Providing Register Address over SPI Interface

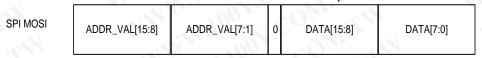

The SPI transactions are performed in 32 bits wide frames. The SPI master drives the command and address of the TC358768XBG register to be accessed. The first 15 bits provide the register address bits 15 to 1. The 16th bit of a frame is the command: 0=Write / 1=Read. Meaning of rest of the bits is based on transaction type. This frame structure is shown in the figure below for a write transaction.

Confidential

Page 30 of 92

Figure 3-12 Register Write Transfer over SPI (transfer size=32 bits)

CMD = Command: 1=Read / 0=Write

SPI slave function supports random write and read accesses.

#### 3.9.1.3 SPI Write Access Translation

Registers in TC358768XBG are 16 bit aligned. This implies that SPI accesses to registers should always be done on 16 bit boundaries. The SPI slave will update an internal 16-bit write data register indexed by the address in the SPI frame. The data in bit slots 15 to 0 (after the first 16 bits of address and command) on MOSI line is used as the write data for these writes. Write access to TC358768XBG registers over the register interface is performed when a frame transfer is completed with command bit set to 0. During the write transaction, the data on the MISO line is not related to the write transaction. How to handle the data on MISO line during write transactions is discussed more in section on full-duplex mode.

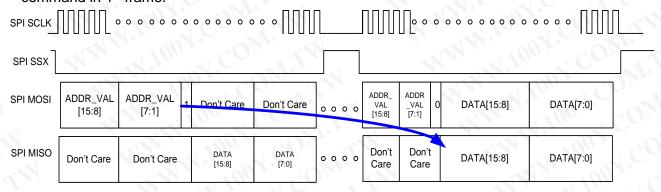

Figure 3-13 Register Write Transfer over SPI (transfer size=32 bits)

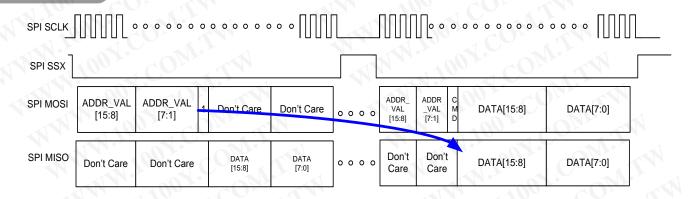

#### 3.9.1.4 SPI Read Access Translation

Registers in TC358768XBG are 16 bit aligned. This implies that SPI accesses to registers should always be done on 16 bit boundaries. The SPI slave will access an internal 16-bit data register indexed by the address in the SPI frame.

Read access to TC358768XBG registers is completed in two frames. The first frame is similar to a write frame (as shown above) but with the 16 bits of data on MOSI line ignored by TC358768XBG. This step provides the 15 bits index address of the TC358768XBG register to be accessed. The only difference in this step from Write frame is that the command bit is set to 1 (Read command). During the second frame period, the TC358768XBG stuffs the read data into the bit slots 15 to 0 based on the data from the TC358768XBG register indexed by the read command address in the first frame as shown below. Handling of MISO line during first frame period and MOSI line during the second frame period is discussed further in full-duplex mode section.

Figure 3-14 Register Read (Normal) Transfer over SPI (transfer size=32 bits)

#### 3.9.2 Full Duplex

All above transactions are considered as full duplex by TC358768XBG by default. During any frame, TC358768XBG inserts the data from the TC358768XBG register that was last addressed by the read command from the SPI master into the bit slots 15 to 0 of the frame on MISO line. During any frame, the bits on the MOSI line bit slots 31 to 17 are considered as the address with the bit slot 16 providing the command. Data on MOSI line during bit slots 15 to 0 are used as write data.

The data on MISO line during bit slots 15 to 0 always corresponds to the previous frame's read command and can be ignored by the SPI Master if the previous frame command was a read command.

The data on MOSI line during bit slots 31 to 17 always provides the address for the TC358768XBG register for the current frame command.

The data on MOSI line during bit slots 15 to 0 will always be written into the TC358768XBG register addressed by current frame's address bits (bit slots 31 to 17) if the command in the current frame is a write command.

Four scenarios are possible for back to back transactions as explained below.

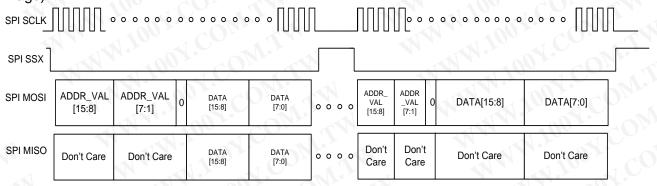

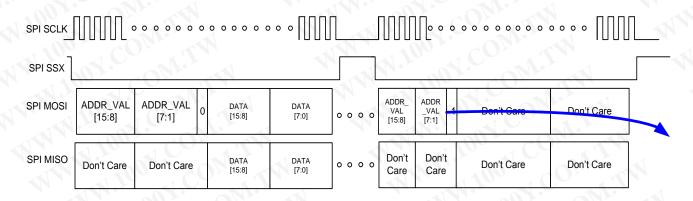

#### 3.9.2.1 Back-2-back writes

In this case, the data on the MOSI line is always valid during both back-2-back frames and used for TC358768XBG register writes. The data on the MISO line in first frame might correspond to a read command issued in the previous frame. Data on the MISO line in 2<sup>nd</sup> frame is redundant (corresponds to the TC358768XBG register addressed by the last read command some frames ago).

Figure 3-15 Back-2-Back Write Transfers over SPI

#### 3.9.2.2 Back-2-back reads

In this case, the data on the MOSI line is always valid only during first 16 bits (bit slots 31 to 16) in both back-2-back frames and used for TC358768XBG register reads. The data on the MISO line in first frame might correspond to a read command issued in the previous frame. Data on the MISO line in 2<sup>nd</sup> frame corresponds to the TC358768XBG register addressed by the read command in 1<sup>st</sup> frame. The read data corresponding to the register addressed by the read command in 2<sup>nd</sup> frame shall be available in the next (3<sup>rd</sup>) frame on MISO line.

Figure 3-16 Back-2-Back Read Transfers over SPI

#### 3.9.2.3 Write-after-Read

In this case, the handling of data on MISO and MOSI lines during first frame is similar to the "Back-to-Back reads" case. Data on the MOSI line during first 16 bits (bit slots 31 to 16) in 2<sup>nd</sup> frame provides the address and command for the write (write-after-read). Data on the MOSI line during bit slots 15 to 0 in 2<sup>nd</sup> frame provides the write data for the write command. Data on the MISO line in 2<sup>nd</sup> frame corresponds to the TC358768XBG register addressed by the read command in 1<sup>st</sup> frame.

Figure 3-17 Write-after-Read Transfer over SPI

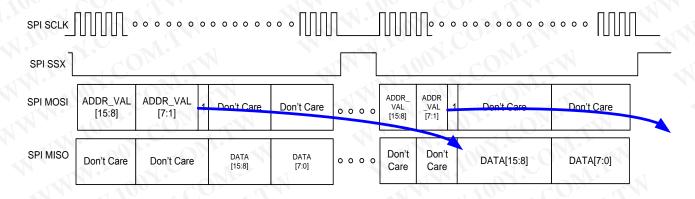

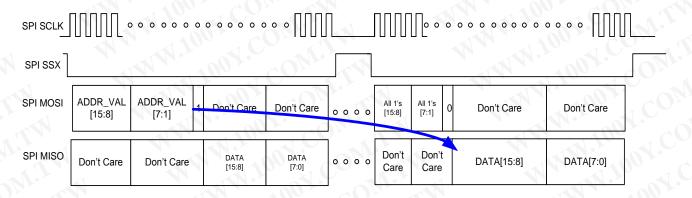

#### 3.9.2.4 Read-after-Write

In this case, the handling of data on MISO and MOSI lines during first frame is similar to the "Back-to-Back writes" case. Data on the MOSI line during first 16 bits (bit slots 31 to 16) in 2<sup>nd</sup> frame provides the address and command for the read (read-after-write). Data on the MOSI line during bit slots 15 to 0 in 2<sup>nd</sup> frame is redundant. Data on the MISO line in 2<sup>nd</sup> frame is redundant. The read data corresponding to the register addressed by the read command in 2<sup>nd</sup> frame shall be available in the next (3<sup>rd</sup>) frame on MISO line.

Figure 3-18 Read-after-Write Transfer over SPI

#### 3.9.2.5 NOP-after-Read

In this case, where there is a read alone followed by no more immediate request, the handling of data on MISO and MOSI lines during first frame is similar to the "Back-to-Back reads" case. Data on the MOSI line during first 16 bits (bit slots 31 to 16) in 2<sup>nd</sup> frame should contain all 1's to point to a dummy address for SPI and command for the write. Data on the MOSI line during bit slots 15 to 0 in 2<sup>nd</sup> frame is redundant. Data on the MISO line in 2<sup>nd</sup> frame corresponds to the TC358768XBG register addressed by the read command in 1<sup>st</sup> frame. The write on MOSI line in 2<sup>nd</sup> frame points to a dummy address (all 1's) and so redundant.

Figure 3-19 NOP-after-Read Transfer over SPI

## 4 Clock and System

The clock generation unit (CG) makes use of a single PLL. PLL Clock output frequency is same as DSITX Bit clock frequency. DSITX Byte clock will be used for DSITX controller and Video Buffer controller. PCLK input will be used for Parallel port input controller. Rest of the module will used either REFCLK or PCLK/4.

PLL uses either an external input clock REFCLK (6MHz to 40 MHz) or PCLK/4 to generate PLL Refclk. After reset, if REFCLK is not present on the system, automatically TC358768XBG will select PCLK/4 as the clock source.

#### 4.1.1 Example of PLL Generated Clock Frequency

The possible clock frequencies generated from the PLL are achieved by varying the values in registers PLLFBD and PLLDiv.

Table 4-1 provides possible frequencies that may be used in TC358768XBG.

Reference clock (MHz) **FBD** PRD FRS pll clk (MHz) (REFCLK or PCLK/4) 255 7 1 265.60 319 5 2 221.33 6 2 319 189.71 319 2 166.00

**Table 4-1 Possible PLL parameters**

**Table 4-2 Controllers' Operating Frequency**

| Controllers                | Operating Frequency |           | Source               |

|----------------------------|---------------------|-----------|----------------------|

|                            | min (MHz)           | max (MHz) |                      |

| VB controller (Write port) | 10                  | 166       | Input PCLK           |

| VB controller (Read port)  |                     | 125       | DSI Byte clock (PLL) |

| Parallel Input controller  |                     | 166       | Input PCLK           |

| SPI/I2C controller         | 6                   | 40        | Input REFCLK         |

| Register module            | 6                   | 40        | Input REFCLK         |

Confidential

Page 36 of 92

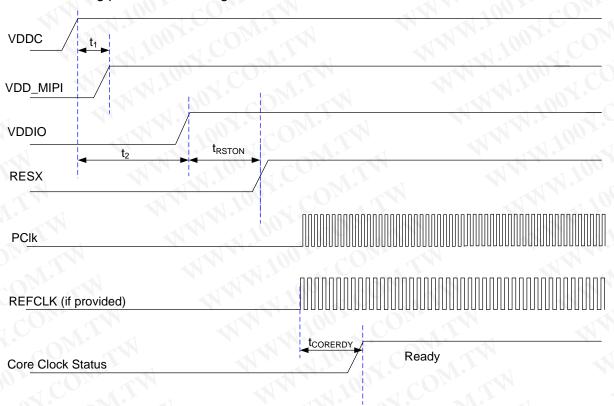

### 4.1.2 TC358768XBG Power Up Procedure

The following sequence should happen before TC358768XBG is able to operate properly:

- 1. Provide voltage and clock sources to TC358768XBG.

- 2. For voltage source, it is desired to turn on core power (1.2) source first, then Analog PHY and IO power as shown in Figure 4-1 Power On Sequence.

- RefClk, PClk/4, clock source can be from 6 MHz to 40 MHz. PClk has to toggle first before accessing/programing TC358768XBG.

- 4. The timing parameters for Figure 4-1 are tabulated in Table 4-3.

Figure 4-1 Power On Sequence

| Table 4-3 Power On Sequence Timing |  | Table | 4-3 | <b>Power</b> | On | Sec | uence | <b>Timin</b> | q |

|------------------------------------|--|-------|-----|--------------|----|-----|-------|--------------|---|

|------------------------------------|--|-------|-----|--------------|----|-----|-------|--------------|---|

| <b>Parameters</b>    | Description                                                                                        | Min. | Тур.  | Max.     | Units |

|----------------------|----------------------------------------------------------------------------------------------------|------|-------|----------|-------|

| RefClk               | Reference clock frequency                                                                          | 6    |       | 40       | MHz   |

| $t_1$                | VDD_MIPI on delay from VDDC.                                                                       | 0    | GU    | 10       | msec  |

| t <sub>2</sub>       | VDDIO on delay from VDDC                                                                           | 0    |       | 10       | msec  |

| t <sub>RSTON</sub>   | RESET width period                                                                                 | 200  | J-7-C | <u> </u> | nsec  |

| t <sub>CORERDY</sub> | Period after reset de-assertion when TC358768XBG clocks are stable (Dependent on REFCLK frequency) | .7   | 0     | 1        | msec  |

#### **TC358768XBG Power Down Procedure**

Figure 4-2 Power Down Sequence

**Table 4-4 Power Down Sequence Timing**

| <b>Parameters</b> | Description                       | Min. | Typ.     | Max. | Units |

|-------------------|-----------------------------------|------|----------|------|-------|

| $t_1$             | VDD_MIPI off delay from VDDIO off | 0    |          | 10   | msec  |

| $t_2$             | VDDC off delay from VDD_MIPL off  | 0    | <b>)</b> | . 10 | msec  |

### 5 RegFile Block

Host accesses TC358768XBG RegFile block to read status and/or write control registers through the I2C or SPI slave interface.

Registers in Group Global and CSITX\_CTL (Table 5-1) can be accessed as 16-bit registers. While the others have to be written as 32-bit registers, even if the upper 16-bits are all zeros.

### 5.1 Register Map

The control and status registers in TC358768XBG is provided in Table 5-1.

Table 5-1 Register Map

| Group     | Address            | Register       | Description                                  |

|-----------|--------------------|----------------|----------------------------------------------|

|           | 0x0000             | ChipID         | TC358768XBG Chip and Revision ID             |

|           | 0x0002             | SysCtl         | System Control Register                      |

|           | 0x0004             | ConfCtl        | Configuration Control Register               |

|           | 0x0006             | FiFoCtl        | FiFo Control Register                        |

|           | 0x0008             | DataFmt        | Data Format Control Register                 |

|           | 0x000E             | GPIOEn         | GPIO Enable Control Register                 |

| Global    | 0x0010             | GPIODir        | GPIO Pin Direction Control Register          |

|           | 0x0012             | GPIOIn         | GPIO Input Pin Value                         |

|           | 0x0014             | GPIOOut        | GPIO Output Pin Value                        |

|           | 0x0016             | PLLCtI0        | PLL control Register 0                       |

|           | 0x0018             | PLLCtl1        | PLL control Register 1                       |

|           | 0x0050             | DSITX_DT       | DSITX Data Type Register                     |

|           | 0x00F8             | FiFoStatus     | FiFo Underflow/Overflow Status               |

|           | 0x0100             | CLW_DPHYCONTTX | Clock Lane DPHY Tx Control register          |

|           | 0x0104             | DOW DPHYCONTTX | Data Lane0 DPHY Tx Control register          |

|           | 0x0108             | D1W_DPHYCONTTX | Data Lane1 DPHY Tx Control register          |

|           | 0x010C             | D2W_DPHYCONTTX | Data Lane2 DPHY Tx Control register          |

|           | 0x0110             | D3W_DPHYCONTTX | Data Lane3 DPHY Tx Control register          |

| TX<br>PHY | 0x0114 –<br>0x013F | Reserved       | M. D. Carling                                |

|           | 0x0140             | CLW_CNTRL      | Clock Lane DPHY Control Register             |

|           | 0x0144             | D0W_CNTRL      | Data Lane 0 DPHY Control Register            |

|           | 0x0148             | D1W_CNTRL      | Data Lane 1 DPHY Control Register            |

|           | 0x014C             | D2W_CNTRL      | Data Lane 2 DPHY Control Register            |

|           | 0x0150             | D3W_CNTRL      | Data Lane 3 DPHY Control Register            |

| -1        | 0x0200             | Reserved       |                                              |

|           | 0x0204             | STARTCNTRL     | DSITX Start Control Register                 |

|           | 0x0208             | STATUS         | DSITX Status Register                        |

|           | 0x020C             | Reserved       |                                              |

|           | 0x0210             | LINEINITCHT    | DSITX Line Initialization Control Register   |

|           | 0x0214             | LPTXTIMECNT    | SYSLPTX Timing Generation Counter            |

|           | 0x0218             | TCLK_HEADERCNT | TCLK_ZERO and TCLK_PREPARE Counter           |

| TX        | 0x021C             | TCLK_TRAILCNT  | TCLK_TRAIL Counter                           |

| PPI       | 0x0220             | THS_HEADERCNT  | THS_ZERO and THS_PREPARE Counter             |

|           | 0x0224             | TWAKEUP        | TWAKEUP Counter                              |

|           | 0x0228             | TCLK_POSTCNT   | TCLK_POST Counter                            |

|           | 0x022C             | THS_TRAILCNT   | THS_TRAIL Counter                            |

|           | 0x0230             | HSTXVREGCNT    | TX Voltage Regulator setup Wait Counter      |

|           | 0x0234             | HSTXVREGEN     | Voltage regulator enable for HSTX Data Lanes |

|           | 0x0238             | TXOPTIONCNTRL  | TX Option Control                            |

|           | 0x023C             | BTACNTRL1      | BTA Control                                  |

TC358768XBG Functional Spec

Confidential

Page 39 of 92

| N     | 0x0400-<br>0x0408  | Reserved      | MAN ODY . ON TA                            |

|-------|--------------------|---------------|--------------------------------------------|

|       | 0x040C             | DSI_CONFR     | DSI Configuration Read Register            |

| TV    | 0x0410             | RDFIFO_STATUS | DSI Command Read Data FIFO Status Register |

| TX    | 0x0430             | DSICMD_RDFIFO | DSI Command Read Data FIFO                 |

| CTRL  | 0x0500             | DSI_CONFW     | DSI TX Configure Write Register            |

|       | 0x0504 –<br>0x0517 | Reserved      | MA. M.100 21 CO.                           |

|       | 0x0518             | DSI_START     | DSI – Starts DSI-TX operation              |

|       | 0x0600             | DSICMD_TX     | DSI Command Packet Start register          |

|       | 0x0602             | DSICMD_TYPE   | DSI Command Packet Type register           |

|       | 0x0604             | DSICMD_WC     | DSI Command Packet Word Count              |

|       |                    |               |                                            |

|       | 0x0610             | DSICMD_WD0    | DSI Command Packet Data register 0         |

|       | 0x0612             | DSICMD_WD1    | DSI Command Packet Data register 1         |

|       | 0x0614             | DSICMD_WD2    | DSI Command Packet Data register 2         |

| DSITX | 0x0616             | DSICMD_WD3    | DSI Command Packet Data register 3         |

| CTRL  |                    |               |                                            |

|       | 0x0620             | DSI_EVENT     | DSI Hsync Event Mode                       |

|       | 0x0622             | DSI_VSW       | DSI Vsync Width register                   |

|       | 0x0624             | DSI_VBPR      | DSI Vsync Back Porch lines register        |

|       | 0x0626             | DSI_VACT      | DSI Vsync Active lines register            |