# High Voltage Latch-Up Proof, **Quad SPST Switches**

# ADG5212/ADG5213

#### **FEATURES**

Latch-up proof 3 pF off source capacitance 5 pF off drain capacitance 0.07 pC charge injection Low leakage: 0.2 nA maximum at 85°C ±9 V to ±22 V dual-supply operation 9 V to 40 V single-supply operation 48 V supply maximum ratings Fully specified at  $\pm 15$  V,  $\pm 20$  V,  $\pm 12$  V, and  $\pm 36$  V Vss to VDD analog signal range

#### **APPLICATIONS**

**Automatic test equipment Data acquisition** Instrumentation **Avionics** Audio and video switching **Communication systems**

#### **GENERAL DESCRIPTION**

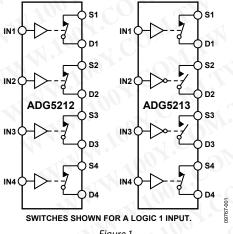

The ADG5212/ADG5213 contain four independent singlepole/single-throw (SPST) switches. The ADG5212 switches turn on with Logic 1. The ADG5213 has two switches with digital control logic similar to that of the ADG5212; however, the logic is inverted on the other two switches. Each switch conducts equally well in both directions when on, and each switch has an input signal range that extends to the supplies. In the off condition, signal levels up to the supplies are blocked.

The ADG5212 and ADG5213 do not have a V<sub>L</sub> pin. The digital inputs are compatible with 3 V logic inputs over the full operating supply range.

The ultralow capacitance and charge injection of these switches make them ideal solutions for data acquisition and sample-andhold applications, where low glitch and fast settling are required. Fast switching speed together with high signal bandwidth make the parts suitable for video signal switching.

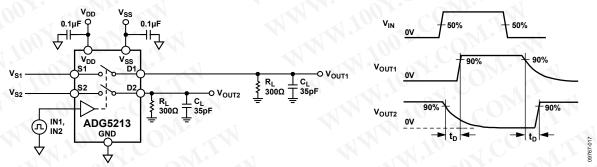

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1.

#### PRODUCT HIGHLIGHTS

- Trench Isolation Guards Against Latch-Up. A dielectric trench separates the P and N channel transistors, thereby preventing latch-up even under severe overvoltage conditions.

- Ultralow Capacitance and <1 pC Charge Injection.

- **Dual-Supply Operation.** For applications where the analog signal is bipolar, the ADG5212/ADG5213 can be operated from dual supplies of up to ±22 V.

- Single-Supply Operation. For applications where the analog signal is unipolar, the ADG5212/ADG5213 can be operated from a single rail power supply of up to 40 V.

- 3 V Logic-Compatible Digital Inputs.  $V_{INH} = 2.0 \text{ V}, V_{INL} = 0.8 \text{ V}.$

- No V<sub>L</sub> Logic Power Supply Required.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

### **TABLE OF CONTENTS**

| Features                         | 1    |

|----------------------------------|------|

| Applications                     |      |

| Functional Block Diagrams        | 1    |

| General Description              | 1 Pi |

| Product Highlights               |      |

| Revision History                 | 2 Te |

| Specifications                   | 3 Te |

| ±15 V Dual Supply                |      |

| ±20 V Dual Supply                | 4 A  |

| 12 V Single Supply               | 5 O  |

| 36 V Single Supply               | 6    |

|                                  |      |

| REVISION HISTORY                 |      |

| 4/11—Revision 0: Initial Version |      |

|                                  |      |

|                                  |      |

|                                  |      |

|                                  |      |

| Continuous Current per Channel, Sx or Dx     | /  |

|----------------------------------------------|----|

| Absolute Maximum Ratings                     | 8  |

| ESD Caution                                  | 8  |

| Pin Configurations and Function Descriptions | 9  |

| Typical Performance Characteristics          | 10 |

| Test Circuits                                |    |

| Terminology                                  | 16 |

| Trench Isolation                             |    |

| Applications Information                     | 18 |

| Outline Dimensions                           | 19 |

| Ordering Guide                               | 19 |

|                                              |    |

|                                              |    |

|                                              |    |

|                                              |    |

100×

# OM.T **REVISION HISTORY**

4/11—Revision 0: Initial Version N.COM

# **SPECIFICATIONS**

## ±15 V DUAL SUPPLY

$V_{DD}$  = +15 V ± 10%,  $V_{SS}$  = -15 V ± 10%, GND = 0 V, unless otherwise noted.

Table 1.

| Parameter                                                    | 25°C        | -40°C to +85°C | -40°C to +125°C                    | Unit        | <b>Test Conditions/Comments</b>                                        |

|--------------------------------------------------------------|-------------|----------------|------------------------------------|-------------|------------------------------------------------------------------------|

| ANALOG SWITCH                                                |             |                | 1111                               | 21          |                                                                        |

| Analog Signal Range                                          |             | N              | V <sub>DD</sub> to V <sub>SS</sub> | V max       |                                                                        |

| On Resistance, R <sub>ON</sub>                               | 160         |                | W                                  | Ω typ       | $V_s = \pm 10 \text{ V}, I_s = -1 \text{ mA},$<br>see Figure 24        |

|                                                              | 200         | 250            | 280                                | Ω max       | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}$                   |

| On-Resistance Match Between Channels, ΔR <sub>ON</sub>       | 2           | . 1            |                                    | Ωtyp        | $V_s = \pm 10 \text{ V}, I_s = -1 \text{ mA}$                          |

|                                                              | 8           | 9              | 10                                 | Ω max       |                                                                        |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                | 38          |                |                                    | Ωtyp        | $V_s = \pm 10 \text{ V}, I_s = -1 \text{ mA}$                          |

| 100                                                          | 50          | 65             | 70                                 | Ω max       | 00 , 00                                                                |

| LEAKAGE CURRENTS                                             |             |                |                                    |             | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                   |

| Source Off Leakage, Is (Off)                                 | 0.01        |                |                                    | nA typ      | $V_S = \pm 10 \text{ V}, V_D = \mp 10 \text{ V},$                      |

|                                                              | 41          |                | .4                                 | W .         | $v_s = \pm 10 \text{ V}, v_D = + 10 \text{ V},$<br>see Figure 23       |

|                                                              | 0.1         | 0.2            | 0.4                                | nA max      | See Figure 25                                                          |

| Drain Off Leakage, I <sub>D</sub> (Off)                      | 0.01        | 0.2            | 0.4                                | nA typ      | 313                                                                    |

| Dialif Off Leakage, ID (Off)                                 | 0.01        |                |                                    | па сур      | $V_S = \pm 10 \text{ V}, V_D = \mp 10 \text{ V},$                      |

|                                                              | 0.1         | 0.2            | 0.4                                | n A m s     | see Figure 23                                                          |

|                                                              | 0.1         | 0.2            | 0.4                                | nA max      | (A) 11 (A)                                                             |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On) | 0.02        | -1             |                                    | nA typ      | $V_S = V_D = \pm 10 \text{ V, see Figure 26}$                          |

|                                                              | 0.2         | 0.25           | 0.9                                | nA max      |                                                                        |

| DIGITAL INPUTS                                               | ~1 <b>1</b> |                |                                    | 4           | 100                                                                    |

| Input High Voltage, V <sub>INH</sub>                         | M.          |                | 2.0                                | V min       |                                                                        |

| Input Low Voltage, V <sub>INL</sub>                          | 1           | 100            | 0.8                                | V max       | 100                                                                    |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>          | 0.002       |                |                                    | μA typ      | $V_{IN} = V_{GND}$ or $V_{DD}$                                         |

|                                                              | M.          | 1100           | ±0.1                               | μA max      | 100                                                                    |

| Digital Input Capacitance, C <sub>IN</sub>                   | 3           |                |                                    | pF typ      |                                                                        |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                         |             | 100            | CON                                |             | 10                                                                     |

| ton                                                          | 175         |                |                                    | ns typ      | $R_L = 300 \Omega, C_L = 35 pF$                                        |

|                                                              | 210         | 255            | 280                                | ns max      | $V_s = 10 V$ , see Figure 30                                           |

| toff                                                         | 140         |                |                                    | ns typ      | $R_L = 300 \Omega, C_L = 35 pF$                                        |

|                                                              | 170         | 195            | 215                                | ns max      | V <sub>s</sub> = 10 V, see Figure 30                                   |

| Break-Before-Make Time Delay, t <sub>D</sub>                 | 40          |                |                                    | ns typ      | $R_L = 300 \Omega, C_L = 35 pF$                                        |

| (ADG5213 Only)                                               |             |                | 400 3                              |             |                                                                        |

|                                                              |             |                | 20                                 | ns min      | $V_{S1} = V_{S2} = 10 \text{ V, see Figure 29}$                        |

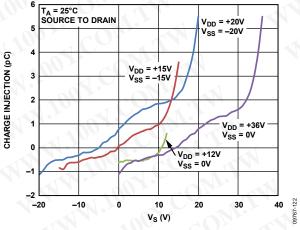

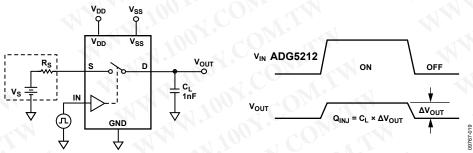

| Charge Injection, Q <sub>INJ</sub>                           | 0.07        |                | 1100                               | pC typ      | $V_S = 0 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF},$ see Figure 31 |

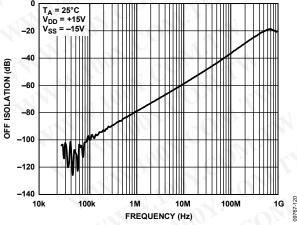

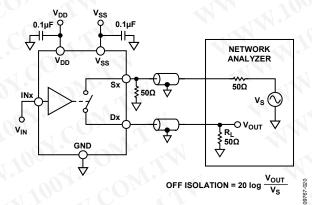

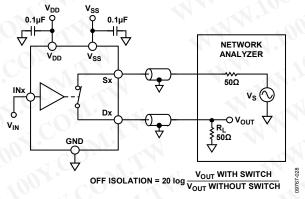

| Off Isolation                                                | -105        |                | 1007                               | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 25         |

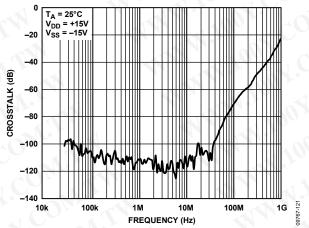

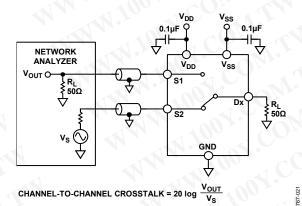

| Channel-to-Channel Crosstalk                                 | -105        |                | NAN., UO                           | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 27         |

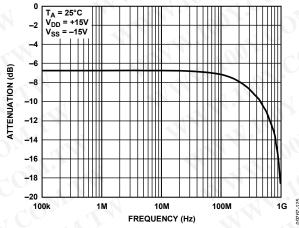

| –3 dB Bandwidth                                              | 435         |                | . Al. I                            | MHz typ     | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 2                        |

| Insertion Loss                                               | -6.8        |                | 11/1/1/10                          | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 28         |

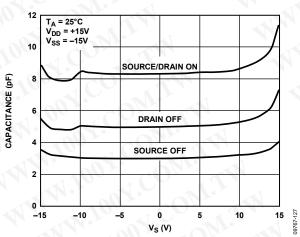

| C <sub>s</sub> (Off)                                         | 3           |                |                                    | pF typ      | $V_S = 0 \text{ V, } f = 1 \text{ MHz}$                                |

| C <sub>D</sub> (Off)                                         | 5           |                | 1                                  | pF typ      | $V_S = 0 V, f = 1 MHz$                                                 |

| $C_D$ (On), $C_S$ (On)                                       | 8           | A)             |                                    | pF typ      | $V_S = 0 V, f = 1 MHz$                                                 |

| POWER REQUIREMENTS                                           |             |                |                                    | 110         | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                   |

| $I_{DD}$                                                     | 45          |                | 1                                  | μA typ      | Digital inputs = 0 V or V <sub>DD</sub>                                |

|                                                              | 55          |                | 70                                 | μA max      |                                                                        |

| Iss                                                          | 0.001       | •              |                                    | μΑ typ      | Digital inputs = 0 V or V <sub>DD</sub>                                |

| 100                                                          | M.          |                | 1                                  | μA max      | D 2 40 x                                                               |

| $V_{DD}/V_{SS}$                                              | -           | 1.             | ±9/±22                             | V min/V max | GND = 0 V                                                              |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

#### **±20 V DUAL SUPPLY**

$V_{DD}$  = +20 V ± 10%,  $V_{SS}$  = -20 V ± 10%, GND = 0 V, unless otherwise noted.

Table 2

| Parameter                                                      | 25°C  | -40°C to +85°C | -40°C to +125°C                    | Unit      | <b>Test Conditions/Comments</b>                                           |

|----------------------------------------------------------------|-------|----------------|------------------------------------|-----------|---------------------------------------------------------------------------|

| ANALOG SWITCH                                                  |       |                |                                    | 1.        |                                                                           |

| Analog Signal Range                                            | QO M  |                | V <sub>DD</sub> to V <sub>SS</sub> | V max     | CONTRA                                                                    |

| On Resistance, R <sub>ON</sub>                                 | 140   |                |                                    | Ωtyp      | $V_S = \pm 15 \text{ V}, I_S = -1 \text{ mA},$<br>see Figure 24           |

|                                                                | 160   | 200            | 230                                | Ω max     | $V_{DD} = +18 \text{ V}, V_{SS} = -18 \text{ V}$                          |

| On-Resistance Match Between<br>Channels, ARon                  | 1.5   | DEVITA         |                                    | Ωtyp      | $V_S = \pm 15 \text{ V, } I_S = -1 \text{ mA}$                            |

|                                                                | 8     | 9              | 10                                 | Ω max     | 100 x 0 1 1 1                                                             |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                  | 33    |                |                                    | Ωtyp      | $V_S = \pm 15 \text{ V}, I_S = -1 \text{ mA}$                             |

|                                                                | 45    | 55             | 60                                 | Ω max     | 100 200                                                                   |

| LEAKAGE CURRENTS                                               |       |                | -1                                 |           | $V_{DD} = +22 \text{ V}, V_{SS} = -22 \text{ V}$                          |

| Source Off Leakage, Is (Off)                                   | 0.01  | CON            |                                    | nA typ    | $V_S = \pm 15 \text{ V}, V_D = \mp 15 \text{ V},$ see Figure 23           |

|                                                                | 0.1   | 0.2            | 0.4                                | nA max    | see rigure 25                                                             |

| Drain Off Leakage, I <sub>D</sub> (Off)                        | 0.01  | 0.2            | 0.4                                | nA typ    |                                                                           |

| Brain on Ecakage, is (on)                                      |       | 700 T.C.       |                                    |           | $V_S = \pm 15 \text{ V}, V_D = \mp 15 \text{ V},$ see Figure 23           |

|                                                                | 0.1   | 0.2            | 0.4                                | nA max    | 100                                                                       |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On)   | 0.02  | N. V.          |                                    | nA typ    | $V_S = V_D = \pm 15 \text{ V, see Figure 26}$                             |

| OF                                                             | 0.2   | 0.25           | 0.9                                | nA max    |                                                                           |

| DIGITAL INPUTS                                                 |       |                |                                    | <b>41</b> |                                                                           |

| Input High Voltage, V <sub>INH</sub>                           |       | 100            | 2.0                                | V min     | 100                                                                       |

| Input Low Voltage, V <sub>INL</sub>                            |       |                | 0.8                                | V max     | M. IN.                                                                    |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>            | 0.002 | 10             | $0 \sim 0_{\rm M}$                 | μA typ    | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                     |

|                                                                |       |                | ±0.1                               | μA max    | M. M.                                                                     |

| Digital Input Capacitance, C <sub>IN</sub>                     | 3     |                | $00^{\circ}$                       | pF typ    |                                                                           |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                           |       |                |                                    |           |                                                                           |

| ton                                                            | 155   |                | 100                                | ns typ    | $R_L = 300 \Omega$ , $C_L = 35 pF$                                        |

|                                                                | 195   | 235            | 255                                | ns max    | $V_s = 10 V$ , see Figure 30                                              |

| toff                                                           | 145   |                | 1100                               | ns typ    | $R_L = 300 \Omega,  C_L = 35  pF$                                         |

|                                                                | 165   | 185            | 210                                | ns max    | $V_s = 10 V$ , see Figure 30                                              |

| Break-Before-Make Time Delay, t <sub>D</sub><br>(ADG5213 Only) | 35    |                | 111.100                            | ns typ    | $R_L = 300 \Omega$ , $C_L = 35 pF$                                        |

|                                                                |       |                | 20                                 | ns min    | $V_{S1} = V_{S2} = 10 \text{ V, see Figure 29}$                           |

| Charge Injection, Q <sub>INJ</sub>                             | -0.5  |                | 10                                 | pC typ    | $V_S = 0 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF},$<br>see Figure 31 |

| Off Isolation                                                  | -105  | N              |                                    | dB typ    | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 25            |

| Channel-to-Channel Crosstalk                                   | -105  | M              | W. W.                              | dB typ    | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 27            |

| –3 dB Bandwidth                                                | 460   |                |                                    | MHz typ   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 28                          |

| Insertion Loss                                                 | -6    | W.             |                                    | dB typ    | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 28            |

| Cs (Off)                                                       | 2.8   |                |                                    | pF typ    | $V_S = 0 V, f = 1 MHz$                                                    |

| C <sub>D</sub> (Off)                                           | 4.8   | Oh, WA         |                                    | pF typ    | $V_S = 0 V, f = 1 MHz$                                                    |

| $C_D$ (On), $C_S$ (On)                                         | 8     |                |                                    | pF typ    | $V_s = 0 V, f = 1 MHz$                                                    |

| Parameter                        | 25°C  | -40°C to +85°C | -40°C to +125°C | Unit        | Test Conditions/Comments                         |

|----------------------------------|-------|----------------|-----------------|-------------|--------------------------------------------------|

| POWER REQUIREMENTS               | 1     |                | 1111.           |             | $V_{DD} = +22 \text{ V}, V_{SS} = -22 \text{ V}$ |

| I <sub>DD</sub>                  | 50    |                | 100             | μA typ      | Digital inputs = 0 V or V <sub>DD</sub>          |

|                                  | 70    |                | 110             | μA max      | M. T                                             |

| Iss                              | 0.001 |                |                 | μA typ      | Digital inputs = 0 V or V <sub>DD</sub>          |

|                                  |       |                | 1               | μA max      |                                                  |

| V <sub>DD</sub> /V <sub>SS</sub> | CO    |                | ±9/±22          | V min/V max | GND = 0 V                                        |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

#### 12 V SINGLE SUPPLY

$V_{DD}$  = 12 V ± 10%,  $V_{SS}$  = 0 V, GND = 0 V, unless otherwise noted.

Table 3.

| Parameter                                                      | 25°C  | -40°C to +85°C | -40°C to +125°C                         | Unit    | Test Conditions/Comments                                                        |

|----------------------------------------------------------------|-------|----------------|-----------------------------------------|---------|---------------------------------------------------------------------------------|

| ANALOG SWITCH                                                  |       | M. M           |                                         |         |                                                                                 |

| Analog Signal Range                                            | 1     |                | 0 V to V <sub>DD</sub>                  | V max   | 100, 60, 4                                                                      |

| On Resistance, Ron                                             | 350   | ON             | 1                                       | Ωtyp    | $V_s = 0 \text{ V to } 10 \text{ V, } I_s = -1 \text{ mA,}$ see Figure 24       |

|                                                                | 500   | 610            | 700                                     | Ωmax    | $V_{DD} = 10.8 \text{ V}, V_{SS} = 0 \text{ V}$                                 |

| On-Resistance Match Between Channels, ΔR <sub>ON</sub>         | 4     | (O)            |                                         | Ωtyp    | $V_s = 0 \text{ V to } 10 \text{ V}, I_s = -1 \text{ mA}$                       |

|                                                                | 20    | 21             | 22                                      | Ω max   |                                                                                 |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                  | 160   |                |                                         | Ωtyp    | $V_s = 0 \text{ V to } 10 \text{ V, } I_s = -1 \text{ mA}$                      |

|                                                                | 280   | 335            | 370                                     | Ω max   |                                                                                 |

| LEAKAGE CURRENTS                                               | - 40  |                |                                         |         | $V_{DD} = 13.2 \text{ V}, V_{SS} = 0 \text{ V}$                                 |

| Source Off Leakage, I <sub>s</sub> (Off)                       | 0.01  | 100%           | MI                                      | nA typ  | $V_S = 1 \text{ V}/10 \text{ V}, V_D = 10 \text{ V}/1 \text{ V},$ see Figure 23 |

|                                                                | 0.1   | 0.2            | 0.4                                     | nA max  |                                                                                 |

| Drain Off Leakage, I <sub>D</sub> (Off)                        | 0.01  | 1.100          | CONTAIN                                 | nA typ  | $V_S = 1 \text{ V}/10 \text{ V}, V_D = 10 \text{ V}/1 \text{ V},$ see Figure 23 |

|                                                                | 0.1   | 0.2            | 0.4                                     | nA max  |                                                                                 |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On)   | 0.02  | M. Ju          | COM.                                    | nA typ  | $V_S = V_D = 1 \text{ V}/10 \text{ V},$<br>see Figure 26                        |

|                                                                | 0.2   | 0.25           | 0.9                                     | nA max  |                                                                                 |

| DIGITAL INPUTS                                                 |       |                | 11.                                     |         |                                                                                 |

| Input High Voltage, V <sub>INH</sub>                           |       |                | 2.0                                     | V min   |                                                                                 |

| Input Low Voltage, V <sub>INL</sub>                            |       |                | 0.8                                     | V max   |                                                                                 |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>            | 0.002 |                | 100 at CO                               | μA typ  | $V_{IN} = V_{GND}$ or $V_{DD}$                                                  |

|                                                                |       |                | ±0.1                                    | μA max  | - (1)                                                                           |

| Digital Input Capacitance, C <sub>IN</sub>                     | 3     |                | 133 Z C                                 | pF typ  |                                                                                 |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                           |       |                | , , , , , , , , , , , , , , , , , , , , |         |                                                                                 |

| ton                                                            | 235   |                | 41.70                                   | ns typ  | $R_L = 300 \Omega, C_L = 35 pF$                                                 |

|                                                                | 290   | 360            | 410                                     | ns max  | $V_s = 8 V$ , see Figure 30                                                     |

| toff                                                           | 165   |                |                                         | ns typ  | $R_L = 300 \Omega, C_L = 35 pF$                                                 |

|                                                                | 205   | 235            | 260                                     | ns max  | $V_s = 8 V$ , see Figure 30                                                     |

| Break-Before-Make Time Delay, t <sub>D</sub><br>(ADG5213 Only) | 85    |                | M. M. Jo.                               | ns typ  | $R_L = 300 \ \Omega, \ C_L = 35 \ pF$                                           |

|                                                                |       |                | 50                                      | ns min  | $V_{51} = V_{52} = 8 \text{ V, see Figure 29}$                                  |

| Charge Injection, Q <sub>INJ</sub>                             | -0.5  | N              |                                         | pC typ  | $V_S = 6 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF},$<br>see Figure 31       |

| Off Isolation                                                  | -105  |                |                                         | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ see Figure 25                    |

| Channel-to-Channel Crosstalk                                   | -105  |                |                                         | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ see Figure 27                    |

| –3 dB Bandwidth                                                | 340   | M.             |                                         | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 28                                |

| Parameter              | 25°C         | -40°C to +85°C | -40°C to +125°C | Unit        | <b>Test Conditions/Comments</b>                              |

|------------------------|--------------|----------------|-----------------|-------------|--------------------------------------------------------------|

| Insertion Loss         | -11          |                | 11/1/12         | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ see Figure 28 |

| C <sub>s</sub> (Off)   | 3.5          |                | 1               | pF typ      | $V_s = 6 V, f = 1 MHz$                                       |

| C <sub>D</sub> (Off)   | 5.5          |                |                 | pF typ      | $V_s = 6 V, f = 1 MHz$                                       |

| $C_D$ (On), $C_S$ (On) | 9            | -1             |                 | pF typ      | $V_s = 6 V, f = 1 MHz$                                       |

| POWER REQUIREMENTS     | (O)          |                |                 | 100,        | V <sub>DD</sub> = 13.2 V                                     |

| l <sub>DD</sub>        | 40           | -1             |                 | μA typ      | Digital inputs = 0 V or V <sub>DD</sub>                      |

|                        | $\neg O_{N}$ |                | 65              | μA max      |                                                              |

| $V_{DD}$               |              |                | 9/40            | V min/V max | $GND = 0 V, V_{SS} = 0 V$                                    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

#### **36 V SINGLE SUPPLY**

$V_{DD}$  = 36 V ± 10%,  $V_{SS}$  = 0 V, GND = 0 V, unless otherwise noted.

Table 4.

| Parameter                                                      | 25°C  | -40°C to +85°C | -40°C to +125°C        | Unit   | Test Conditions/Comments                                                        |

|----------------------------------------------------------------|-------|----------------|------------------------|--------|---------------------------------------------------------------------------------|

| ANALOG SWITCH                                                  | 100   | COA            |                        | J1"    | 4N 400 x 201                                                                    |

| Analog Signal Range                                            |       | 1.0            | 0 V to V <sub>DD</sub> | V max  |                                                                                 |

| On Resistance, R <sub>ON</sub>                                 | 150   | OD COD         |                        | Ωtyp   | $V_S = 0 \text{ V to } 30 \text{ V}, I_S = -1 \text{ mA},$<br>see Figure 24     |

|                                                                | 170   | 215            | 245                    | Ω max  | $V_{DD} = 32.4 \text{ V}, V_{SS} = 0 \text{ V}$                                 |

| On-Resistance Match Between Channels, $\Delta R_{ON}$          | 1.6   |                |                        | Ωtyp   | $V_s = 0 \text{ V to } 30 \text{ V, } I_s = -1 \text{ mA}$                      |

|                                                                | 8     | 9              | 10                     | Ω max  | 100                                                                             |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                  | 35    |                |                        | Ωtyp   | $V_s = 0 V \text{ to } 30 V, I_s = -1 \text{ mA}$                               |

|                                                                | 50    | 60             | 65                     | Ω max  | 00                                                                              |

| LEAKAGE CURRENTS                                               |       |                |                        |        | $V_{DD} = 39.6 \text{ V}, V_{SS} = 0 \text{ V}$                                 |

| Source Off Leakage, Is (Off)                                   | 0.01  | 17,100         | COM                    | nA typ | $V_S = 1 \text{ V}/30 \text{ V}, V_D = 30 \text{ V}/1 \text{ V},$ see Figure 23 |

|                                                                | 0.1   | 0.2            | 0.4                    | nA max |                                                                                 |

| Drain Off Leakage, I <sub>D</sub> (Off)                        | 0.01  | 1,111,10       | odi.Co.                | nA typ | $V_S = 1 \text{ V}/30 \text{ V}, V_D = 30 \text{ V}/1 \text{ V},$ see Figure 23 |

|                                                                | 0.1   | 0.2            | 0.4                    | nA max |                                                                                 |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On)   | 0.02  |                | 1007                   | nA typ | $V_S = V_D = 1 \text{ V}/30 \text{ V},$<br>see Figure 26                        |

|                                                                | 0.2   | 0.25           | 0.9                    | nA max |                                                                                 |

| DIGITAL INPUTS                                                 |       |                | 100                    | COF    |                                                                                 |

| Input High Voltage, V <sub>INH</sub>                           |       |                | 2.0                    | V min  | No.                                                                             |

| Input Low Voltage, V <sub>INL</sub>                            |       |                | 0.8                    | V max  |                                                                                 |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>            | 0.002 |                | 1111                   | μA typ | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                           |

|                                                                |       | 41             | ±0.1                   | μA max |                                                                                 |

| Digital Input Capacitance, C <sub>IN</sub>                     | 3     |                |                        | pF typ |                                                                                 |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                           | 1     |                |                        | 00     | D. CA                                                                           |

| t <sub>ON</sub>                                                | 190   | S.             | J. M.                  | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$                                              |

|                                                                | 230   | 255            | 265                    | ns max | $V_s = 18 \text{ V}$ , see Figure 30                                            |

| toff                                                           | 175   |                |                        | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$                                              |

| 10° 10°                                                        | 215   | 230            | 245                    | ns max | $V_s = 18 \text{ V}$ , see Figure 30                                            |

| Break-Before-Make Time Delay, t <sub>D</sub><br>(ADG5213 Only) | 45    |                |                        | ns typ | $R_L = 300 \Omega, C_L = 35 pF$                                                 |

|                                                                |       | 1.             | 25                     | ns min | $V_{S1} = V_{S2} = 18 \text{ V, see Figure 29}$                                 |

| Charge Injection, Q <sub>INJ</sub>                             | -0.5  |                | N                      | pC typ | $V_S = 18 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF},$ see Figure 31         |

| Off Isolation                                                  | -105  |                |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 25                  |

| Channel-to-Channel Crosstalk                                   | -105  | ON. TA         |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , Figure 27                      |

| –3 dB Bandwidth        |      | -40°C to +85°C | -40°C to +125°C | Unit        | Test Conditions/Comments                                       |

|------------------------|------|----------------|-----------------|-------------|----------------------------------------------------------------|

|                        | 410  |                | N. 100          | MHz typ     | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 28               |

| Insertion Loss         | -6.8 |                | MAN             | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 28 |

| C <sub>s</sub> (Off)   | 3    |                | 11.             | pF typ      | $V_s = 18 \text{ V, } f = 1 \text{ MHz}$                       |

| C <sub>D</sub> (Off)   | 5    |                |                 | pF typ      | $V_s = 18 \text{ V, } f = 1 \text{ MHz}$                       |

| $C_D$ (On), $C_S$ (On) | 8    | 4              | 11              | pF typ      | $V_s = 18 \text{ V, } f = 1 \text{ MHz}$                       |

| POWER REQUIREMENTS     |      | N              |                 | 100,20      | $V_{DD} = 39.6 \text{ V}$                                      |

| $I_{DD}$               | 80   |                |                 | μA typ      | Digital inputs = $0 \text{ V or V}_{DD}$                       |

|                        | 100  |                | 130             | μA max      |                                                                |

| $V_{DD}$               |      |                | 9/40            | V min/V max | $GND = 0  V,  V_{SS} = 0  V$                                   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

#### CONTINUOUS CURRENT PER CHANNEL, Sx OR Dx

Table 5.

| Parameter                                         | 25°C     | 85°C | 125°C | Unit       |

|---------------------------------------------------|----------|------|-------|------------|

| CONTINUOUS CURRENT, Sx or Dx                      |          | . 4  |       | 1          |

| $V_{DD} = +15 \text{ V}, V_{SS} = -15 \text{ V}$  |          | N    | _     | ~003       |

| TSSOP ( $\theta_{JA} = 112.6^{\circ}\text{C/W}$ ) | 18       | 10   | 5     | mA maximum |

| LFCSP ( $\theta_{JA} = 30.4$ °C/W)                | 32       | 15   | 6     | mA maximum |

| $V_{DD} = +20 \text{ V}, V_{SS} = -20 \text{ V}$  |          | 1.51 |       |            |

| TSSOP ( $\theta_{JA} = 112.6^{\circ}\text{C/W}$ ) | 29       | 16   | 8     | mA maximum |

| LFCSP ( $\theta_{JA} = 30.4$ °C/W)                | 50       | 22   | 9     | mA maximum |

| $V_{DD} = 12 \text{ V}, V_{SS} = 0 \text{ V}$     | 1400 J   | 15   | _     |            |

| TSSOP ( $\theta_{JA} = 112.6^{\circ}\text{C/W}$ ) | 18       | 12   | 7     | mA maximum |

| LFCSP ( $\theta_{JA} = 30.4^{\circ}C/W$ )         | 32       | 17   | 8     | mA maximum |

| $V_{DD} = 36 \text{ V}, V_{SS} = 0 \text{ V}$     | 24       | 10   |       |            |

| TSSOP ( $\theta_{JA} = 112.6^{\circ}\text{C/W}$ ) | 34<br>59 | 18   | 8 9   | mA maximum |

| LFCSP ( $\theta_{JA} = 30.4$ °C/W)                | 59       | 24   | 9     | mA maximum |

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 6.

| Table 0.                                      |                                                                                         |

|-----------------------------------------------|-----------------------------------------------------------------------------------------|

| Parameter                                     | Rating                                                                                  |

| V <sub>DD</sub> to V <sub>SS</sub>            | 48 V                                                                                    |

| V <sub>DD</sub> to GND                        | −0.3 V to +48 V                                                                         |

| V <sub>ss</sub> to GND                        | +0.3 V to -48 V                                                                         |

| Analog Inputs <sup>1</sup>                    | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V or}$ 30 mA, whichever occurs first    |

| Digital Inputs <sup>1</sup>                   | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V or}$<br>30 mA, whichever occurs first |

| Peak Current, Sx or Dx Pin                    | 60 mA (pulsed at 1 ms, 10% duty cycle maximum)                                          |

| Continuous Current, Sx or Dx <sup>2</sup>     | Data + 15%                                                                              |

| Temperature                                   | 1, 100 y. COB.                                                                          |

| Operating Range                               | −40°C to +125°C                                                                         |

| Storage Range                                 | −65°C to +150°C                                                                         |

| Junction                                      | 150°C                                                                                   |

| Thermal Impedance, $\theta_{JA}$              | 100,                                                                                    |

| 16-Lead TSSOP (4-Layer Board)                 | 112.6°C/W                                                                               |

| 16-Lead LFCSP (4-Layer Board)                 | 30.4°C/W                                                                                |

| Reflow Soldering Peak<br>Temperature, Pb Free | 260(+0/-5)°C                                                                            |

<sup>&</sup>lt;sup>1</sup> Overvoltages at the INx, Sx, and Dx pins are clamped by internal diodes. Limit current to the maximum ratings given.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Only one absolute maximum rating can be applied at any one time.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> See Table 5

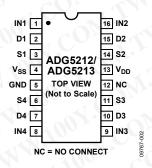

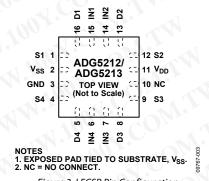

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 2. TSSOP Pin Configuration

Figure 3. LFCSP Pin Configuration

Table 7. Pin Function Descriptions

|       | Pin No. | 1111.           |                                                                                                                                                                                                        |

|-------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | LFCSP   | Mnemonic        | Description                                                                                                                                                                                            |

| 1     | 15      | IN1             | Logic Control Input.                                                                                                                                                                                   |

| 2     | 16      | D1              | Drain Terminal. This pin can be an input or an output.                                                                                                                                                 |

| 3     | 1       | S1              | Source Terminal. This pin can be an input or an output.                                                                                                                                                |

| 4     | 2       | V <sub>SS</sub> | Most Negative Power Supply Potential.                                                                                                                                                                  |

| 5     | 3       | GND             | Ground (0 V) Reference.                                                                                                                                                                                |

| 6     | 4       | S4              | Source Terminal. This pin can be an input or an output.                                                                                                                                                |

| 7     | 5       | D4              | Drain Terminal. This pin can be an input or an output.                                                                                                                                                 |

| 8     | 6       | IN4             | Logic Control Input.                                                                                                                                                                                   |

| 9     | 7       | IN3             | Logic Control Input.                                                                                                                                                                                   |

| 10    | 8       | D3              | Drain Terminal. This pin can be an input or an output.                                                                                                                                                 |

| 11    | 9       | S3              | Source Terminal. This pin can be an input or an output.                                                                                                                                                |

| 12    | 10      | NC              | No Connect. These pins are open.                                                                                                                                                                       |

| 13    | 11      | V <sub>DD</sub> | Most Positive Power Supply Potential.                                                                                                                                                                  |

| 14    | 12      | S2              | Source Terminal. This pin can be an input or an output.                                                                                                                                                |

| 15    | 13      | D2              | Drain Terminal. This pin can be an input or an output.                                                                                                                                                 |

| 16    | 14      | IN2             | Logic Control Input.                                                                                                                                                                                   |

| N/A¹  | EP      | Exposed pad     | Exposed Pad. The exposed pad is connected internally. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the substrate, Vss. |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

#### Table 8. ADG5212 Truth Table

| ADG5212 INx | Switch Condition |

|-------------|------------------|

| 1           | On               |

| 0           | Off              |

#### Table 9. ADG5213 Truth Table

| ADG5213 INx | \$1,\$4 | S2, S3 |

|-------------|---------|--------|

| 0           | Off     | On     |

| 1           | On      | Off    |

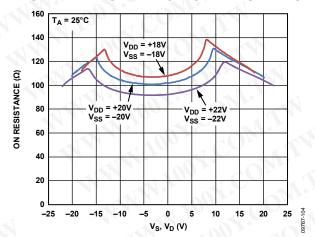

### TYPICAL PERFORMANCE CHARACTERISTICS

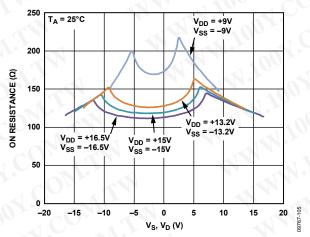

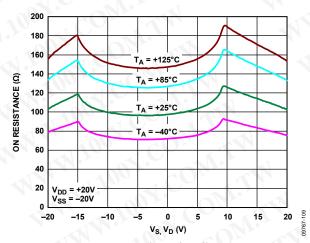

Figure 4.  $R_{ON}$  as a Function of  $V_S$ ,  $V_D$  (Dual Supply)

Figure 5.  $R_{ON}$  as a Function of  $V_S$ ,  $V_D$  (Dual Supply)

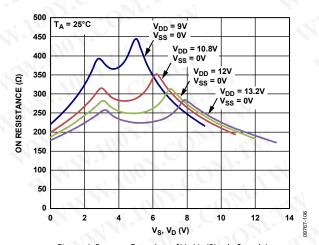

Figure 6.  $R_{ON}$  as a Function of  $V_s$ ,  $V_D$  (Single Supply)

Figure 7.  $R_{ON}$  as a Function of  $V_S$ ,  $V_D$  (Single Supply)

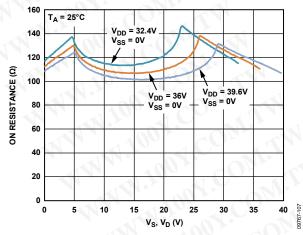

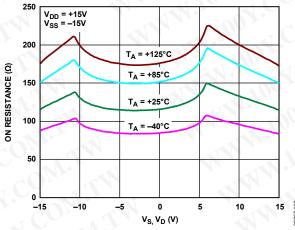

Figure 8.  $R_{ON}$  as a Function of  $V_{S}$ ,  $V_{D}$  for Different Temperatures,  $\pm 15 \text{ V}$  Dual Supply

Figure 9.  $R_{ON}$  as a Function of  $V_{S}$ ,  $V_{D}$  for Different Temperatures,  $\pm 20 \text{ V}$  Dual Supply

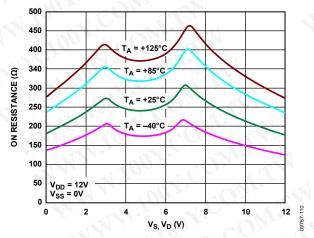

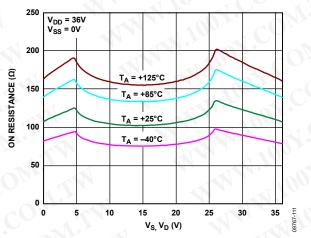

Figure 10.  $R_{ON}$  as a Function of  $V_S$ ,  $V_D$  for Different Temperatures, 12 V Single Supply

Figure 11. R<sub>ON</sub> as a Function of V<sub>S</sub>,V<sub>D</sub> for Different Temperatures, 36 V Single Supply

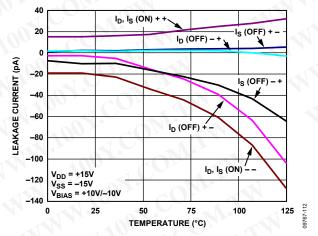

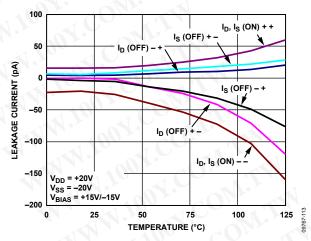

Figure 12. Leakage Currents vs. Temperature, ±15 V Dual Supply

Figure 13. Leakage Currents vs. Temperature, ±20 V Dual Supply

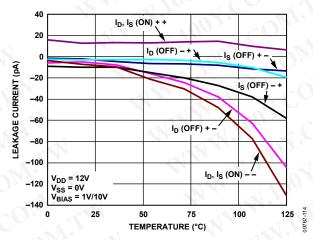

Figure 14. Leakage Currents vs. Temperature, 12 V Single Supply

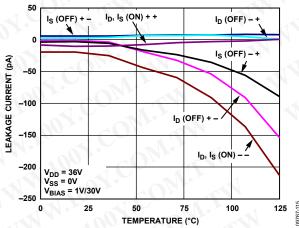

Figure 15. Leakage Currents vs. Temperature, 36 V Single Supply

Figure 16. Off Isolation vs. Frequency, ±15 V Dual Supply

Figure 17. Crosstalk vs. Frequency, ±15 V Dual Supply

Figure 18. Charge Injection vs. Source Voltage

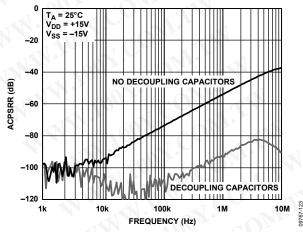

Figure 19. ACPSRR vs. Frequency, ±15 V Dual Supply

Figure 20. Bandwidth

Figure 21. Capacitance

MMN.Inn r.

NNA

MMA

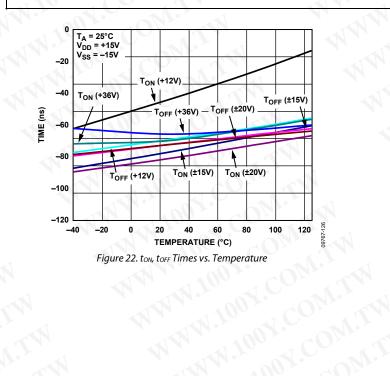

MMM.100Y.COM.TW Figure 22. ton, toff Times vs. Temperature

A. Innx.,

1001.C

WWW.look

MMM.100X.COM.

MITH

OM

WWW.100X.COM.TW

# **TEST CIRCUITS**

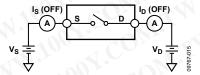

Figure 23. Off Leakage

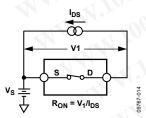

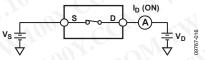

Figure 24. On Resistance

Figure 25. Off Isolation

Figure 26. On Leakage

Figure 27. Channel-to-Channel Crosstalk

Figure 28. Bandwidth

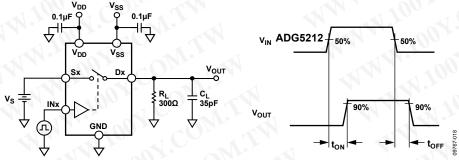

Figure 29. Break-Before-Make Time Delay, to

Figure 30. Switching Times

Figure 31. Charge Injection

### **TERMINOLOGY**

$I_{DD}$

$I_{\rm DD}$  represents the positive supply current.

Iss

Iss represents the negative supply current.

$V_D, V_S$

$V_{\text{D}}$  and  $V_{\text{S}}$  represent the analog voltage on Terminal Dx and Terminal Sx, respectively.

Ron

$R_{\mathrm{ON}}$  represents the ohmic resistance between Terminal Dx and Terminal Sx.

$\Delta R_{ON}$

$\Delta R_{\rm ON}$  represents the difference between the  $R_{\rm ON}$  of any two channels.

R<sub>FLAT(ON)</sub>

Flatness that is defined as the difference between the maximum and minimum value of on resistance measured over the specified analog signal range is represented by R<sub>FLAT(ON)</sub>.

Is (Off)

Is (Off) is the source leakage current with the switch off.

I<sub>D</sub> (Off)

I<sub>D</sub> (Off) is the drain leakage current with the switch off.

$I_D$  (On),  $I_S$  (On)

$I_D$  (On) and  $I_S$  (On) represent the channel leakage currents with the switch on.

$V_{INL}$

$V_{\text{INL}}$  is the maximum input voltage for Logic 0.

$V_{\text{INH}}$

$V_{INH}$  is the minimum input voltage for Logic 1.

IINL, IINH

$I_{\rm INL}$  and  $I_{\rm INH}$  represent the low and high input currents of the digital inputs.

C<sub>D</sub> (Off)

C<sub>D</sub> (Off) represents the off switch drain capacitance, which is measured with reference to ground.

Cs (Off)

Cs (Off) represents the off switch source capacitance, which is measured with reference to ground.

$C_D$  (On),  $C_S$  (On)

$C_D$  (On) and  $C_S$  (On) represent on switch capacitances, which are measured with reference to ground.

$C_{IN}$

C<sub>IN</sub> is the digital input capacitance.

ton

$t_{\rm ON}$  represents the delay between applying the digital control input and the output switching on (see Figure 30).

tori

toff represents the delay between applying the digital control input and the output switching off (see Figure 30).

tn

$t_{\rm D}$  represents the off time measured between the 80% point of both switches when switching from one address state to another.

Off Isolation

Off isolation is a measure of unwanted signal coupling through an off switch.

**Charge Injection**

Charge injection is a measure of the glitch impulse transferred from the digital input to the analog output during switching.

Crosstalk

Crosstalk is a measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance.

Bandwidth

Bandwidth is the frequency at which the output is attenuated by 3 dB.

On Response

On response is the frequency response of the on switch.

**Insertion Loss**

Insertion loss is the loss due to the on resistance of the switch.

AC Power Supply Rejection Ratio (ACPSRR)

AC power supply rejection ratio (ACPSRR) is the ratio of the amplitude of signal on the output to the amplitude of the modulation. This is a measure of the ability of the device to avoid coupling noise and spurious signals that appear on the supply voltage pin to the output of the switch. The dc voltage on the device is modulated by a sine wave of 0.62~V~p-p.

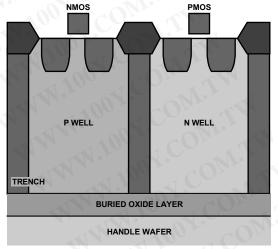

### TRENCH ISOLATION

In the ADG5212 and ADG5213, an insulating oxide layer (trench) is placed between the NMOS and the PMOS transistors of each CMOS switch. Parasitic junctions, which occur between the transistors in junction isolated switches, are eliminated, and the result is a completely latch-up proof switch.

In junction isolation, the N and P wells of the PMOS and NMOS transistors form a diode that is reverse-biased under normal operation. However, during overvoltage conditions, this diode can become forward-biased. A silicon controlled rectifier (SCR) type circuit is formed by the two transistors, causing a significant amplification of the current that, in turn, leads to latch-up. With trench isolation, this diode is removed and the result is a latch-up proof switch.

Figure 32. Trench Isolation

### APPLICATIONS INFORMATION

The ADG52xx family of switches and multiplexers provides a robust solution for instrumentation, industrial, automotive, aerospace, and other harsh environments that are prone to latch-up, which is an undesirable high current state that can lead to device failure and persists until the power supply is turned off. The ADG5212/ADG5213 high voltage switches allow single-supply operation from 9 V to 40 V and dual-supply operation from  $\pm 9$  V to  $\pm 22$  V.

08-16-2010-C

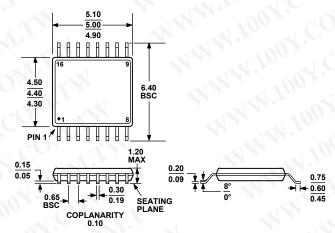

# **OUTLINE DIMENSIONS**

#### **COMPLIANT TO JEDEC STANDARDS MO-153-AB**

Figure 33. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16)

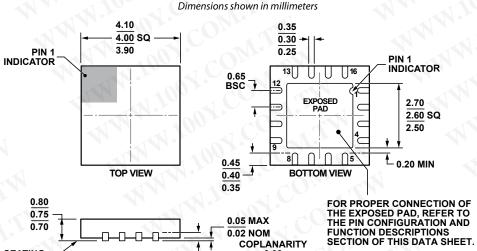

#### COMPLIANT TO JEDEC STANDARDS MO-220-WGGC.

0.20 REF

Figure 34. 16-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 4 mm × 4 mm Body, Very Very Thin Quad (CP-16-17) Dimensions shown in millimeters

COPLANARITY

0.08

#### **ORDERING GUIDE**

SEATING PLANE

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADG5212BRUZ        | -40°C to +125°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG5212BRUZ-RL7    | -40°C to +125°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG5212BCPZ-RL7    | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]  | CP-16-17       |

| ADG5213BRUZ        | -40°C to +125°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG5213BRUZ-RL7    | -40°C to +125°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG5213BCPZ-RL7    | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]  | CP-16-17       |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

| ADG5212/ADG5213 |

|-----------------|

|-----------------|

MMM.100X.COM WWW.100Y.COM.TW NOTES WWW.100Y.COM.TW

1. M. M. 100 X.

WWW.100Y.COM.TW

100X.COM.TW

CONTAN

OM.

WWW.100Y.COM.ITW

MMM.100X.COM

WWW.100X