Product specification

# Octal D-type transparent latch; 3-state

74HC/HCT573

#### **FEATURES**

- Inputs and outputs on opposite sides of package allowing easy interface with microprocessors

- Useful as input or output port for microprocessors/microcomputers

- 3-state non-inverting outputs for bus oriented applications

- Common 3-state output enable input

- Functionally identical to the "563" and "373"

- · Output capability: bus driver

- I<sub>CC</sub> category: MSI

### **GENERAL DESCRIPTION**

The 74HC/HCT573 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

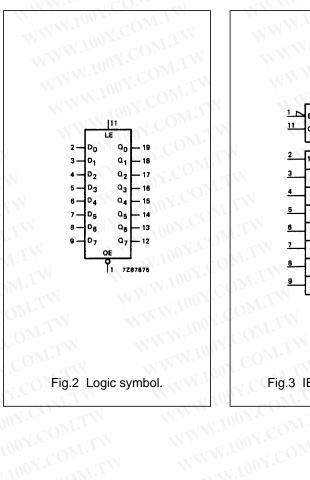

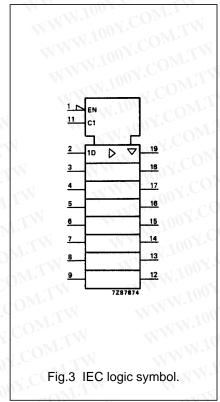

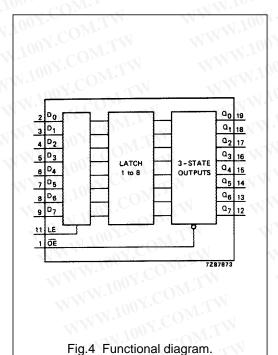

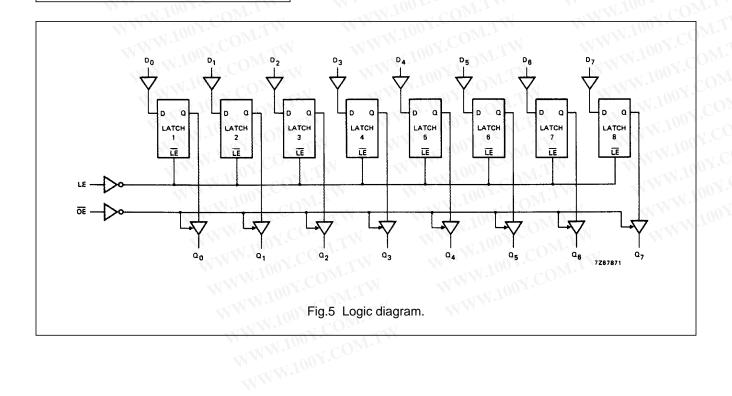

The 74HC/HCT573 are octal D-type transparent latches featuring separate D-type inputs for each latch and 3-state outputs for bus oriented applications.

A latch enable (LE) input and an output enable (OE) input are common to all latches.

The "573" consists of eight D-type transparent latches with 3-state true outputs. When LE is HIGH, data at

the  $D_n$  inputs enter the latches. In this condition the latches are transparent, i.e. a latch output will change state each time its corresponding D-input changes.

When LE is LOW the latches store the information that was present at the D-inputs a set-up time preceding the HIGH-to-LOW transition of LE. When  $\overline{OE}$  is LOW, the contents of the 8 latches are available at the outputs. When  $\overline{OE}$  is HIGH, the outputs go to the high impedance OFF-state. Operation of the  $\overline{OE}$  input does not affect the state of the latches.

The "573" is functionally identical to the "563" and "373", but the "563" has inverted outputs and the "373" has a different pin arrangement.

#### QUICK REFERENCE DATA

GND = 0 V;  $T_{amb} = 25 \, ^{\circ}\text{C}$ ;  $t_r = t_f = 6 \, \text{ns}$

| CVMDOL                              |   | DADAMETER                               | CONDITIONS                                  | T   | 100Y.C |         |  |

|-------------------------------------|---|-----------------------------------------|---------------------------------------------|-----|--------|---------|--|

| SYMBOL                              |   | PARAMETER                               | CONDITIONS                                  | НС  | нст    | UNIT    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | W | propagation delay                       | $C_L = 15 \text{ pF}; V_{CC} = 5 \text{ V}$ | 7   | MA     | 1 100Y. |  |

|                                     |   | D <sub>n</sub> to Q <sub>n</sub>        | MM. 100X.COM                                | 14  | 17     | ns      |  |

|                                     |   | LE to Q <sub>n</sub>                    | MAM. Inc. COM.                              | 15  | 15     | ns      |  |

| Cı                                  |   | input capacitance                       | COM COM                                     | 3.5 | 3.5    | pF      |  |

| C <sub>PD</sub>                     |   | power dissipation capacitance per latch | notes 1 and 2                               | 26  | 26     | pF 1.10 |  |

#### **Notes**

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_L \times V_{CC}^2 \times f_o)$$

where:

f<sub>i</sub> = input frequency in MHz; f<sub>o</sub> = output frequency in MHz

$$\sum (C_1 \times V_{CC}^2 \times f_0) = \text{sum of outputs}$$

C<sub>L</sub> = output load capacitance in pF; V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_1 = GND$  to  $V_{CC}$ ; for HCT the condition is  $V_1 = GND$  to  $V_{CC} - 1.5$  V

### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

Http://www.100y.com.tw

# Octal D-type transparent latch; 3-state

## 74HC/HCT573

### **PIN DESCRIPTION**

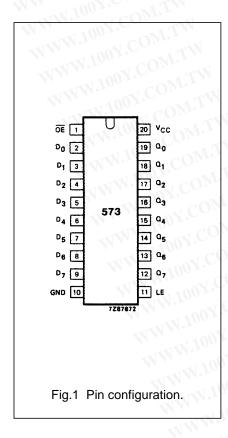

| PIN NO.                        | SYMBOL                           | NAME AND FUNCTION                        |

|--------------------------------|----------------------------------|------------------------------------------|

| 2, 3, 4, 5, 6, 7, 8, 9         | D <sub>0</sub> to D <sub>7</sub> | data inputs                              |

| 11 OV.COM                      | LE                               | latch enable input (active HIGH)         |

| IN.100 COM.                    | ŌĒ                               | 3-state output enable input (active LOW) |

| 10 V.100 COM.                  | GND                              | ground (0 V)                             |

| 19, 18, 17, 16, 15, 14, 13, 12 | Q <sub>0</sub> to Q <sub>7</sub> | 3-state latch outputs                    |

| 20                             | V <sub>CC</sub>                  | positive supply voltage                  |

Http://www.100y.com.tw

# Octal D-type transparent latch; 3-state

## 74HC/HCT573

### **FUNCTION TABLE**

| OPERATING                                   |    | NPUT | S              | INTERNAL    | OUTPUTS Q <sub>0</sub> to Q <sub>7</sub> L H |  |

|---------------------------------------------|----|------|----------------|-------------|----------------------------------------------|--|

| MODES                                       | ŌĒ | LE   | D <sub>N</sub> | LATCHES     |                                              |  |

| enable and read register (transparent mode) |    | H    | H<br>(1,100    | OX.CH COM.  |                                              |  |

| latch and read register                     | L  | L    | l<br>h         | 100 H ON    | TVH                                          |  |

| latch register and disable outputs          | H  | Ly   | l<br>h         | 1.100 H. CO | Z<br>Z                                       |  |

#### **Notes**

- 1. H = HIGH voltage level

- h = HIGH voltage level one set-up time prior to the HIGH-to-LOW LE transition

- L = LOW voltage level

- I = LOW voltage level one set-up time prior to the HIGH-to-LOW LE transition

- Z = high impedance OFF-state

Http://www.100y.com.tw

## Octal D-type transparent latch; 3-state

74HC/HCT573

### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: bus driver

I<sub>CC</sub> category: MSI

### **AC CHARACTERISTICS FOR 74HC**

| SYMBOL                              | PARAMETER                                            | T <sub>amb</sub> (°C) |                |                 |                  |                 |                 |                 |      | TEST CONDITIONS        |           |

|-------------------------------------|------------------------------------------------------|-----------------------|----------------|-----------------|------------------|-----------------|-----------------|-----------------|------|------------------------|-----------|

|                                     |                                                      |                       |                |                 |                  |                 |                 |                 |      | 01.                    | COWILM    |

|                                     |                                                      | +25                   |                |                 | <b>-40</b> t     | to +85          | -40 t           | -40 to +125     |      | V <sub>CC</sub><br>(V) | WAVEFORMS |

|                                     | V.100Y.COM.TW                                        | min.                  | typ.           | max.            | min.             | max.            | min.            | max.            | TWW. | 100                    | COMITY    |

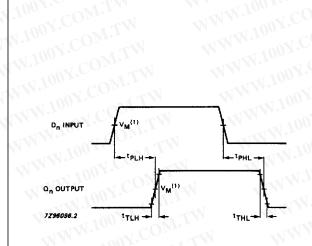

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay D <sub>n</sub> to Q <sub>n</sub>   |                       | 47<br>17<br>14 | 150<br>30<br>26 | 100X.            | 190<br>38<br>33 | TW              | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0      | Fig.6     |

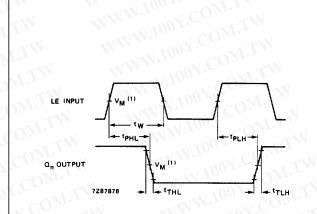

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>LE to Q <sub>n</sub>            |                       | 50<br>18<br>14 | 150<br>30<br>26 | 1.100<br>1.100   | 190<br>38<br>33 | M.T.            | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0      | Fig.7     |

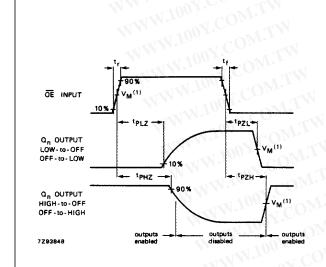

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time $\overline{OE}$ to $Q_n$  | LTW                   | 44<br>16<br>13 | 140<br>28<br>24 | MM· <sub>1</sub> | 175<br>35<br>30 | $co_{M_1}$      | 210<br>42<br>36 | ns   | 2.0<br>4.5<br>6.0      | Fig.8     |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time $\overline{OE}$ to $Q_n$ | OM.T                  | 55<br>20<br>16 | 150<br>30<br>26 | MAN              | 190<br>38<br>33 | Y.CO            | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0      | Fig.8     |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                               | COM                   | 14<br>5<br>4   | 60<br>12<br>10  | MA               | 75<br>15<br>13  | 00.X°C          | 90<br>18<br>15  | ns   | 2.0<br>4.5<br>6.0      | Fig.6     |

| t <sub>W</sub>                      | enable pulse width<br>HIGH                           | 80<br>16<br>14        | 14<br>5<br>4   | N               | 100<br>20<br>17  | MM              | 120<br>24<br>20 | CON             | ns   | 2.0<br>4.5<br>6.0      | Fig.7     |

| t <sub>su</sub>                     | set-up time<br>D <sub>n</sub> to LE                  | 50<br>10<br>9         | 11<br>4<br>3   | TW              | 65<br>13<br>11   | WW              | 75<br>15<br>13  | 0Y.C            | ns   | 2.0<br>4.5<br>6.0      | Fig.9     |

| t <sub>h</sub>                      | hold time<br>D <sub>n</sub> to LE                    | 5<br>5<br>5           | 3<br>1.        | M.TV<br>OM.T    | 5<br>5<br>5      | N.              | 5<br>5<br>5     | 700X            | ns M | 2.0<br>4.5<br>6.0      | Fig.9     |

Product specification

## Octal D-type transparent latch; 3-state

74HC/HCT573

### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: bus driver

I<sub>CC</sub> category: MSI

## Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| D <sub>n</sub> | 0.35                  |

| LE<br>OE       | 0.65                  |

| ŌĒ             | 1.25                  |

### **AC CHARACTERISTICS FOR 74HCT**

| SYMBOL                              | MMM.100X.COM                                       | T <sub>amb</sub> (°C) |      |             |            |      |             |       |      | TEST CONDITIONS        |              |  |

|-------------------------------------|----------------------------------------------------|-----------------------|------|-------------|------------|------|-------------|-------|------|------------------------|--------------|--|

|                                     |                                                    | 74HCT                 |      |             |            |      |             |       |      | MM                     | W.1007.CC    |  |

|                                     | PARAMETER                                          | +25                   |      |             | -40 to +85 |      | -40 to +125 |       | UNIT | V <sub>CC</sub><br>(V) | WAVEFORMS    |  |

|                                     | WWW.100Y.CC                                        | min.                  | typ. | max.        | min.       | max. | min.        | max.  |      | (1)                    | W 1. 100 Y.C |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay D <sub>n</sub> to Q <sub>n</sub> | COM                   | 20   | 35          | WW         | 44   | V.C         | 53    | ns   | 4.5                    | Fig.6        |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>LE to Q <sub>n</sub>          | CON                   | 18   | 35          | W          | 44   | 00Y.        | 53    | ns   | 4.5                    | Fig.7        |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time OE to Q <sub>n</sub>    | N.CO                  | 17   | 30          | 7          | 38   | N.100       | 45    | ns   | 4.5                    | Fig.8        |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time OE to Q <sub>n</sub>   | 700X                  | 18   | 30          |            | 38   | W.10        | 45    | ns   | 4.5                    | Fig.8        |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                             | 1.100                 | 5    | 12          | N          | 15   | WW          | 18    | ns   | 4.5                    | Fig.6        |  |

| t <sub>W</sub>                      | enable pulse width<br>HIGH                         | 16                    | 5    | $O_{M_{I}}$ | 20         |      | 24          | W.100 | ns   | 4.5                    | Fig.7        |  |

| t <sub>su</sub>                     | set-up time<br>D <sub>n</sub> to LE                | 13                    | 7    | .coM        | 16         |      | 20          |       | ns   | 4.5                    | Fig.9        |  |

| t <sub>h</sub>                      | hold time<br>D <sub>n</sub> to LE                  | 9                     | 4    | N.CO        | 11         |      | 14          |       | ns   | 4.5                    | Fig.9        |  |

Http://www. 100y. com. tw

# Octal D-type transparent latch; 3-state

Ñ

## 74HC/HCT573

### **AC WAVEFORMS**

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.6 Waveforms showing the data input  $(D_n)$  to output  $(Q_n)$  propagation delays and the output transition times.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.7 Waveforms showing the latch enable input (LE) pulse width, the latch enable input to output  $(Q_n)$  propagation delays and the output transition times.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.8 Waveforms showing the 3-state enable and disable times.

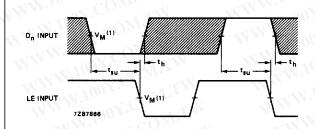

The shaded areas indicate when the input is permitted to change for predictable output performance.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.9 Waveforms showing the data set-up and hold times for D<sub>n</sub> input to LE input.

### **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".