# **GENERAL INFORMATION**

# **UAR/T: Universal Asynchronous Receiver/Transmitter**

勝 特 力 材 料 886-3-5753170 胜特力电子(上海 86-21-34970699 胜特力电子(深圳 86-755-83298787 Http://www.100y.com.tw

#### **FEATURES**

- DTL and TTL compatible—no interfacing circuits required drives one TTL load

- Fully Double Buffered—eliminates need for system synchronization, facilitates high-speed operation

- Full Duplex Operation—can handle multiple bauds (receiving-transmitting) simultaneously

- Start Bit Verification—decreases error rate with center sampling

- Receiver center sampling of serial input; 46% distortion immunity

- High Speed Operation

- Three-State Outputs—bus structure capability

- Low Power minimum power requirements

- Input Protected—eliminates handling problems

#### AY-5-1013A

- GIANT P-channel nitride process

- 0 to 40kbaud

- Pull up resistors to V<sub>CC</sub> on all inputs

#### AY-6-1013

- GIANT P-channel nitride process

- 0 to 22.5kbaud

- Extended Operating Temperature Range:

-40°C to +85°C (plastic package)

-55°C to +125°C (ceramic package)

- Pull-up resistors to V<sub>CC</sub> on all inputs

#### AY-3-1014A/1015D

- Single Supply Operation:

- +4.75V to +14V (AY-3-1014A)

- +4.75V to +5.25V (AY-3-1015D)

- CMOS compatible (AY-3-1014A)

- 11/2 stop bit mode

- External reset of all registers except control bits register

- GIANT II N-channel Ion Implant Process

- 0 to 30k baud

- Pull-up resistors to V<sub>cc</sub> on all inputs (AY-3-1015D)

#### DESCRIPTION

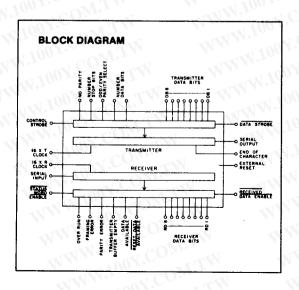

The Universal Asynchronous Receiver/Transmitter (UAR/T) is an LSI subsystem which accepts binary characters from either a terminal device or a computer and receives/transmits this character with appended control and error detecting bits. All characters contain a start bit, 5 to 8 data bits, one or two stop bits (1½ stop bit capability with the AY-3-1014A/1015D), and either odd/even parity or no parity. In order to make the UAR/T universal, the baud, bits per word, parity mode, and the number of stop bits are externally selectable. The device is constructed on a single monolithic chip. All inputs and outputs are directly compatible with MTOS/MTNS logic, and also with TTL/DTL/CMOS logic without the need for interfacing components. All strobed outputs are three-state logic.

# M.100X.COM PIN FUNCTIONS

100Y.COM.TW

| 勝 | 特   | 力  | 材    | 料      | 886-3-5753170   |

|---|-----|----|------|--------|-----------------|

| 胜 | 特力  | 电  | 子(上  | 海)     | 86-21-34970699  |

| 胜 | 特力  | 电  | 子(深  | 圳)     | 86-755-83298787 |

|   | Htt | n. | // 1 | X/ XX/ | 100v com tw     |

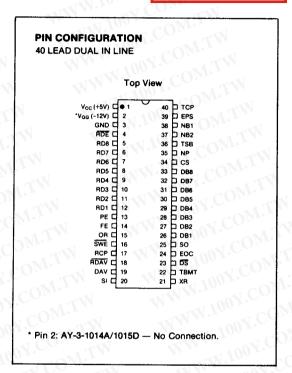

| Pin No.     | Name (Symbol)                                     | 100y. com. tw Function                                                                                                                                                                                                                                                                             |      |  |  |  |  |

|-------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 1           | Vcc Power Supply (Vcc)                            | +5V Supply                                                                                                                                                                                                                                                                                         |      |  |  |  |  |

| 2           | V <sub>GG</sub> Power Supply (V <sub>GG</sub> )   | -12V Supply (Not connected for AY-3-1014A/1015)                                                                                                                                                                                                                                                    |      |  |  |  |  |

| 3           | Ground (V <sub>GI</sub> )                         | Ground                                                                                                                                                                                                                                                                                             |      |  |  |  |  |

| 4           | Received Data Enable (RDE)                        | A logic "0" on the receiver enable line places the received data onto the output lines.                                                                                                                                                                                                            |      |  |  |  |  |

| 5-12        | Received Data Bits (RD8-RD1)                      | These are the 8 data output lines. Received characters are right justified: the LSB always appears on RD1. These lines have tristate outputs; i.e., they have the normal TTL output characteristic and the state outputs.                                                                          |      |  |  |  |  |

| **          | Parity Error (PE)                                 | tics when RDE is "0" and a high impedance state when RDE is "1". Thus, the data output lines can be bus structure oriented.  This line goes to a logic "1" if the received character parity does                                                                                                   |      |  |  |  |  |

| 13<br>14    | Framing Error (FE)                                | not agree with the selected parity. Tri-state.  This line goes to a logic "1" if the received character has no valid                                                                                                                                                                               |      |  |  |  |  |

| 15          | Over-Run (OR)                                     | stop bit. Tri-state.  This line goes to a logic "1" if the previously received character is                                                                                                                                                                                                        |      |  |  |  |  |

| N           | MM 1001.00                                        | not read (DAV line not reset) before the present character is transferred to the receiver holding register. Tri-state.                                                                                                                                                                             |      |  |  |  |  |

| 16          | Status Word Enable (SWE)                          | A logic "0" on this line places the status word bits (PE, FE, OR, DAV, TBMT) onto the output lines. Tri-state.  This line will contain a clock whose frequency is 16 times (16X)                                                                                                                   |      |  |  |  |  |

| 17<br>18    | Receiver Clock (RCP)  Reset Data Available (RDAV) | the desired receiver baud.  A logic "0" will reset the DAV line. The DAV F/F is only thing that                                                                                                                                                                                                    |      |  |  |  |  |

| 19          | Data Available (DAV)                              | is reset. Must betied to logic "1" when not in use on the AY-3-1014A.  This line goes to a logic "1" when an entire character has been received and transferred to the receiver holding register. Tri-                                                                                             |      |  |  |  |  |

| 20          | Serial Input (SI)                                 | state. Fig. 12,34. This line accepts the serial bit input stream. A Marking (logic "1") to spacing (logic "0") transition is required for initiation of data reception. Fig. 11,12,33,34.                                                                                                          |      |  |  |  |  |

| 21          | External Reset (XR)                               | Resets all registers except the control bits register (the received data register is not reset in the AY-5-1013A and AY-6-1013). Sets SO, EOC, and TBMT to a logic "1". Resets DAV, and error flags to "0". Clears input data buffer. Must be                                                      |      |  |  |  |  |

| 22          | Transmitter Buffer Empty (TBMT)                   | tied to logic "0" when not in use.  The transmitter buffer empty flag goes to a logic "1" when the data bits holding register may be loaded with another character.                                                                                                                                |      |  |  |  |  |

| 23          | Data Strobe (DS)                                  | Tri-state. See Fig. 18,20,40,42.  A strobe on this line will enter the data bits into the data bits holding register. Initial data transmission is initiated by the rising edge of DS. Data must be stable during entire strobe.                                                                   |      |  |  |  |  |

| 24          | End of Character (EOC)                            | This line goes to a logic "1" each time a full character is transmitted. It remains at this level until the start of transmission of the next character. See Fig. 17, 19, 39, 41.                                                                                                                  |      |  |  |  |  |

| 25          | Serial Output (SO)                                | This line will serially, by bit, provide the entire transmitted char-<br>acter. It will remain at a logic "1" when no data is being transmit-<br>ted. See Fig. 16.                                                                                                                                 |      |  |  |  |  |

| 26-33<br>34 | Data Bit Inputs (DB1-DB8) Control Strobe (CS)     | There are up to 8 data bit input lines available.  A logic "1" on this lead will enter the control bits (EPS, NB1, NB2, TSB, NP) into the control bits holding register. This line can be strobed or hard wired to a logic "1" level.                                                              |      |  |  |  |  |

| 35          | No Parity (NP)                                    | A logic "1" on this lead will eliminate the parity bit from the transmitted and received character (no PE indication). The stop bit(s) will immediately follow the last data bit. If not used, this lead must be tied to a logic "0".                                                              |      |  |  |  |  |

| 36          | Number of Stop Bits (TSB)                         | This lead will select the number of stop bits, 1 or 2, to be appended immediately after the parity bit. A logic "0" will insert 1 stop bit and a logic "1" will insert 2 stop bits. For the AY-3-1014A/1015, the combined selection of 2 stop bits and 5 bits/character will produce 1½ stop bits. |      |  |  |  |  |

| 37-38       | Number of Bits/Character (NB2, NB1)               | These two leads will be internally decoded to select either 5, 6, 7 or 8 data bits/character.  NB2 NB1 Bits/Character  0 0 5                                                                                                                                                                       |      |  |  |  |  |

|             | WW.100X.COM.TW                                    | 0 1 6<br>1 0 7<br>1 1 8                                                                                                                                                                                                                                                                            |      |  |  |  |  |

| 39          | Odd/Even Parity Select (EPS)                      | The logic level on this pin selects the type of parity which will be<br>appended immediately after the data bits. It also determines the<br>parity that will be checked by the receiver. A logic "0" will insert<br>odd parity and a logic "1" will insert even parity                             |      |  |  |  |  |

| 40          | Transmitter Clock (TCP)                           | This line will contain a clock whose frequency is 16 times (16X) the desired transmitter baud.                                                                                                                                                                                                     |      |  |  |  |  |

|             |                                                   |                                                                                                                                                                                                                                                                                                    | 6-81 |  |  |  |  |

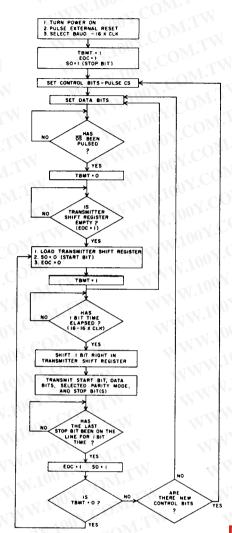

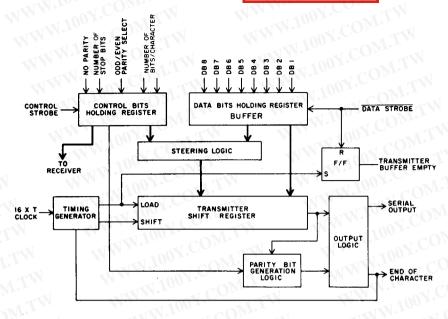

#### TRANSMITTER OPERATION

#### Flg.1

#### initializing

Power is applied, external reset is enabled and clock pulse is applied having a frequency of 16 times the desired baud. The above conditions will set TBMT, EOC, and SO to logic "1" (line is marking).

After initializing is completed, user may set control bits and data bits with control bits selection normally occurring before data bits selection. However, one may set both DS and CS simultaneously if minimum pulse width specifications are followed. Once Data Strobe (DS) is pulsed the TBMT signal will change from a logic "1" to a logic "0" indicating that the data bits holding register is filled with a previous character and is unable to receive new data bits, and transmitter shift register is transmitting previously loaded data. TBMT will return to a logic "1". When transmitter shift register is empty, data bits in the holding register are immediately loaded into the transmitter shift register for transmission. The shifting of information from the holding register to the transmitter shift register will be followed by SO and EOC going to a logic "0", and TBMT will also go to a logic "1" indicating that the shifting operation is completed and that the data bits holding register is ready to accept new data. It should be remembered that one full character time is now available for loading of the next character without loss in transmission speed due to double buffering (separate data bits holding register and transmitter shift register).

Data transmission is initiated with transmission of a start bit, data bits, parity bit (if desired) and stop bit(s). When the last stop bit has been on line for one bit time, EOC will go to a logic "1" indicating that new character is ready for transmission. This new character will be transmitted only if TBMT is a logic "0" as was previously discussed.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

**LELECOM**

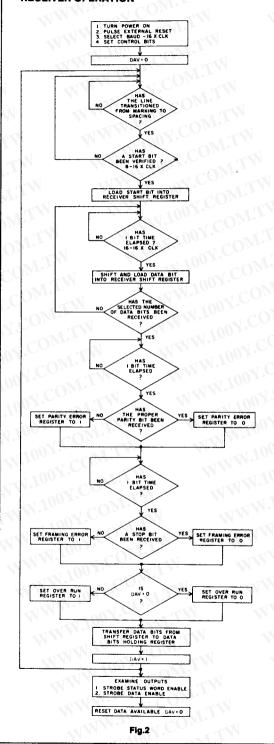

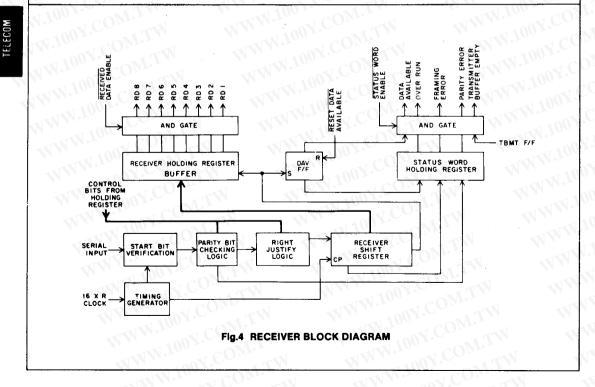

#### RECEIVER OPERATION

#### Initializing

Power is applied, external reset is enabled, and clock pulse is applied having a frequency of 16 times the desired baud. The previous conditions will set data available (DAV) to a logic "1".

After initializing is completed, user should note that one set of control bits will be used for both receiver and transmitter making individual control bit setting unnecessary. Data reception starts when serial input signal changes from Marking (logic "1") to spacing (logic "0") which initiates start bit. The start bit is valid if, after transition from logic "1" to logic "0", the SI line continues to be at logic "0", when center sampled, 8 clock pulses later. If, however, line is at a logic "1" when center sampling occurs, the start bit verification process will be reset. If the Serial Input line transitions from a logic "1" to a logic "0" (marking to spacing) when the 16x clock is in a logic "1" state, the bit time, for center sampling will begin when the clock line transitions from a logic "1" to a logic "0" state. After verification of a genuine start bit, data bit reception, parity bit reception and stop bit(s), reception proceeds in an orderly manner.

While receiving parity and stop bit(s) the receiver will compare transmitted parity and stop bit(s) with control data bits (parity and number of stop bits) previously set and indicate an error by changing the parity error flip flop and/or the framing error flip flop to a logic "1". It should be noted that if the No Parity Mode is selected the PE (parity error) will be unconditionally set to a logic "0".

Once a full character is received, internal logic looks at the data available (DAV) signal to determine if data has been the read out. If the DAV signal is at a logic "1" the receiver will assume data has not been read out and the over run flip flop of the status word holding register will be set to a logic "1". If the DAV signal is at a logic "0" the receiver will assume that data has been read out. After DAV goes to a logic "1", the receiver shift register is now ready to accept the next character and has one full character time to remove the received character.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw TELECOM

Fig.3 TRANSMITTER BLOCK DIAGRAM

特力材料886-3-5753170

胜特力电子(上海) 86-21-34970699

## AY-5-1013A AY-6-1013

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

V<sub>GG</sub> (with respect to V<sub>CC</sub>). -20 to +0.3V Clock and logic input voltages (with respect to Vcc) -20 to +0.3V 65°C to +150°C Storage Temperature . . Lead Temperature (soldering, 10 seconds) +330°C

\*Exceeding these ratings could cause permanent damage. Functional operation of these devices at these conditions is not implied -operating ranges are specified below.

#### Standard Conditions (unless otherwise noted)

$V_{GG} = -12V \pm 5\%$

$V_{cc} = +5V \pm 5\%$

Temperature  $(T_A) = 0$ °C to +70°C (AY-5-1013A)

-40 C to +85°C (AY-6-1013 Plastic Package)

胜特力电子(深圳) 86-755-83298787 -55C to +125°C (AY-6-1013 Ceramic Package) Http://www. 100y. com. tw

| Characteristic           | Min                  | Typ"                      | Max                   | Units    | Conditions                                   |

|--------------------------|----------------------|---------------------------|-----------------------|----------|----------------------------------------------|

| DC CHARACTERISTICS       | -1100X               | 140                       | $\tilde{L}_{M}$       |          | 2 100 r. COM: 1                              |

| Input Logic Levels       | NIN.                 |                           | -431                  | - 1      |                                              |

| Logic 0                  | 0                    | _                         | 0.8                   | Voits    | $(I_{1L} = -1.6 \text{mA max.})$             |

| Logic 1                  | V <sub>CC</sub> -1.5 | — — <u>—</u>              | V <sub>CC</sub> +0.3  | Volts    | Unit has internal pullup resistors           |

| input Capacitance        |                      |                           | TW                    |          |                                              |

| All Inputs               | `                    | -0                        | 20                    | pF [     | 0 volts bias, f= 1MHz                        |

| Leakage Currents         |                      |                           | TVV.                  |          |                                              |

| Three State Outputs      | VT 1                 | N                         | 1.0                   | μΑ       | 0 volts                                      |

| Data Output Levels       | TANNO                |                           | 7                     | 1        |                                              |

| Logic 0                  | W ''                 | 007.                      | +0.4                  | Volts    | I <sub>OL</sub> = 1.6mA (sink)               |

| Logic 1                  | Vcc-1.0              | (                         | $OM_{r}$              | Volts    | I <sub>OH</sub> = .3mA (source) at 5.0 Volts |

| Output Capacitance       |                      | 10                        | 15                    | pF       |                                              |

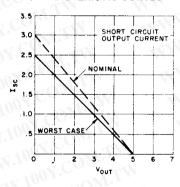

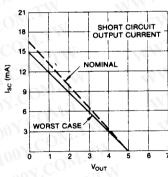

| Short Ckt. Current       |                      | 700                       |                       | Ρ'       | Son File 00                                  |

| -1 ( V3)                 | 1 - 1 TN 11          | -01                       | U-                    |          | See Fig. 23                                  |

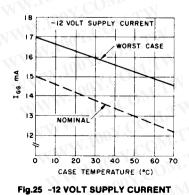

| Power Supply Current     | 11                   | $^{\circ}$ 100 $^{\circ}$ | Mar                   | 7 1      | AV 5 40404 \ 0-5 5 \ 05                      |

| IGG )                    | TAN Y                | 14                        | 16                    | mA .     | AY-5-1013A - See Fig.25                      |

| 25°C,all inputs +5V      | 1 1                  | 17                        | 19                    | mA       | AY-6-1013 - See Fig.25                       |

| lcc )                    |                      | 21                        | 20 23                 | mA<br>mA | AY-5-1013A - See Fig.26<br>AY-6-1013         |

|                          |                      | 1 21                      | 23                    | MA       | A1-6-1013                                    |

| AC CHARACTERISTICS       |                      |                           | -1 CO                 | Mr. z    | T <sub>A</sub> = 25°C, output load           |

|                          |                      |                           |                       |          | capacitance 50pF max.                        |

| Clock Frequency          | DC                   | - 1 <del>4</del> 1. L     | 640                   | kHz      | AY-5-1013A                                   |

| CO.                      | DC a                 | M 7.                      | 360                   | kHz      | AY-6-1013                                    |

| Baud                     | 0                    |                           | 40                    | kbaud    | AY-5-1013A                                   |

| $M_{220} = (O_{M_2})$    | «1 ŏ                 | - TAN                     | 22.5                  | kbaud    | AY-6-1013                                    |

| Pulse Width              |                      |                           | 4007.                 | ~ ( )    | 100                                          |

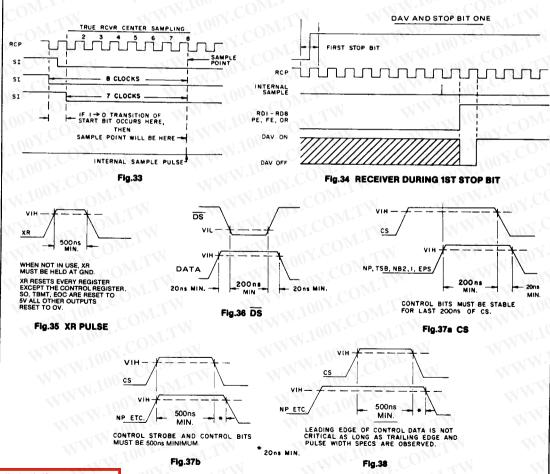

| Clock Pulse              | 750                  |                           | .10                   | ns       | AY-5-1013A - See Fig.9                       |

| 1                        | 1.5                  | 41/3/                     | 4 = 0.0               | μS       | AY-6-1013-See Fig.9                          |

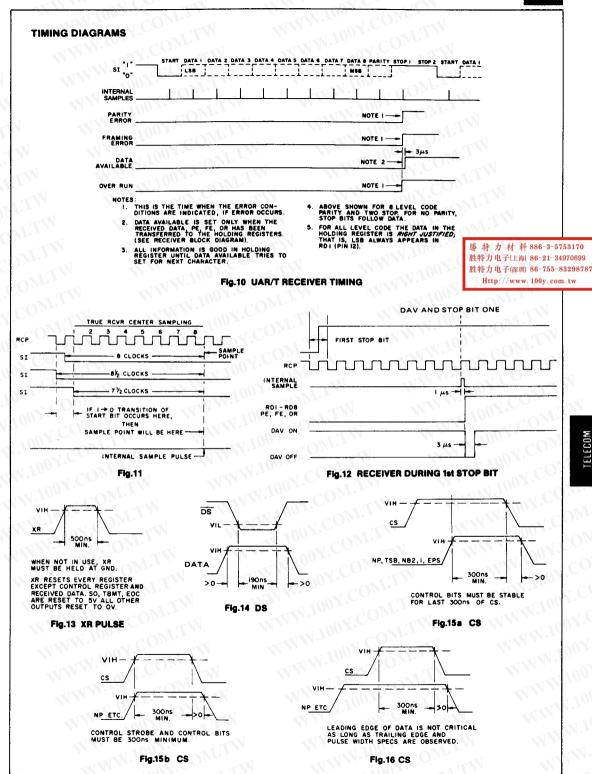

| Control Strobe           | 300                  | - VIII - 21               | V 700                 | ns       | AY-5-1013A-See Fig. 15, 16                   |

| MM.                      | 600                  | 4                         | _ ~                   | ns       | AY-6-1013                                    |

| Data Strobe              | 190                  |                           | -x1400                | ns       | AY-5-1013A-See Fig. 14                       |

|                          | 250                  | - 1                       |                       | ns       | AY-6-1013                                    |

| External Reset           | 500                  | 22                        | -10                   | ns       | AY-5-1013A - See Fig. 13                     |

|                          | 1.0                  |                           | V1/7"                 | μs       | AY-6-1016                                    |

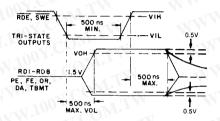

| Status Word Enable       | 500                  | -11                       | N '                   | ns       | AY-5-1013A - See Fig. 21                     |

|                          | 600                  | _ "                       | -1 <del>-1</del> 1.31 | ns       | AY-6-1013 - See Fig. 21                      |

| Reset Data Available     | 250                  |                           | 1/1/27                | ns       | AY-5-1013A - See Fig. 22                     |

| W 1100 X.                | 350                  | _                         | "                     | ns       | AY-6-1013 - See Fig. 22                      |

| Received Data Enable     | 500                  |                           | Land William          | ns       | AY-5-1013A - See Fig. 21                     |

|                          | 600                  | _                         | M                     | ns       | AY-6-1013 - See Fig. 21                      |

| Set Up & Hold Time       | OM.                  |                           | -TAN W                | -1       |                                              |

| nput Data Bits           | 0                    | _                         |                       | ns       | See Fig.14                                   |

| nput Control Bits        | 0                    |                           |                       | ns       | See Fig. 15, 16                              |

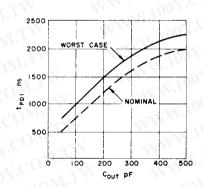

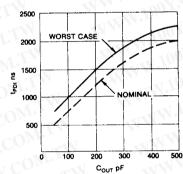

| Output Propagation Delay | Co.                  |                           | TIN I                 | T CON    |                                              |

| TPD0                     | - <del></del> ( ) ]  | _                         | 500                   | ns       | AY-5-1013A - See Fig. 21 & 24                |

|                          | 4 COZz.              | -x1-                      | 650                   | ns       | AY-6-1013 - See Fig. 21 & 24                 |

| TPD1                     | Y - 41               | 11/1                      | 500                   | ns       | AY-5-1013A - See Fig. 21 & 24                |

|                          | I dollar             | _                         | 650                   | ns       | AY-6-1013 - See Fig. 21 & 24                 |

<sup>&</sup>quot;Typical values are at +25°C and nominal voltages.

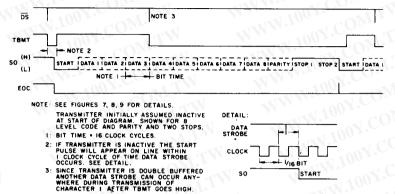

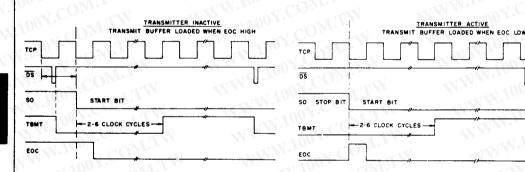

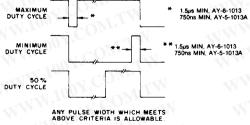

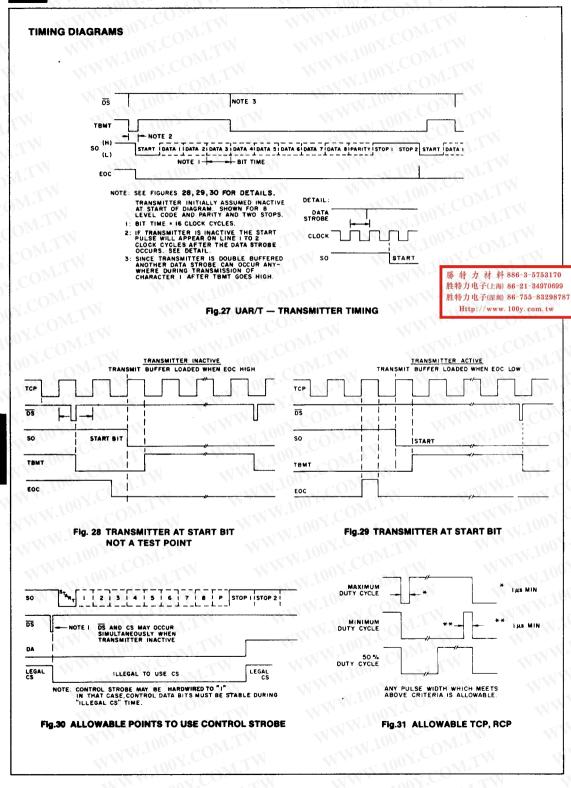

# TIMING DIAGRAMS

Fig.5 UAR/T TRANSMITTER TIMING

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Fig.6 TRANSMITTER AT START BIT

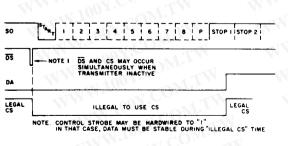

Fig.8 ALLOWABLE POINTS TO USE CONTROL STROBE

#### Fig.7 TRANSMITTER AT START BIT

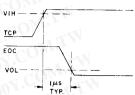

Fig.9 ALLOWABLE TCP, RCP

特力材料886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100v.com.tw

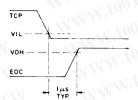

VIH -VIL TBMT VOL -

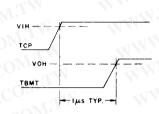

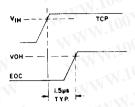

Fig.17 EOC TURN-ON

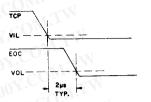

Fig.19 EOC TURN-OFF

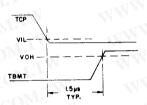

Fig.18 TBMT TURN-OFF

Fig.20 TBMT TURN-ON

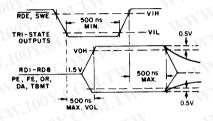

Fig.21 RDE, SWE

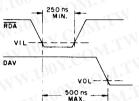

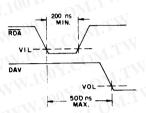

Fig.22 RDAV

#### TYPICAL CHARACTERISTIC CURVES

Fig.23 SHORT CIRCUIT OUTPUT CURRENT

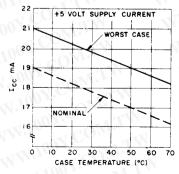

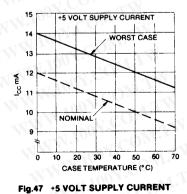

Fig.26 +5 VOLT SUPPLY CURRENT

TELECOM

AY-3-1015D

# GENERAL INSERUMENI

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

Vcc (with respect to GND) . .-0.3 to +16V -65°C to +150°C Storage Temperature . . . Operating Temperature. 0°C to + 70°C Lead Temperature (Soldering, 10 sec) +330°C

\*Exceeding these ratings could cause permanent damage. Functional operation of these devices at these conditions is not implied -operating ranges are specified below.

#### Standard Conditions (unless otherwise noted)

Vcc = +4.75 to +14V (AY-3-1014A) ---Vcc = +4.75V to +5.25V (AY-3-1015D) Operating Temperature (T<sub>A</sub>) = 0°C to +70°C

| Characteristic                                         | Min             | Тур"             | Max                  | Units          | Conditions                                                                                  |

|--------------------------------------------------------|-----------------|------------------|----------------------|----------------|---------------------------------------------------------------------------------------------|

| DC CHARACTERISTICS                                     | anv.C           | Dr. W            | N.                   | WW             | TV STORY                                                                                    |

| Input Logic Levels (AY-3-1014A)                        |                 | LOW!             |                      |                | M. Jan. COM.                                                                                |

| Logic 0                                                | 0               |                  | 0.8                  | Volts          |                                                                                             |

| Logic 1: at V <sub>CC</sub> = +4.75V                   | 2.0             | - <del></del> (  | V <sub>CC</sub> +0.3 | Volts          | 100 M.1                                                                                     |

| at V <sub>CC</sub> = +14V                              | 3.0             | ( ( <del>)</del> | V <sub>CC</sub> +0.3 | Volts          | M. COL                                                                                      |

| Input Logic Levels (AY-3-1015)                         |                 |                  |                      | . '\\          | 1007.                                                                                       |

| Logic 0                                                | 0               | AAN!             | 0.8                  | Volts          | MIN. IN COM.                                                                                |

| Logic 1                                                | 2.4             |                  | V <sub>cc</sub> +0.3 | Volts          | AY-3-1015 has internal                                                                      |

| Input Capacitance                                      |                 | 1                | 1/2 2.               |                | pull-up resistors to V <sub>CC</sub>                                                        |

| All inputs                                             | 1 1 1 <u>-</u>  | A CU             | 20                   | pF             | 0 volts bias, f = 1MHz                                                                      |

| Output Impedance                                       |                 | 07.              |                      |                | 100                                                                                         |

| Tri-State Outputs                                      | 1.0             |                  |                      | MΩ             | TIMM.                                                                                       |

| Data Output Levels                                     | 1.0             |                  |                      | 1414.1         | M. 1001.                                                                                    |

| Logic 0                                                |                 | 00               | 0.4                  | - 1/- (A-      | 7 - 10 4 (111)                                                                              |

| Logic 1: AY-3-1014A/1015D                              | 2.4             | 1.700            | +0.4                 | Volts<br>Volts | I <sub>OL</sub> = 1.6mA (sink)<br>I <sub>OH</sub> = -40μA (source)—at V <sub>CC</sub> = +5V |

| AY-3-1014A only                                        | 3.5             | 100-             |                      | Volts          | I <sub>OH</sub> = -50μA (source)—at V <sub>CC</sub> = +14                                   |

| Output Capacitance                                     | 3.3             | 10               | 15                   | pF             | TOH = -50/JA (SOURCE)—at VCC = +14                                                          |

|                                                        | // <del>-</del> | 100 7.           | 19                   | pr             | 100 -00                                                                                     |

| Short Ckt. Current                                     | - <del></del>   | N                | (CO-17)              |                | See Fig.45.                                                                                 |

| Power Supply Current                                   |                 | -11003           |                      |                | 1001.                                                                                       |

| Icc at Vcc = +5V (AY-3-1014A)                          | × X             | 10               | 15                   | mA             | See Fig.47.                                                                                 |

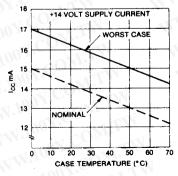

| I <sub>CC</sub> at V <sub>CC</sub> = +14V (AY-3-1014A) | <u> </u>        | 14               | 20                   | mA             | 47 41111 2                                                                                  |

| lcc at Vcc = +5V (AY-3-1015D)                          |                 | 10               |                      |                | See Fig.48.                                                                                 |

| 166 at V66 - +3V (A1-3-1019D)                          |                 | 1110             | 15                   | mA             | 1007.0                                                                                      |

| AC CHARACTERISTICS                                     | ,               | WW.F             | 1 CO                 | Mr.            | WWW. OV.C                                                                                   |

| W LOOK TW                                              |                 | -7.1             | 001.                 |                | T <sub>A</sub> = 25°C, Output load                                                          |

| William COMP.                                          |                 |                  |                      |                | capacitance 50 pF max.                                                                      |

| Clock Frequency                                        | DC ¶            | N                | 480/400              | kHz            | at V <sub>CC</sub> = +4.75V/+14V                                                            |

| Baud                                                   | 0               | -XX              | 30/25                | kbaud          | at V <sub>CC</sub> = +4.75V/+14V                                                            |

| Pulse Width                                            |                 | - 1              | - VI                 |                |                                                                                             |

| Clock Pulse                                            | 1.0             |                  | 1100 2               | μS             | See Fig.31                                                                                  |

| Control Strobe                                         | 500             |                  | N                    | ns             | See Fig.37                                                                                  |

| Data Strobe                                            | 200             | 1 T.             | 1 <del>0</del> 07    | ns             | See Fig.36                                                                                  |

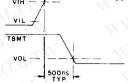

| External Reset                                         | 500             | _                | W.F.                 | ns             | See Fig.35                                                                                  |

| Status Word Enable                                     | 500             |                  | - 00°                | ns             | See Fig.43                                                                                  |

| Reset Data Available                                   | 200             | -                |                      | ns             | See Fig.44                                                                                  |

| Received Data Enable                                   | 500             | -                |                      | ns             | See Fig.43                                                                                  |

| Set Up & Hold Time                                     | 1 44            |                  | -31 1 W              |                |                                                                                             |

| Input Data Bits                                        | 20              | <                | 11 17.               | ns             | See Fig.36                                                                                  |

| Input Control Bits                                     | 20              | _ \              |                      | ns             | See Fig.37                                                                                  |

| Output Propagation Delay                               | Lo =            |                  | - W. W. P.           |                | J. W. T.                                                |

| TPD0                                                   | - (PA)          |                  | 500                  | ns             | See Fig.43 & 46                                                                             |

| TPD1                                                   | 1. 7            | _                | 500                  | ns             | See Fig.43 & 46                                                                             |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787

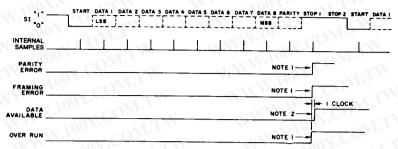

#### TIMING DIAGRAMS

#### NOTES:

- I. THIS IS THE TIME WHEN THE ERROR CON-DITIONS ARE INDICATED, IF ERROR OCCURS.

- 2. DATA AVAILABLE IS SET ONLY WHEN THE RECEIVED DATA, PE, FE, OR HAS BEEN TRANSFERRED TO THE HOLDING REGISTERS. (SEE RECEIVER BLOCK DIAGRAM).

- 3. ALL INFORMATION IS GOOD IN HOLDING REGISTER UNTIL DATA AVAILABLE TRIES TO SET FOR NEXT CHARACTER.

- ABOVE SHOWN FOR B LEVEL CODE PARITY AND TWO STOP, FOR NO PARITY, STOP BITS FOLLOW DATA.

- 5. FOR ALL LEVEL CODE THE DATA IN THE HOLDING REGISTER IS RIGHT JUSTIFIED; THAT IS, LSB ALWAYS APPEARS IN ROI (PIN 12).

#### Fig.32 UAR/T — RECEIVER TIMING

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### **TIMING DIAGRAMS**

VIH OS

VIL

TBMT

VOL

IMP

TYP

Fig.39 EOC TURN-ON

Fig.40 TBMT TURN-OFF

Fig.41 EOC TURN-OFF

Fig.42 TBMT TURN-ON

Fig.43 RDE, SWE

Fig.44 RDAV

### TYPICAL CHARACTERISTIC CURVES

Fig.45 SHORT CIRCUIT OUTPUT CURRENT (only 1 output may be shorted at a time)

Fig.46 RD1-RD8, PE, FE, OR, TBMT, DAV

Fig.48 +14 VOLT SUPPLY CURRENT (AY-3-1014A only)

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-34970699

胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw