勝特力電材超市-龍山店 886-3-5773766 勝特力電材超市-光復店 886-3-5729570 胜特力电子(上海) 86-21-34970699 胜特力电子(深圳) 86-755-83298787 http://www.100y.com.tw

## Preliminary PT5619 90V Three-Phase Gate Driver

#### DESCRIPTION

The PT5619 is a high-speed 3-phase gate driver for power MOSFET and IGBT devices with three independent high and low side referenced output channels. Built-in dead time protection and shoot-through protection prevent damage to the half-bridge. The UVLO circuits prevent malfunction when VCC and VBS are lower than the specified threshold voltage. A novel high-voltage BCD process and common-mode noise canceling technique provide stable operation of high-side drivers under high dV/dt noise conditions while achieving excellent negative transient voltage tolerance. An enable pin (ENB) is included so that standby mode may be used to set the chip into a low quiescent current state to realize long battery lifetime.

#### APPLICATION

- E-BIKE/electric power tool 3-phase motor driver

- · Battery-powered mini/micro motor control

- · General purpose inverter

#### **FEATURE**

- · Integrated 90V half-bridge high side driver

- Ability to drive up to 3-phase half-bridge gates

- Built-in dead time protection

- Shoot-through protection

- Under voltage lockout for VCC and VBS

- Low operation voltage 0-5.5V for VCC and VBS

- 3.3V and 5V input logic compatible

- Enable pin (ENB) for low standby current

- IO+/IO-: +1.2A/-2.0A at VCC=15V, VBS=15V

- Built-in dead time: 0.5µs (typ.)

- Common-mode dV/dt noise cancellation circuit

- Tolerant of negative transient voltage

- · Low dl/dt gate drive for better noise immunity

- -40°C to 125°C operating range

- Small footprint package: TSSOP20L/24L, QFN24

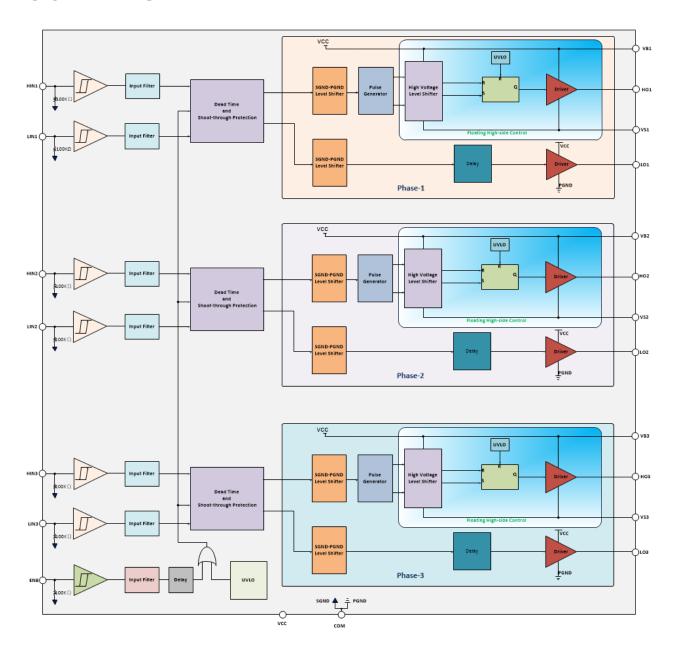

## **BLOCK DIAGRAM**

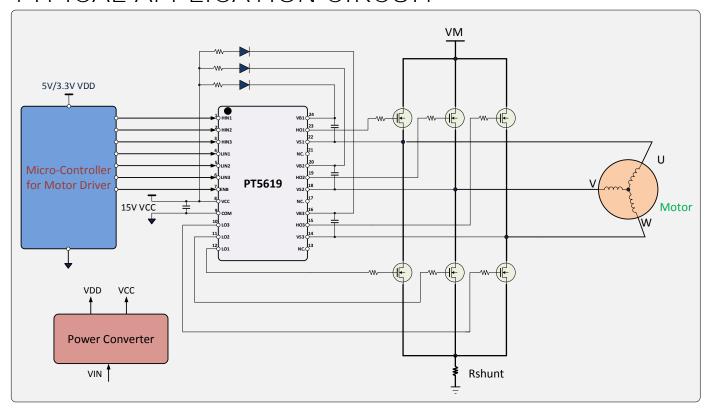

# TYPICAL APPLICATION CIRCUIT

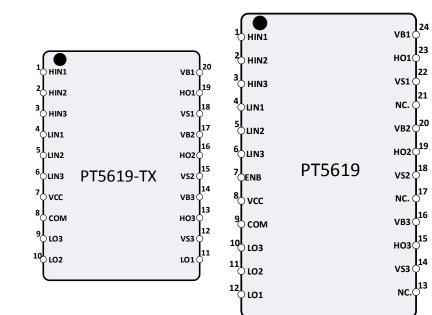

## ORDER INFORMATION

| Valid Part Number | Package Type   | Top Code  |

|-------------------|----------------|-----------|

| PT5619-TX         | 20 Pins, TSSOP | PT5619-TX |

| PT5619            | 24 Pins, TSSOP | PT5619    |

| PT5619            | 24 Pins, QFN   | PT5619    |

### PIN CONFIGURATION

20-PIN TSSOP

24-PIN TSSOP

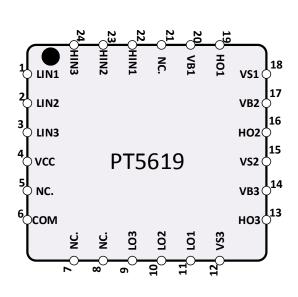

**QFN**

# PIN DESCRIPTION

| Din Nama | Description                                             | Pin No.      |              |     |

|----------|---------------------------------------------------------|--------------|--------------|-----|

| Pin Name | Description                                             | 20-Pin TSSOP | 24-Pin TSSOP | QFN |

| HIN1     | Logic input for phase-1 high-side gate driver           | 1            | 1            | 22  |

| HIN2     | Logic input for phase-2 high-side gate driver           | 2            | 2            | 23  |

| HIN3     | Logic input for phase-3 high-side gate driver           | 3            | 3            | 24  |

| LIN1     | Logic input for phase-1 low-side gate driver            | 4            | 4            | 1   |

| LIN2     | Logic input for phase-2 low-side gate driver            | 5            | 5            | 2   |

| LIN3     | Logic input for phase-3 low-side gate driver            | 6            | 6            | 3   |

| ENB      | Logic input for standby mode control                    | -            | 7            | -   |

| VCC      | Logic and low-side gate drivers power supply voltage    | 7            | 8            | 4   |

| NC       | Not connected                                           | -            | •            | 5   |

| COM      | Logic ground and low-side gate drivers ground           | 8            | 9            | 6   |

| NC       | Not connected                                           | -            | •            | 7   |

| NC       | Not connected                                           | -            | -            | 8   |

| LO3      | Phase-3 low-side gate driver output                     | 9            | 10           | 9   |

| LO2      | Phase-2 low-side gate driver output                     | 10           | 11           | 10  |

| LO1      | Phase-1 low-side gate driver output                     | 11           | 12           | 11  |

| NC.      | Not connected                                           | -            | 13           | -   |

| VS3      | Phase-3 high-side driver floating supply offset voltage | 12           | 14           | 12  |

| HO3      | Phase-3 high-side driver output                         | 13           | 15           | 13  |

| VB3      | Phase-3 high-side driver floating supply                | 14           | 16           | 14  |

| NC.      | Not connected                                           | -            | 17           | -   |

| VS2      | Phase-2 high-side driver floating supply offset voltage | 15           | 18           | 15  |

| HO2      | Phase-2 high-side driver output                         | 16           | 19           | 16  |

| VB2      | Phase-2 high-side driver floating supply                | 17           | 20           | 17  |

| NC.      | Not connected                                           | -            | 21           | -   |

| VS1      | Phase-1 high-side driver floating supply offset voltage | 18           | 22           | 18  |

| HO1      | Phase-1 high-side driver output                         | 19           | 23           | 19  |

| VB1      | Phase-1 high-side driver floating supply                | 20           | 24           | 20  |

| NC       | Not connected                                           | -            | -            | 21  |

|          |                                                         |              |              |     |

#### FUNCTION DESCRIPTION

#### LOW SIDE POWER SUPPLY: VCC

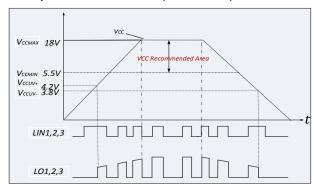

VCC is the low side supply and it provides power to both input logic and low side output power stage. The built-in undervoltage lockout circuit enables the device to operate at sufficient power when a typical VCC supply voltage higher than  $V_{\text{CCUV+}}$  =4.2V is present, shown as Figure. 1. The PT5619 shuts down all the gate driver outputs, when the VCC supply voltage is below  $V_{\text{CCUV-}}$ =3.8 V, shown as Figure. 1. This prevents the external power devices against extremely low gate voltage levels during on-state which may result in excessive power dissipation.

Figure. 1 VCC supply UVLO operating area

## HIGH SIDE POWER SUPPLY: VBS (VB1-VS1, VB2-VS2, VB3-VS3)

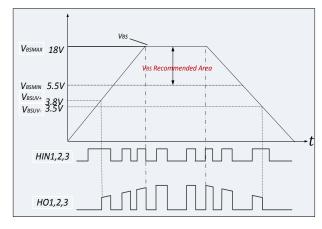

VBS is the high side supply voltage. The total high side circuitry may float with respect to COM following the external high side power device emitter/source voltage. Due to the internal low power consumption, the entire high side circuitry may be supplied by bootstrap topology connected to VCC, and it may be powered with small bootstrap capacitors. The device operating area as a function of the supply voltage is given in Figure. 2.

Figure. 2 VBS supply UVLO operating area

# LOW SIDE AND HIGH CONTROL INPUT LOGIC: HIN&LIN (HIN1, 2, 3/LIN1, 2, 3)

The Schmitt trigger threshold of each input is designed low enough to guarantee LSTTL and CMOS compatibility down to 3.3V controller outputs. Input Schmitt trigger and advanced noise filtering provide noise rejection of short input pulses. An internal pull-down resistor of about  $100 \text{k}\Omega$  (positive logic) pre-biases each input during VCC supply start-up state. The minimum recommended input pulse-width is 300ns for proper operation of the driver.

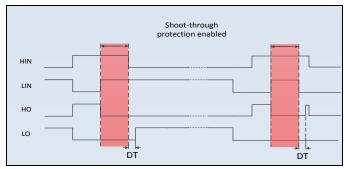

#### SHOOT-THROUGH PREVENTION

The PT5619 is equipped with shoot-through protection circuitry (also known as cross conduction prevention circuitry). Figure. 3 shows how this protection circuitry prevents both the high- and low-side switches from conducting at the same time. When the inputs controlling both high-side and low-side drivers are both logic HIGH, then both driver outputs are pulled down to logic LOW to shut down two power devices in the same bridge.

Figure. 3 Shoot-through prevention

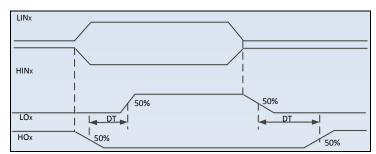

#### DEAD TIME PROTECTION

The PT5619 features integrated fixed dead time protection circuitry. The dead time feature inserts a time period (a minimum dead time) in which both the high- and low-side power switches are held off. This is done to ensure that the power switch has fully turned off before the second power switch is turned on. This minimum dead time is automatically inserted whenever the external dead time is shorter than DT. External dead times larger than DT are not modified by the gate driver. Figure. 4 illustrates the dead time period and the relationship between the output gate signals.

Figure. 4 Dead time protection

## GATE DRIVER (HO1, 2, 3/LO1, 2, 3)

Low side and high side driver outputs are specifically designed for pulse operation and dedicated to drive power devices such as IGBT and power MOSFET. Low side outputs (i.e. LO1, 2, 3) are state triggered by the respective inputs, while high side outputs (i.e. HO1,2,3) are only changed at the edge of the respective inputs. After releasing from an undervoltage condition of the VBS supply, a new turn-on signal (edge) is necessary to activate the respective high side output. In contrast, after releasing from an under-voltage condition of the VCC supply, the low side outputs may directly switch to the state of their respective inputs without the additional constraints of the high side driver.

#### STANDBY MODE

The PT5619 packaged in TSSOP24L provides an enable pin (ENB) to allow the device to work in a low current dissipation state. Pin ENB is compatible with 3.3/5V logic level. If ENB is set to logic HIGH, the device is forced into standby mode and all gate driver outputs are locked into a logic LOW state and only  $46\mu$ A (typ.) is dissipated. If ENB goes from logic HIGH to logic LOW and incorporates a delay of  $6\mu$ s (typ.), the device may be released from standby mode and all outputs are enabled. In order to lower the bias current, a sufficiently large resistor ( $100k\Omega$ ) is tied between ENB and COM.

## ABSOLUTE MAXIMUM RATINGS

Stresses exceeding the absolute maximum ratings may damage the device or cause abnormal function. All the voltage parameters are absolute voltages referenced to IC COM unless otherwise stated in the table.

| Parameter                                 | Symbol                                                | Min.                     | Max.                       | Units |

|-------------------------------------------|-------------------------------------------------------|--------------------------|----------------------------|-------|

| High-side floating supply voltage         | V <sub>B1,2,3</sub>                                   | -0.3                     | 90                         |       |

| High-side offset voltage                  | V <sub>S1,2,3</sub>                                   | V <sub>B1,2,3</sub> –20  | V <sub>B1,2,3</sub> +0.3   |       |

| High-side gate driver output voltage      | V <sub>HO1,2,3</sub>                                  | V <sub>S1,2,3</sub> –0.3 | V <sub>B1,2,3</sub> +0.3   |       |

| Low-side gate driver output voltage       | V <sub>LO1,2,3</sub>                                  | COM-0.3                  | Vcc+0.3                    | ٧     |

| Logic input voltage                       | V <sub>HIN1,2,3</sub><br>V <sub>LIN1,2,3</sub><br>ENB | <b>-0</b> .3             | 20                         |       |

| Low-side supply voltage                   | Vcc                                                   | -0.3                     | 20                         |       |

| Package power dissipation @ TA≤25°C ①     | P <sub>D</sub>                                        | -                        | TSSOP20:1.2<br>TSSOP24:1.3 | W     |

| Thermal resistance, junction to ambient ① | Rth <sub>JA</sub>                                     | -                        | TSSOP20:100<br>TSSOP24:94  | °C /W |

| Allowable offset voltage slew rate        | dV/dt                                                 | -                        | 50                         | V/ns  |

| Junction temperature                      | TJ                                                    | -40                      | +150                       | °C    |

| Storage temperature                       | Ts                                                    | -40                      | +150                       | C     |

| Soldering lead temperature (duration 10s) | TL                                                    | -                        | 260                        | °C    |

Note:

## RECOMMENDED OPERATING CONDITIONS

| Parameter                                 | Symbol                                                | Min.                     | Тур. | Max.                    | Units |

|-------------------------------------------|-------------------------------------------------------|--------------------------|------|-------------------------|-------|

| Low-side supply voltage                   | Vcc                                                   | 5.5                      | -    | 18                      |       |

| High-side floating supply offset voltage② | V <sub>S1,2,3</sub>                                   | COM-6                    | -    | 60                      |       |

| High-side floating supply voltage         | V <sub>B1,2,3</sub>                                   | V <sub>S1,2,3</sub> +5.5 | -    | V <sub>B1,2,3</sub> +18 |       |

| High-side gate driver output voltage      | V <sub>HO1,2,3</sub>                                  | Vs                       | -    | V <sub>B</sub>          | V     |

| Low-side gate driver output voltage       | V <sub>LO1,2,3</sub>                                  | COM                      | -    | Vcc                     |       |

| Logic input voltage                       | V <sub>HIN1,2,3</sub><br>V <sub>LIN1,2,3</sub><br>ENB | 0                        | -    | 5                       |       |

| IC operating junction temperature         | TJ                                                    | -40                      | -    | +125                    | °C    |

②: For VBS=15V, normal logic operation for VS is between COM–6V to 90V. High-side circuitry will sustain current state if VS is between COM–6V to COM–V<sub>BS</sub>. The parameter is only guaranteed by design.

①:  $P_D$  and  $Rth_{JA}$  are only guaranteed by design.

## STATIC ELECTRICAL CHARACTERISTICS

$(V_{CC}-COM)=(V_B-V_S)=15V$ . Ambient temperature Ta=25°C unless otherwise specified. The  $V_{IN,TH}$ ,  $V_{I}$ , and  $I_{IN}$  parameters are referenced to COM and are applicable to all channels. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads. The  $V_{CCUV}$  parameters are referenced to, COM. The  $V_{BSUV}$  parameters are referenced to  $V_S$ .

| parameters are referenced to Vs.                                         |                      |                                                                               |      | _    |      |      |  |

|--------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------|------|------|------|------|--|

| Parameter                                                                | Symbol               | Test Conditions                                                               | Min. | Тур. | Max. | Unit |  |

| Low Side Power Supply Characteristics                                    | T                    |                                                                               |      | 1    | T    | ı    |  |

| Quiescent VCC supply current                                             | I <sub>QVCC1</sub>   | V <sub>HIN1,2,3</sub> =V <sub>LIN1,2,3</sub> =0 or 5V,<br>V <sub>ENB</sub> =0 | 210  | 330  | 450  |      |  |

| Quiescent VCC supply current in standby mode                             | IQVCC2               | VHIN1,2,3 = VLIN1,2,3=0 or 5V,<br>VENB=5                                      | -    | 46   | 80   | μA   |  |

| operating VCC supply current                                             | Ічссор               | f LIN1,2,3=20KHz,<br>f HIN1,2,3=20KHz,                                        | -    | 1500 | -    |      |  |

| VCC supply under-voltage positive going threshold                        | V <sub>CCUV+</sub>   | -                                                                             | 2.9  | 4.2  | 5.5  |      |  |

| VCC supply under-voltage negative going threshold                        | Vccuv-               | -                                                                             | 2.5  | 3.8  | 5.1  | V    |  |

| VCC supply under-voltage lockout hysteresis                              | Vcchys               | -                                                                             | -    | 0.4  | -    |      |  |

| High Side Floating Power Supply Charact                                  | eristics             |                                                                               |      | l .  |      | I    |  |

| High side VBS supply under-voltage positive going threshold              | V <sub>BSUV+</sub>   | -                                                                             | 2.5  | 3.8  | 5.5  |      |  |

| High side VBS supply under-voltage negative going threshold              | V <sub>BSUV</sub> -  | -                                                                             | 2.2  | 3.5  | 4.8  | V    |  |

| High side VBS supply under-voltage lockout hysteresis                    | V <sub>BSUVHYS</sub> | -                                                                             | -    | 0.3  | -    |      |  |

| High side quiescent VBS supply current                                   | I <sub>QBS</sub>     | V <sub>BS</sub> =15V                                                          | 25   | 45   | 65   |      |  |

| Offset supply leakage current                                            | I <sub>LK</sub>      | V <sub>B</sub> =V <sub>S</sub> =100V V <sub>CC</sub> =0V                      | -    | -    | 10   | μA   |  |

| Logic Input Section                                                      |                      |                                                                               |      |      |      |      |  |

| Logic HIGH input voltage HIN1,2,3,<br>LIN1,2,3 and ENB                   | ViH                  | -                                                                             | 2.5  | -    | -    |      |  |

| Logic LOW input voltage HIN1,2,3,<br>LIN1,2,3 and ENB                    | VıL                  | -                                                                             | -    | -    | 0.8  | V    |  |

| Input positive going threshold                                           | V <sub>IN,TH+</sub>  | -                                                                             | -    | 1.9  | -    |      |  |

| Input negative going threshold                                           | V <sub>IN,TH</sub> - | -                                                                             | -    | 1.4  | -    |      |  |

| Logic HIGH input bias current                                            | I <sub>IN+</sub>     | V <sub>IN</sub> =5V                                                           | -    | 50   | -    |      |  |

| Logic LOW input bias current                                             | I <sub>IN</sub> -    | V <sub>IN</sub> =0                                                            | -    | 0    | -    | μA   |  |

| Gate Driver Output Section                                               |                      |                                                                               |      |      |      |      |  |

| High side output HIGH short-circuit pulse current                        | I <sub>HO+</sub>     | V <sub>HO</sub> =V <sub>S</sub> =0                                            | -    | 1.2  | -    |      |  |

| High side output LOW short-circuit pulse current                         | Іно-                 | V <sub>HO</sub> =V <sub>B</sub> =15V                                          | -    | 2.0  | -    | _    |  |

| Low side output HIGH short-circuit pulse current                         | I <sub>LO+</sub>     | V <sub>LO</sub> =0                                                            | -    | 1.2  | -    | Α    |  |

| Low side output LOW short-circuit pulse current                          | I <sub>LO</sub> -    | VLO=VCC=15V                                                                   | -    | 2.0  | -    |      |  |

| Allowable negative VS voltage for HIN1,2,3 signal propagation to HO1,2,3 | V <sub>SN</sub>      | V <sub>BS</sub> =15V                                                          | -    | -8   | -    | V    |  |

# DYNAMIC ELECTRICAL CHARACTERISTICS

$(V_{CC}-COM)=(V_B-V_S)=15V$ ,  $V_{S1,2,3}=COM$ , and  $C_{load}=1$ nF unless otherwise specified, ambient temperature TA=25°C.

| Parameter                                             | Symbol               | Test Conditions                                                                                   | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| Turn-on propagation delay                             | t <sub>on</sub>      | V <sub>HIN1,2,3</sub> or V <sub>LIN1,2,3</sub> =5V,<br>V <sub>S1,2,3</sub> =0                     | -    | 120  | 200  |      |

| Turn-off propagation delay                            | t <sub>off</sub>     | VHIN1,2,3 or VLIN1,2,3=0, VS1,2,3=0                                                               | -    | 120  | 200  |      |

| Turn-on rise time                                     | tr                   | V <sub>HIN1,2,3</sub> or V <sub>LIN1,2,3</sub> =5V,<br>V <sub>S1,2,3</sub> =0                     | -    | 37   | -    |      |

| Turn-off fall time                                    | t <sub>f</sub>       | VHIN1,2,3 or VLIN1,2,3=0, VS1,2,3=0                                                               | -    | 30   | -    |      |

| Dead time                                             | DT                   | V <sub>HIN1,2,3</sub> or V <sub>LIN1,2,3</sub> =0 and 5V, without external dead time              | 300  | 500  | 700  | ns   |

| Dead time matching (all six channels)                 | MDT                  | without external dead time                                                                        | -    | -    | 50   |      |

| Delay matching (all six channels)                     | MT                   | external dead time > 1000ns                                                                       | -    | -    | 50   |      |

| Output pulse-width matching                           | PM                   | external dead time > 1000ns,<br>PW <sub>IN</sub> =10µs,<br>PM=PW <sub>OUT</sub> -PW <sub>IN</sub> | 1    | -    | 50   |      |

| ENB input filter time                                 | t <sub>FLT,ENB</sub> | V <sub>ENB</sub> =0 and 5V                                                                        | -    | 450  | -    |      |

| ENB input logic HIGH to HO/LO turn-<br>off delay time | t <sub>off,ENB</sub> | V <sub>ENB</sub> =5V                                                                              | -    | 0.55 | -    | ПС   |

| ENB input logic LOW to HO/LO turn-<br>on delay time   | t <sub>on,ENB</sub>  | V <sub>ENB</sub> =0V                                                                              | -    | 6    | -    | μs   |

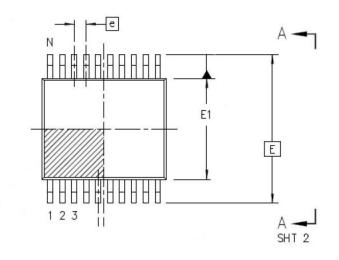

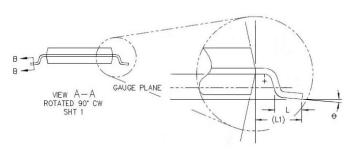

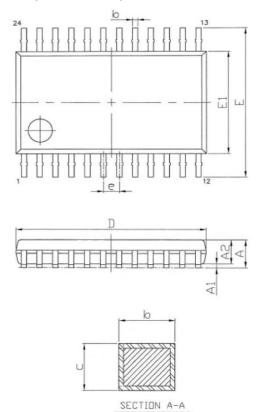

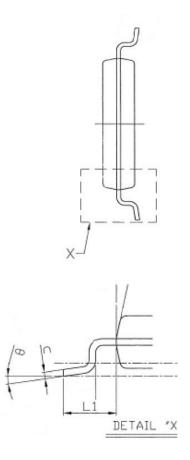

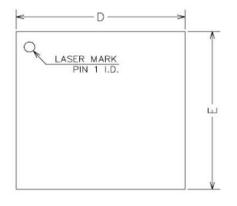

## PACKAGE INFORMATION

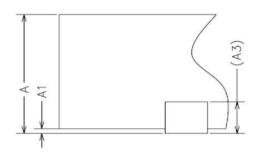

# 20 PINS, TSSOP, 173MIL

SECTION B-B

| Symbol |          | Dimensions(mm | )    |  |

|--------|----------|---------------|------|--|

| Symbol | Min.     | Nom.          | Max. |  |

| Α      | -        |               | 1.20 |  |

| A1     | 0.05     | •             | 0.15 |  |

| A2     | 0.80     | 1.00          | 1.05 |  |

| b      | 0.19     | •             | 0.30 |  |

| С      | 0.09     |               | 0.20 |  |

| е      |          | 0.65BSC       |      |  |

| D      | 6.40     | 6.50          | 6.60 |  |

| E      | 6.4 BSC  |               |      |  |

| E1     | 4.30     | 4.40          | 4.50 |  |

| L      | 0.45     | 0.60          | 0.75 |  |

| L1     | 1.00 REF |               |      |  |

| θ      | 0°       | -             | 8°   |  |

#### Notes:

- 1. All dimensions refer to JEDEC MO-153 AC

- 2. All dimensions are in mm

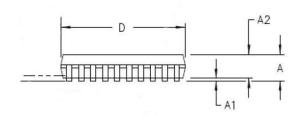

# 24 PINS, TSSOP, 173MIL

| Symbol | Dimensions(mm) |      |      |  |

|--------|----------------|------|------|--|

| Symbol | Min.           | Nom. | Max. |  |

| Α      | -              | -    | 1.20 |  |

| A1     | 0.05           | -    | 0.15 |  |

| A2     | 0.80           | 1.00 | 1.05 |  |

| b      | 0.19           | 0.20 | 0.30 |  |

| С      | 0.09           | -    | 0.20 |  |

| е      | 0.65 BSC       |      |      |  |

| D      | 7.70           | 7.80 | 7.90 |  |

| E      | 6.20           | 6.40 | 6.60 |  |

| E1     | 4.30           | 4.40 | 4.50 |  |

| L1     | 1.00 REF       |      |      |  |

| θ      | 0°             | -    | 8°   |  |

#### Notes:

- 1. All dimensions refer to JEDEC MO-153 ADT

- 2. All dimensions are in mm

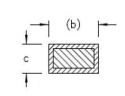

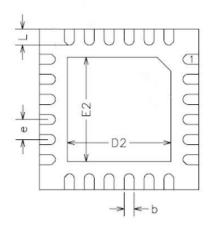

# 24 PINS, QFN

| Symbol | Dimensions(mm) |          |      |  |  |

|--------|----------------|----------|------|--|--|

| Symbol | Min.           | Nom.     | Max. |  |  |

| Α      | 0.70           | 0.75     | 0.80 |  |  |

| A1     | 0.00           | 0.02     | 0.05 |  |  |

| A3     |                | 0.20 REF |      |  |  |

| b      | 0.18           | 0.25     | 0.30 |  |  |

| D      |                | 4.00 BSC |      |  |  |

| D2     | 2.50           | 2.65     | 2.80 |  |  |

| E      |                | 4.00 BSC |      |  |  |

| E2     | 2.50           | 2.65     | 2.80 |  |  |

| е      | 0.50 BSC       |          |      |  |  |

| L      | 0.35           | 0.40     | 0.45 |  |  |

#### Notes:

1. 2. All dimensions refer to JEDEC MO-220 WGGD-6

All dimensions are in mm

## IMPORTANT NOTICE

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian, Taipei 23145, Taiwan

Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw