intersi

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## CA3160, CA3160A

Data Sheet

September 1998

File Number 976.3

## 4MHz, BiMOS Operational Amplifier with MOSFET Input/CMOS Output

The CA3160A and CA3160 are integrated circuit operational amplifiers that combine the advantage of both CMOS and bipolar transistors on a monolithic chip. The CA3160 series are frequency compensated versions of the popular CA3130 series.

Gate protected P-Channel MOSFET (PMOS) transistors are used in the input circuit to provide very high input impedance, very low input current, and exceptional speed performance. The use of PMOS field effect transistors in the input stage results in common-mode input voltage capability down to 0.5V below the negative supply terminal, an important attribute in single supply applications.

A complementary symmetry MOS (CMOS) transistor-pair, capable of swinging the output voltage to within 10mV of either supply voltage terminal (at very high values of load impedance), is employed as the output circuit.

The CA3160 Series circuits operate at supply voltages ranging from 5V to 16V, or  $\pm 2.5V$  to  $\pm 8V$  when using split supplies, and have terminals for adjustment of offset voltage for applications requiring offset null capability. Terminal provisions are also made to permit strobing of the output stage.

The CA3160A offers superior input characteristics over those of the CA3160.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE         | PKG<br>NO. |

|-------------|----------------------------------|-----------------|------------|

| CA3160AE    | -55 to 125                       | 8 Ld PDIP       | E8.3       |

| CA3160E     | -55 to 125                       | 8 Ld PDIP       | E8.3       |

| CA3160T     | -55 to 125                       | 8 Pin Metal Can | T8.C       |

#### Features

- MOSFET Input Stage Provides:

- Very High  $Z_{I} = 1.5T\Omega (1.5 \times 10^{12} \Omega)$  (Typ)

- Common-Mode Input Voltage Range Includes Negative Supply Rail; Input Terminals Can Be Swung 0.5V Below Negative Supply Rail

- CMOS Output Stage Permits Signal Swing to Either (or Both) Supply Rails

## Applications

- Ground Referenced Single Supply Amplifiers

- Fast Sample Hold Amplifiers

- Long Duration Timers/Monostables

- High Input Impedance Wideband Amplifiers

- Voltage Followers (e.g., Follower for Single Supply D/A Converter)

- Wien-Bridge Oscillators

- Voltage Controlled Oscillators

- Photo Diode Sensor Amplifiers

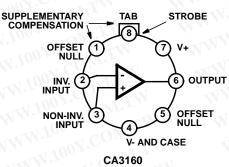

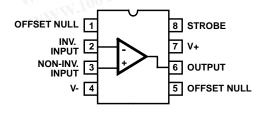

#### Pinouts

(PDIP) TOP VIEW

NOTE: CA3160 Series devices have an on-chip frequency compensation network. Supplementary phase compensation or frequency roll-off (if desired) can be connected externally between Terminals 1 and 8.

#### **Absolute Maximum Ratings**

| Supply Voltage (Between V+ and V- Terminals) | +16V               |

|----------------------------------------------|--------------------|

| Differential Mode Input Voltage              |                    |

| Input Voltage (\                             | /+ +8V) to (V0.5V) |

| Input Current                                | 1mA                |

| Output Short Circuit Duration (Note 2)       | Indefinite         |

#### **Operating Conditions**

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www. 100y. com. tw

## Thermal Information

| Thermal Resistance (Typical, Note 1)    | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)  |

|-----------------------------------------|-------------------------------------|--------------------------------------|

| PDIP Package                            | 110                                 | N/A                                  |

| Metal Can Package                       | 170                                 | 85                                   |

| Maximum Junction Temperature (Metal Can | )                                   | 175 <sup>0</sup> C                   |

| Maximum Junction Temperature (Plastic P |                                     |                                      |

| Maximum Storage Temperature Range       | 65                                  | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10  | Os)                                 | 300 <sup>0</sup> C                   |

|                                         |                                     |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

2. Short Circuit may be applied to ground or to either supply.

| Electrical Specifications | $T_A = 25^{\circ}C$ , V+ = 15V, V- = 0V, Unless Otherwise Specified |

|---------------------------|---------------------------------------------------------------------|

|---------------------------|---------------------------------------------------------------------|

|                                        | N                 | TEST CONDITIONS                                | CA3160    |            |             | CA3160A |            |      | N                  |

|----------------------------------------|-------------------|------------------------------------------------|-----------|------------|-------------|---------|------------|------|--------------------|

| PARAMETER                              | SYMBOL            |                                                | MIN       | ТҮР        | MAX         | MIN     | TYP        | MAX  | UNITS              |

| Input Offset Voltage                   | IViol             | V <sub>S</sub> = ±7.5V                         | <u>Om</u> | 6          | 15          | M.n.    | 2          | 5    | mV                 |

| Input Offset Current                   | lliol             | V <sub>S</sub> = ±7.5V                         | COM       | 0.5        | 30          | W PIN   | 0.5        | 20   | pА                 |

| Input Current                          | l.                | $V_{S} = \pm 7.5 V$                            | 1 CON     | 5          | 50          | WW      | 5          | 30   | рА                 |

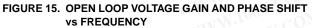

| Large-Signal Voltage Gain              | A <sub>OL</sub>   | $V_{O} = 10V_{P-P}, R_{L} = 2k\Omega$          | 50        | 320        | -           | 50      | 320        | v.co | kV/V               |

|                                        | M.TW              | WW.10                                          | 94        | 110        | -<br>1      | 94      | 110        | STC  | dB                 |

| Common-Mode Rejection Ratio            | CMRR              | I.W.                                           | 70        | 90         | -           | 80      | 95         |      | dB                 |

| Common-Mode Input-Voltage Range        | VICR              | N NN                                           | 0         | -0.5 to 12 | 10          | 0       | -0.5 to 12 | 10   | V                  |

| Power-Supply Rejection Ratio           | PSRR              | $\Delta V_{IO}/\Delta V_S$ , $V_S = \pm 7.5 V$ | 1001      | 32         | 320         | - 1     | 32         | 150  | μV/V               |

| Maximum Output Voltage                 | V <sub>OM</sub> + | $R_L = 2k\Omega$                               | 12        | 13.3       | TN          | 12      | 13.3       | 100  | V                  |

|                                        | V <sub>OM</sub> - | WW WT                                          | 10        | 0.002      | 0.01        | -       | 0.002      | 0.01 | V                  |

|                                        | V <sub>OM</sub> + | R <sub>L</sub> = ∞                             | 14.99     | 15         |             | 14.99   | 15         | -11  | V                  |

|                                        | V <sub>OM</sub> - |                                                | WAY.      | 0          | 0.01        | - W     | 0          | 0.01 | V                  |

| Maximum Output Current                 | I <sub>OM</sub> + | V <sub>O</sub> = 0V (Source)                   | 12        | 22         | 45          | 12      | 22         | 45   | mA                 |

|                                        | IOM-              | $V_{O} = 15V$ (Sink)                           | 12        | 20         | 45          | 12      | 20         | 45   | mA                 |

| Supply Current (Note 3)                | N.10+             | $V_{O} = 7.5V, R_{L} = \infty$                 | <u> </u>  | 10         | 15          | <u></u> | 10         | 15   | mA                 |

|                                        | W.100Y            | $V_{O} = 0V, R_{L} = \infty$                   | <u>N</u>  | 2          | 3           | M.T.    | 2          | 3    | mA                 |

| Input Offset Voltage Temperature Drift | 100               | $\Delta V_{IO}/\Delta T$                       | 211       | 8          | N. <u>.</u> | T.IV    | 6          | N.   | μV/ <sup>o</sup> C |

**Electrical Specifications** For Design Guidance,  $V_{SUPPLY} = \pm 7.5V$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified

| WW.10                                 |                | 1.1                                                       | WW.Ioo            | CA3160 | CA3160A |        |

|---------------------------------------|----------------|-----------------------------------------------------------|-------------------|--------|---------|--------|

| PARAMETER SY                          |                | TEST CONDITIONS                                           |                   | ТҮР    | ТҮР     | UNITS  |

| Input Offset Voltage Adjustment Range | 00X.C          | $10k\Omega$ Across Terminals 4 and 5 or Terminals 4 and 1 |                   | ±22    | ±22     | mV     |

| Input Resistance                      | RI             | JO <sub>M</sub> .,                                        |                   | 1.5    | 1.5     | ТΩ     |

| Input Capacitance                     | CI             | f = 1MHz                                                  |                   | 4.3    | 4.3     | pF     |

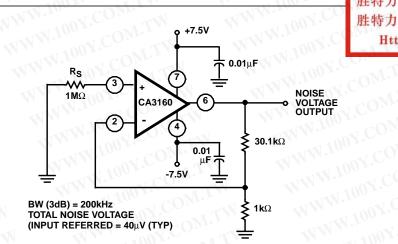

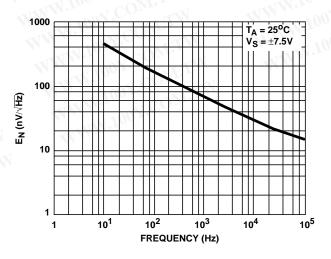

| Equivalent Input Noise Voltage        | e <sub>N</sub> | BW = 0.2MHz                                               | $R_S = 1M\Omega$  | 40     | 40      | μV     |

|                                       |                |                                                           | $R_S = 10M\Omega$ | 50     | 50      | μV     |

| Equivalent Input Noise Voltage        | e <sub>N</sub> | R <sub>S</sub> = 100Ω                                     | 1kHz              | 72     | 72      | nV/√Hz |

|                                       |                |                                                           | 10kHz             | 30     | 30      | nV/√Hz |

**Electrical Specifications** For Design Guidance,  $V_{SUPPLY} = \pm 7.5V$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified (Continued)

| PARAMETER                        |                    | . All          | LM MM 1007.0                                                                                       | CA3160 | CA3160A<br>TYP | UNITS |

|----------------------------------|--------------------|----------------|----------------------------------------------------------------------------------------------------|--------|----------------|-------|

|                                  |                    | SYMBOL         | TEST CONDITIONS                                                                                    | TYP    |                |       |

| Unity Gain Crossover Free        | luency             | f <sub>T</sub> | TW WWW 100Y.                                                                                       | 4      | 4              | MHz   |

| Slew Rate                        | I.WWW.I            | SR             | You WWW.                                                                                           | 10     | 10             | V/µs  |

| Transient Response Rise and Fall | Rise and Fall Time | tr             | $C_L = 25pF, R_L = 2k\Omega$ , (Voltage Follower)                                                  | 0.09   | 0.09           | μs    |

|                                  | Overshoot          | OS             | OM.1 1 11.100                                                                                      | 10     | 10             | %     |

| Settling Time                    | LM MM              | ts             | $C_L = 25pF, R_L = 2k\Omega$ , (Voltage Follower)<br>To <0.1%, V <sub>IN</sub> = 4V <sub>P-P</sub> | 1.8    | 1.8            | μs    |

**Electrical Specifications** For Design Guidance, V+ = +5V, V- = 0V, T<sub>A</sub> = 25<sup>o</sup>C, Unless Otherwise Specified

| WWW.100Y.COM.TW                 | 4                 | W.100X.CON.TV                        | CA3160   | CA3160A  | UNITS |  |

|---------------------------------|-------------------|--------------------------------------|----------|----------|-------|--|

| PARAMETER                       | SYMBOL            | TEST CONDITIONS                      | ТҮР      | TYP      |       |  |

| Input Offset Voltage            | V <sub>IO</sub>   | WWWWWWWWWWWWWWW                      | 6        | 2        | mV    |  |

| Input Offset Current            | √ I <sub>IO</sub> | WWWWWWWWWWW                          | 0.1      | 0.1      | рА    |  |

| Input Current                   | 1                 | WWW.100Y.COM                         | 2        | 2        | рА    |  |

| Common-Mode Rejection Ratio     | CMRR              | WWW.tosoy.CON                        | 80       | 90       | dB    |  |

| Large Signal Voltage Gain       | A <sub>OL</sub>   | $V_{O} = 4V_{P-P}, R_{L} = 5k\Omega$ | 100      | 100      | kV/V  |  |

|                                 | M.I.Y             | WWW.100 Y CC                         | 100      | 100      | dB    |  |

| Common-Mode Input Voltage Range | VICR              | WW.1001                              | 0 to 2.8 | 0 to 2.8 | COV   |  |

| Supply Current                  | OVI+TY            | $V_0 = 5V, R_1 = \infty$             | 300      | 300      | μΑ    |  |

|                                 | M.T               | $V_0 = 2.5V, R_L = \infty$           | 500      | 500      | μΑ    |  |

| Power Supply Rejection Ratio    | PSRR              | $\Delta V_{IO}/\Delta V+$            | 200      | 200      | μV/V  |  |

NOTE:

3. I<sub>CC</sub> typically increases by 1.5mA/MHz during operation.

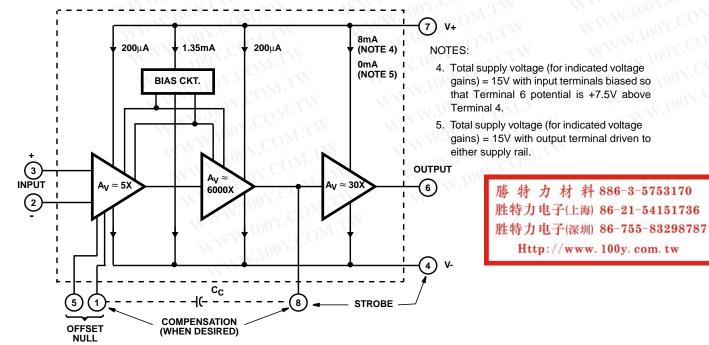

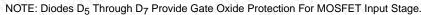

## Block Diagram

3 intersil

## Application Information

## **Circuit Description**

Refer to the Block Diagram of the CA3160 series CMOS Operational Amplifiers. The input terminals may be operated down to 0.5V below the negative supply rail, and the output can be swung very close to either supply rail in many applications. Consequently, the CA3160 series circuits are ideal for single supply operation. Three class A amplifier stages, having the individual gain capability and current consumption shown in the Block Diagram provide the total gain of the CA3160. A biasing circuit provides two potentials for common use in the first and second stages. Terminals 8 and 1 can be used to supplement the internal phase compensation network if additional phase compensation or frequency roll-off is desired. Terminals 8 and 4 can also be used to strobe the output stage into a low quiescent current state. When Terminal 8 is tied to the negative supply rail (Terminal 4) by mechanical or electrical means, the output potential at Terminal 6 essentially rises to the positive supplyrail potential at Terminal 7. This condition of essentially zero current drain in the output stage under the strobed "OFF" condition can only be achieved when the ohmic load

4

resistance presented to the amplifier is very high (e.g., when the amplifier output is used to drive MOS digital circuits in comparator applications).

勝特力材料 886-3-5753170

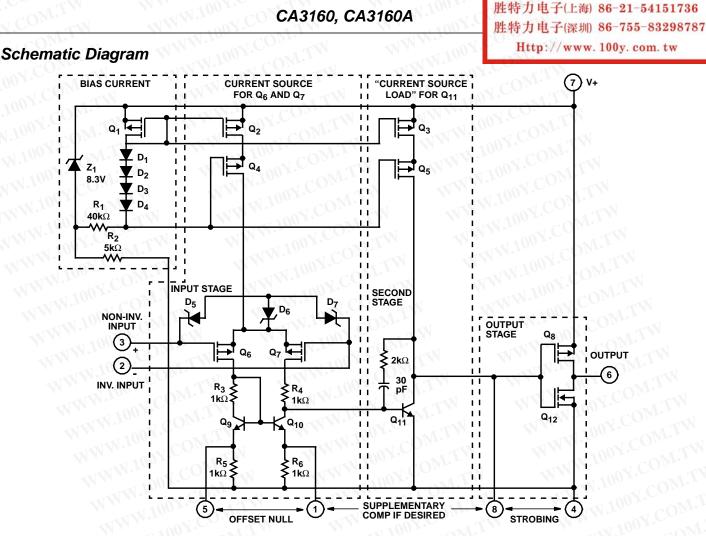

Input Stage - The circuit of the CA3160 is shown in the Schematic Diagram. It consists of a differential-input stage using PMOS field-effect transistors (Q6, Q7) working into a mirror-pair of bipolar transistors (Q9, Q10) functioning as load resistors together with resistors R<sub>3</sub> through R<sub>6</sub>. The mirrorpair transistors also function as a differential-to-single-ended converter to provide base drive to the second-stage bipolar transistor (Q11). Offset nulling, when desired, can be effected by connecting a  $100,000\Omega$  potentiometer across Terminals 1 and 5 and the potentiometer slider arm to Terminal 4. Cascode-connected PMOS transistors Q2, Q4, are the constant-current source for the input stage. The biasing circuit for the constant-current source is subsequently described. The small diodes D<sub>5</sub> through D<sub>7</sub> provide gate-oxide protection against high-voltage transients, including static electricity during handling for Q6 and Q7.

**Second-Stage** - Most of the voltage gain in the CA3160 is provided by the second amplifier stage, consisting of bipolar

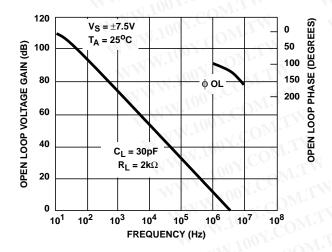

transistor  $Q_{11}$  and its cascode-connected load resistance provided by PMOS transistors  $Q_3$  and  $Q_5$ . The source of bias potentials for these PMOS transistors is described later. Miller Effect compensation (roll off) is accomplished by means of the 30pF capacitor and  $2k\Omega$  resistor connected between the base and collector of transistor  $Q_{11}$ . These internal components provide sufficient compensation for unity gain operation in most applications. However, additional compensation, if desired, may be used between Terminals 1 and 8.

**Bias-Source Circuit** - At total supply voltages, somewhat above 8.3V, resistor  $R_2$  and zener diode  $Z_1$  serve to establish a voltage of 8.3V across the series-connected circuit, consisting of resistor  $R_1$ , diodes  $D_1$  through  $D_4$ , and PMOS transistor  $Q_1$ . A tap at the junction of resistor  $R_1$  and diode  $D_4$  provides a gate-bias potential of about 4.5V for PMOS transistors  $Q_4$  and  $Q_5$  with respect to Terminal 7. A potential of about 2.2V is developed across diode-connected PMOS transistor  $Q_1$  with respect to Terminal 7 to provide gate bias for PMOS transistors  $Q_2$  and  $Q_3$ . It should be noted that  $Q_1$  is "mirror-connected" to both  $Q_2$  and  $Q_3$ . Since transistors  $Q_1$ ,  $Q_2$ ,  $Q_3$  are designed to be identical, the approximately 200 $\mu$ A current in  $Q_1$  establishes a similar current in  $Q_2$  and  $Q_3$  as constant-current sources for both the first and second amplifier stages, respectively.

At total supply voltages somewhat less than 8.3V, zener diode  $Z_1$  becomes nonconductive and the potential, developed across series-connected  $R_1$ ,  $D_1 - D_4$ , and  $Q_1$ , varies directly with variations in supply voltage. Consequently, the gate bias for  $Q_4$ ,  $Q_5$  and  $Q_2$ ,  $Q_3$  varies in accordance with supply-voltage variations. This variation results in deterioration of the power-supply-rejection ratio (PSRR) at total supply voltages below 8.3V. Operation at total supply voltages below about 4.5V results in seriously degraded performance.

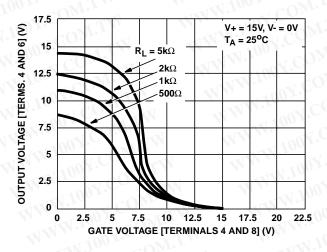

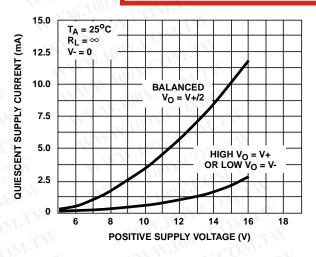

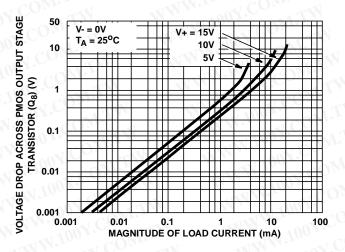

**Output Stage** - The output stage consists of a drain-loaded inverting amplifier using CMOS transistors operating in the Class A mode. When operating into very high resistance loads, the output can be swung within millivolts of either supply rail. Because the output stage is a drain-loaded amplifier, its gain is dependent upon the load impedance. The transfer characteristics of the output stage for a load returned to the negative supply rail are shown in Figure 17. Typical op amp loads are readily driven by the output stage. Because largesignal excursions are non-linear, requiring feedback for good waveform reproduction, transient delays may be encountered. As a voltage follower, the amplifier can achieve 0.01% accuracy levels, including the negative supply rail.

#### **Offset Nulling**

Offset-voltage nulling is usually accomplished with a  $100,000\Omega$  potentiometer connected across Terminals 1 and 5 and with the potentiometer slider arm connected to Terminal 4. A fine offset-null adjustment usually can be effected with the slider arm positioned in the mid-point of the potentiometer's total range.

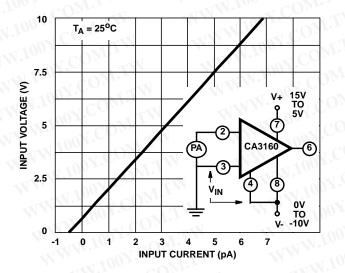

# Input Current Variation with Common Mode Input Voltage

As shown in the Electrical Specifications, the input current for the CA3160 Series Op Amps is typically 5pA at  $T_A = 25^{\circ}C$ when Terminals 2 and 3 are at a common-mode potential of +7.5V with respect to negative supply Terminal 4. Figure 23 contains data showing the variation of input current as a function of common-mode input voltage at  $T_A = 25^{\circ}C$ . These data show that circuit designers can advantageously exploit these characteristics to design circuits which typically require an input current of less than 1pA, provided the common-mode input voltage does not exceed 2V. As previously noted, the input current is essentially the result of the leakage current through the gate-protection diodes in the input circuit and. therefore, a function of the applied voltage. Although the finite resistance of the glass terminal-to-case insulator of the metal can package also contributes an increment of leakage current, there are useful compensating factors. Because the gateprotection network functions as if it is connected to Terminal 4 potential, and the metal can case of the CA3160 is also internally tied to Terminal 4, input Terminal 3 is essentially "guarded" from spurious leakage currents.

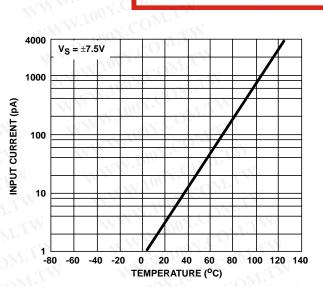

#### Input-Current Variation with Temperature

The input current of the CA3160 Series circuits is typically 5pA at 25<sup>o</sup>C. The major portion of this input current is due to leakage current through the gate-protective diodes in the input circuit. As with any semiconductor junction device, including op amps with a junction-FET input stage, the leakage current approximately doubles for every 10<sup>o</sup>C increase in temperature. Figure 24 provides data on the typical variation of input bias current as a function of temperature in the CA3160.

In applications requiring the lowest practical input current and incremental increases in current because of "warm-up" effects, it is suggested that an appropriate heat sink be used with the CA3160. In addition, when "sinking" or "sourcing" significant output current the chip temperature increases, causing an increase in the input current. In such cases, heat-sinking can also very markedly reduce and stabilize input current variations.

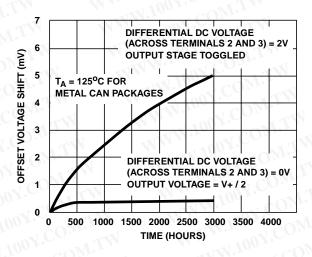

## Input Offset Voltage (V<sub>IO</sub>) Variation with DC Bias vs Device Operating Life

It is well known that the characteristics of a MOSFET device can change slightly when a DC gate-source bias potential is applied to the device for extended time periods. The magnitude of the change is increased at high temperatures. Users of the CA3160 should be alert to the possible impacts of this effect if the application of the device involves extended operation at high temperatures with a significant differential DC bias voltage applied across Terminals 2 and 3. Figure 25 shows typical data pertinent to shifts in offset voltage encountered with CA3160 devices in metal can packages during life testing. At lower temperatures (metal can and plastic) for example at 85<sup>o</sup>C, this change in voltage is considerably less. In typical linear applications where the differential voltage is small and symmetrical, these incremental changes are of about the same magnitude as those encountered in an operational amplifier employing a bipolar transistor input stage. The 2V differential voltage example represents conditions when the amplifier output state is "toggled", e.g., as in comparator applications.

#### **Power Supply Considerations**

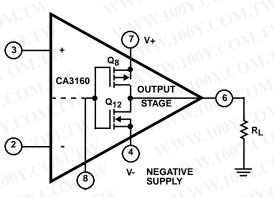

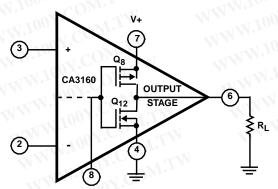

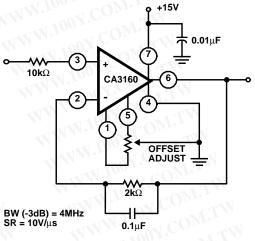

Because the CA3160 is very useful in single supply applications, it is pertinent to review some considerations relating to power supply current consumption under both single and dual supply service. Figures 1A and 1B show the CA3160 connected for both dual and single supply operation.

Dual-supply operation: When the output voltage at Terminal 6 is 0V, the currents supplied by the two power supplies are equal. When the gate terminals of  $Q_8$  and  $Q_{12}$  are driven increasingly positive with respect to ground, current flow through  $Q_{12}$  (from the negative supply) to the load is increased and current flow through  $Q_8$  (from the positive supply) decreases correspondingly. When the gate terminals of  $Q_8$  and  $Q_{12}$  are driven increasingly negative with respect to ground, current flow through  $Q_8$  (from the positive supply) decreases correspondingly. When the gate terminals of  $Q_8$  and  $Q_{12}$  are driven increasingly negative with respect to ground, current flow through  $Q_8$  is increased and current flow through  $Q_1$  is decreased accordingly.

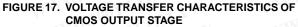

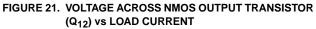

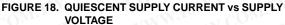

Single supply operation: Initially, let it be assumed that the value of  $R_L$  is very high (or disconnected), and that the inputterminal bias (Terminals 2 and 3) is such that the output terminal (No. 6) voltage is at V+/2, i.e., the voltage-drops across  $Q_8$  and  $Q_{12}$  are of equal magnitude. Figure 18 shows typical quiescent supply-current vs supply voltage for the CA3160 operated under these conditions.

Since the output stage is operating as a Class A amplifier, the supply current will remain constant under dynamic operating conditions as long as the transistors are operated in the linear portion of their voltage-transfer characteristics (see Figure 17). If either Q8 or Q12 are swung out of their linear regions toward cutoff (a non-linear region), there will be a corresponding reduction in supply-current. In the extreme case, e.g., with Terminal 8 swung down to ground potential (or tied to ground), NMOS transistor Q12 is completely cut off and the supply current to series connected transistors Q8, Q12 goes essentially to zero. The two preceding stages in the CA3160, however, continue to draw modest supply-current (see the lower curve in Figure 18) even though the output stage is strobed off. Figure 1A shows a dual-supply arrangement for the output stage that can also be strobed off, assuming  $R_1 = \infty$ , by pulling the potential of Terminal 8 down to that of Terminal 4.

Let it now-be assumed that a load resistance of nominal value (e.g.,  $2k\Omega$ ) is connected between Terminal 6 and ground in the circuit of Figure 1B. Let it further be assumed again that the input-terminal bias (Terminals 2 and 3) is such that the output terminal (No. 6) voltage is at V+/2. Since PMOS transistor Q<sub>8</sub> must now supply quiescent current to both R<sub>L</sub> and transistor Q<sub>12</sub>, it should be apparent that under these conditions the supply current must increase as an inverse function of the R<sub>L</sub> magnitude. Figure 20 shows the voltage-drop across PMOS transistor Q<sub>8</sub> as a function of load current at several supply

6

voltages. Figure 17 shows the voltage transfer characteristics of the output stage for several values of load resistance.

#### Wideband Noise

From the standpoint of low-noise performance considerations, the use of the CA3160 is most advantageous in applications where in the source resistance of the input signal is on the order of  $1M\Omega$  or more. In this case, the total input-referred noise voltage is typically only  $40\mu$ V when the test circuit amplifier of Figure 2 is operated at a total supply voltage of 15V. This value of total input-referred noise remains essentially constant, even though the value of source resistance is raised by an order of magnitude. This characteristic is due to the fact that reactance of the input capacitance becomes a significant factor in shunting the source resistance. It should be noted, however, that for values of source resistance very much greater than  $1M\Omega$ , the total noise voltage generated can be dominated by the thermal noise contributions of both the feedback and source resistors.

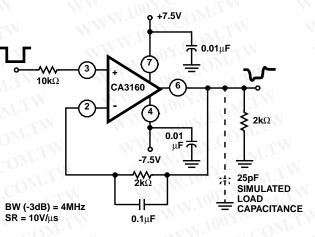

FIGURE 1A. DUAL POWER SUPPLY OPERATION

FIGURE 1B. SINGLE POWER SUPPLY OPERATION FIGURE 1. CA3160 OUTPUT STAGE IN DUAL AND SINGLE POWER SUPPLY OPERATION

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## WW.100Y.COM CA3160, CA3160A

特力材料 886-3-5753170 勝 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Typical Performance Curves

WW.100Y.COM.TW

WWW.100Y.COM

WW.1002

<u>.c</u>on.tw

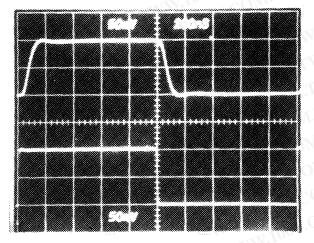

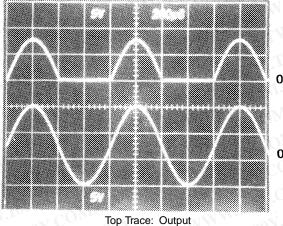

Top Trace: Output Bottom Trace: Input

FIGURE 3B. SMALL SIGNAL RESPONSE

7

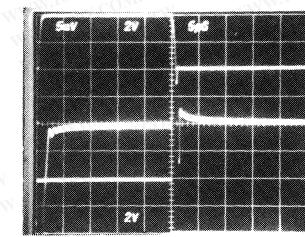

Top Trace: Output Signal Center Trace: Difference Signal 5mV/Div. Bottom Trace: Input Signal

FIGURE 3C. INPUT-OUTPUT DIFFERENCE SIGNAL SHOWING SETTLING TIME

FIGURE 3. DUAL SUPPLY VOLTAGE FOLLOWER WITH ASSOCIATED WAVEFORMS

**FIGURE 3A.**

## **Typical Applications**

#### Voltage Followers

Operational amplifiers with very high input resistances, like the CA3160, are particularly suited to service as voltage followers. Figure 3 shows the circuit of a classical voltage follower, together with pertinent waveforms using the CA3160 in a split-supply configuration.

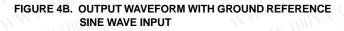

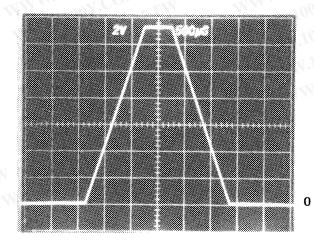

A voltage follower, operated from a single supply, is shown in Figure 4 together with related waveforms. This follower circuit is linear over a wide dynamic range, as illustrated by the reproduction of the output waveform in Figure 4B with inputsignal ramping. The waveforms in Figure 4C show that the follower does not lose its input-to-output phase-sense, even though the input is being swung 7.5V below ground potential. This unique characteristic is an important attribute in both operational amplifier and comparator applications. Figure 4C also shows the manner in which the COS/MOS output stage permits the output signal to swing down to the negative supply-rail potential (i.e., ground in the case shown). The digital-to-analog converter (DAC) circuit, described in the following section, illustrates the practical use of the CA3160 in a single supply voltage follower application.

#### 9-Bit CMOS DAC

A typical circuit of a 9-bit Digital-to-Analog Converter (DAC) (see Note 6) is shown in Figure 5. This system combines the concepts of multiple-switch CMOS ICs, a low-cost ladder network of discrete metal-oxide-film resistors, a CA3160 op amp connected as a follower, and an inexpensive monolithic regulator in a simple single power-supply arrangement. An additional feature of the DAC is that it is readily interfaced with CMOS input logic, e.g., 10V logic levels are used in the circuit of Figure 5.

The circuit uses an R/2R voltage-ladder network, with the outputpotential obtained directly by terminating the ladder arms at either the positive or the negative power supply terminal. Each CD4007A contains three inverters, each inverter functioning as a single-pole double-throw switch to terminate an arm of the R/2R network at either the positive or negative power-supply terminal. The resistor ladder is an assembly of 1% tolerance metal-oxide film resistors. The five arms requiring the highest accuracy are assembled with series and parallel combinations of 806,000 $\Omega$ resistors from the same manufacturing lot.

A single 15V supply provides a positive bus for the CA3160 follower amplifier and feeds the CA3085 voltage regulator. A "scale-adjust" function is provided by the regulator output control, set to a nominal 10V level in this system. The line-voltage regulation (approximately 0.2%) permits a 9-bit accuracy to be maintained with variations of several volts in the supply. The flexibility afforded by the CMOS building blocks simplifies the design of DAC systems tailored to particular needs.

#### NOTE:

6. "Digital-to-Analog Conversion Using the Intersil CD4007A COS/MOS IC", Application Note AN6080.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

FIGURE 4A.

Bottom Trace: Input

#### FIGURE 4C. OUTPUT SIGNAL WITH INPUT SIGNAL RAMPING

FIGURE 4. SINGLE SUPPLY VOLTAGE FOLLOWER WITH ASSOCIATED WAVEFORMS. (e.g., FOR USE IN SINGLE SUPPLY D/A CONVERTER; SEE FIGURE 9 IN AN6080)

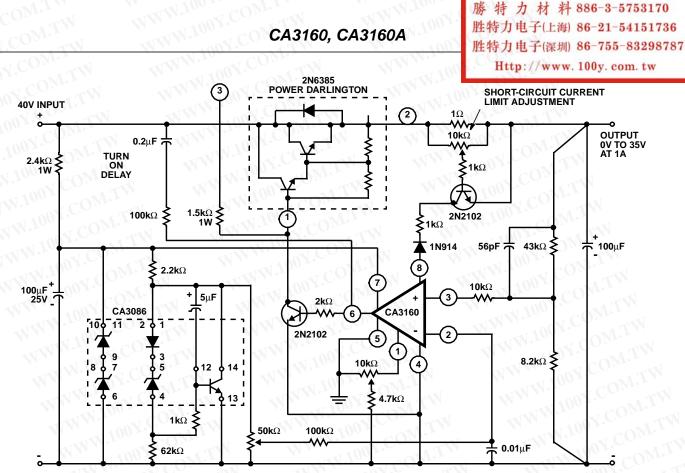

#### Error-Amplifier in Regulated Power Supplies

The CA3160 is an ideal choice for error-amplifier service in regulated power supplies since it can function as an erroramplifier when the regulated output voltage is required to approach zero.

The circuit shown in Figure 6 uses a CA3160 as an error amplifier in a continuously adjustable 1A power supply. One of the key features of this circuit is its ability to regulate down to the vicinity of 0V with only one DC power supply input.

An RC network, connected between the base of the output drive transistor and the input voltage, prevents "turn-on overshoot", a condition typical of many operational amplifier regulator circuits. As the amplifier becomes operational, this RC network ceases to have any influence on the regulator performance.

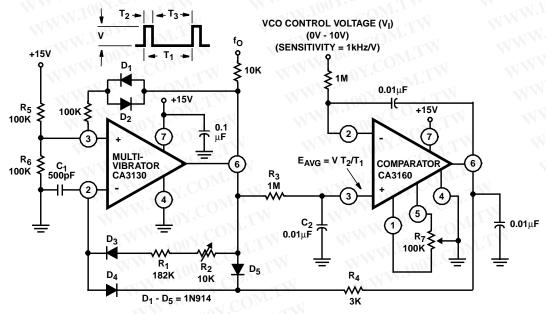

#### Precision Voltage-Controlled Oscillator

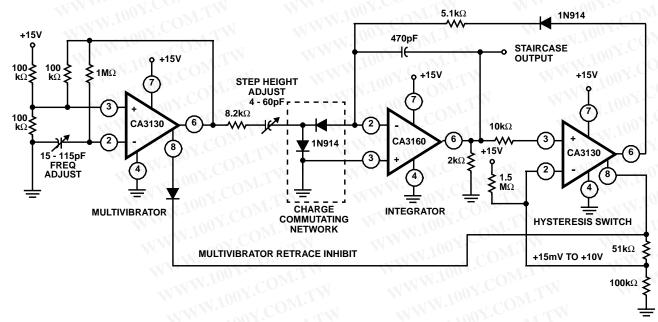

The circuit diagram of a precision voltage-controlled oscillator is shown in Figure 7. The oscillator operates with a tracking error in the order of 0.02% and a temperature coefficient of  $0.01\%/^{O}C$ . A multivibrator (A<sub>1</sub>) generates pulses of constant

amplitude (V) and width (T<sub>2</sub>). Since the output (Terminal 6) of A<sub>1</sub> (a CA3130) can swing within about 10mV of either supplyrail, the output pulse amplitude (V) is essentially equal to V+. The average output voltage ( $E_{AVG} = V T_2/T_1$ ) is applied to the non-inverting Input terminal of comparator A<sub>2</sub> via an integrating network R<sub>3</sub>, C<sub>2</sub>. Comparator A<sub>2</sub> operates to establish circuit conditions such that  $E_{AVG} = V_1$ . This circuit condition is accomplished by feeding an output signal from Terminal 6 of A<sub>2</sub> through R<sub>4</sub>, D<sub>4</sub> to the inverting terminal (Terminal 2) of A<sub>1</sub>, thereby adjusting the multivibrator interval, T<sub>3</sub>.

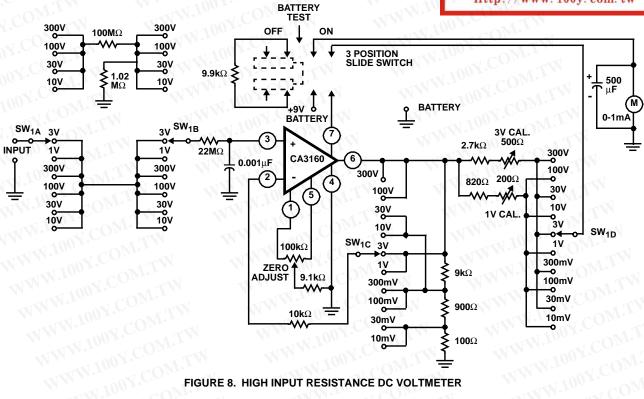

#### Voltmeter With High Input Resistance

The voltmeter circuit shown in Figure 8 illustrates an application in which a number of the CA3160 characteristics are exploited. Range-switch SW<sub>1</sub> is ganged between input and output circuitry to permit selection of the proper output voltage for feedback to Terminal 2 via  $10k\Omega$  current-limiting resistor. The circuit is powered by a single 8.4V mercury battery. With zero input signal, the circuit consumes somewhat less than  $500\mu$ A plus the meter current required to indicate a given voltage. Thus, at full scale input, the total supply current rises to slightly more than  $1500\mu$ A.

FIGURE 5. 9-BIT DAC USING CMOS DIGITAL SWITCHES AND CA3160

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Hum and Noise Output <250 $\mu$ V<sub>RMS</sub>; Regulation (No Load to Full Load) <0.005%; Input Regulation <0.01%/V

#### FIGURE 6. VOLTAGE REGULATOR CIRCUIT (0.1V TO 35V AT 1A)

#### FIGURE 7. VOLTAGE CONTROLLED OSCILLATOR

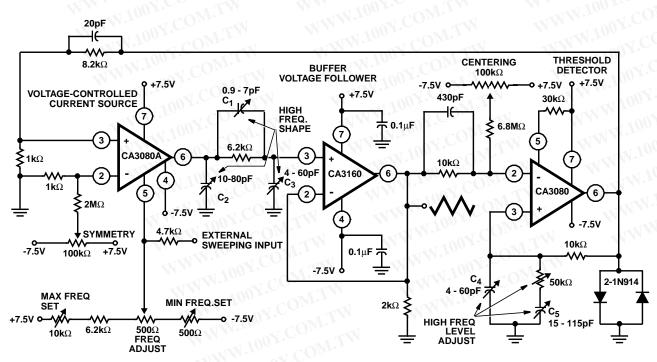

#### **Function Generator**

A function generator having a wide tuning range is shown in Figure 9. The adjustment range, in excess of 1,000,000/1, is accomplished by a single potentiometer. Three operational amplifiers are utilized: a CA3160 as a voltage follower, a CA3080 as a high speed comparator, and a second

10

CA3080A as a programmable current source. Three variable capacitors C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub> shape the triangular signal between 500kHz and 1MHz. Capacitors C<sub>4</sub>, C<sub>5</sub>, and the trimmer potentiometer in series with C<sub>5</sub> maintain essentially constant (+10%) amplitude up to 1MHz.

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

FIGURE 9A. 1,000,000/1 SINGLE CONTROL FUNCTION GENERATOR: 1Hz to 1MHz

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

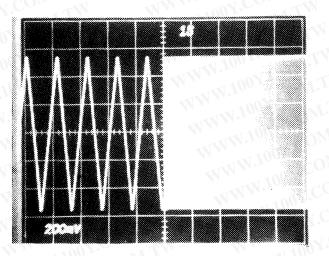

NOTE: A square wave signal modulates the external sweeping input to produce 1Hz and 1MHz, showing the 1,000,000/1 frequency range of the Function Generator.

## FIGURE 9B. TWO-TONE OUTPUT SIGNAL FROM THE FUNCTION GENERATOR

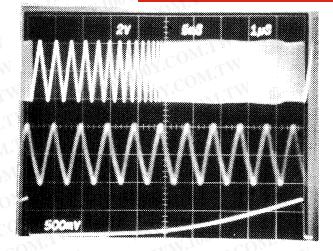

NOTE: The bottom trace is the sweeping signal and the top trace is the actual generator output. The center trace displays the 1MHz signal via delayed oscilloscope triggering of the upper swept output signal.

FIGURE 9C. TRIPLE-TRACE OF THE FUNCTION GENERATOR SWEEPING TO 1MHz

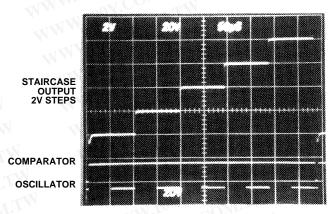

#### Staircase Generator

Figure 10 shows a staircase generator circuit utilizing three CMOS operational amplifiers. Two CA3130s are used; one as a multivibrator, the other as a hysteresis switch. The third amplifier, a CA3160, is used as a linear staircase generator.

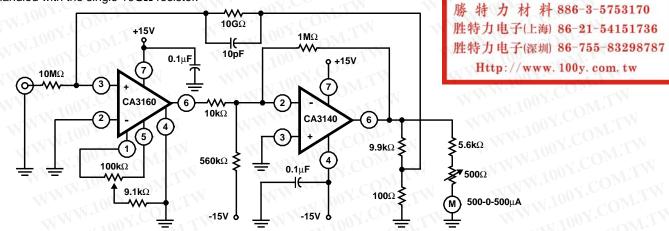

#### **Picoammeter Circuit**

Figure 11 is a current-to-voltage converter configuration utilizing a CA3160 and CA3140 to provide a picoampere

12

meter for 13pA full scale meter deflection. By placing Terminals 2 and 4 of the CA3160 at ground potential, the CA3160 input is operated in the "guarded mode". Under this operating condition, even slight leakage resistance present between Terminals 3 and 2 or between Terminals 3 and 4 would result in zero voltage across this leakage resistance, thus substantially reducing the leakage current.

If the CA3160 is operated with the same voltage on input Terminals 3 and 2 as on Terminal 4, a further reduction in the input current to the less than one picoampere level can be achieved as shown in Figure 23.

To further enhance the stability of this circuit, the CA3160 can be operated with its output (Terminal 6) near ground, thus markedly reducing the dissipation by reducing the supply current to the device.

The CA3140 stage serves as a X100 gain stage to provide the required plus and minus output swing for the meter and feedback network. A 100-to-1 voltage divider network consisting of a 9.9k $\Omega$  resistor in series with a 100 $\Omega$  resistor sets the voltage at the 10G $\Omega$  resistor (in series with Terminal 3) to ±30mV full-scale deflection. This 30mV signal results from ±3V appearing at the top of the voltage divider network which also drives the meter circuitry.

By utilizing a switching technique in the meter circuit and in the  $9.9k\Omega$  and  $100\Omega$  network similar to that used in voltmeter circuit shown in Figure 8, a current range of 3pA to 1nA full scale can be handled with the single  $10G\Omega$  resistor.

Top Trace: Staircase Output 2V Steps Center Trace: Comparator Bottom Trace: Oscillator

FIGURE 10B. STAIRCASE GENERATOR WAVEFORM FIGURE 10. STAIRCASE GENERATOR CIRCUIT

FIGURE 11. CURRENT-TO-VOLTAGE CONVERTER TO PROVIDE A PICOAMMETER WITH ±3pA FULL SCALE DEFLECTION

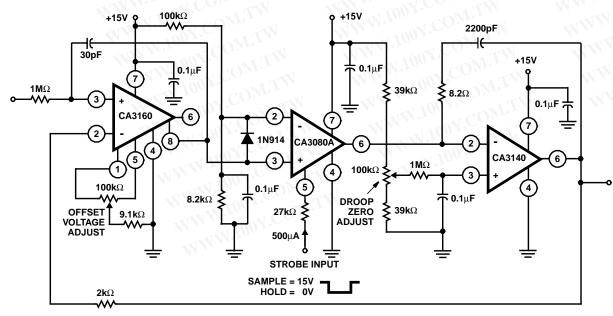

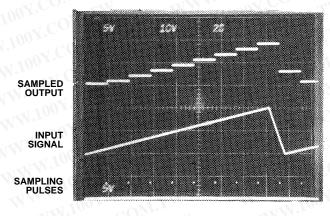

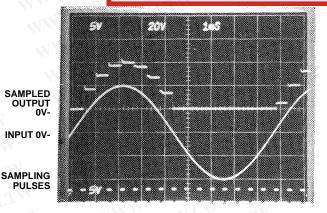

FIGURE 12A. SINGLE SUPPLY SAMPLE AND HOLD SYSTEM, INPUT 0V TO 10V

13 intersil

Top Trace: Sampled Output Center Trace: Input Signal Bottom Trace: Sampling Pulses 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Top Trace: Sampled Output Center Trace: Input Signal Bottom Trace: Sampling Pulses

# FIGURE 12B. SAMPLE AND HOLD WAVEFORM FIGURE 12C. SAMPLE AND HOLD WAVEFORM FIGURE 12. SINGLE SUPPLY SAMPLE AND HOLD SYSTEM, INPUT 0V TO 10V

#### Single Supply Sample-and-Hold System

Figure 12 shows a single supply sample-and-hold system using a CA3160 to provide a high input impedance and an input voltage range of 0V to 10V. The output from the input buffer integrator network is coupled to a CA3080A. The CA3080A functions as a strobeable current source for the CA3140 output integrator and storage capacitor. The CA3140 was chosen because of its low output impedance and constant gain-bandwidth product. Pulse "droop" during the hold interval can be reduced to zero by adjusting the 100k $\Omega$  bias-voltage potentiometer on the positive input of the CA3140. This zero adjustment sets the CA3080A output voltage at its zero current position. In this sample-and-hold circuit it is essential that the amplifier bias current be reduced to zero to minimize output signal current during the hold mode. Even with 320mV at the amplifier bias circuit terminal (5) at least 1100pA of output current will be available.

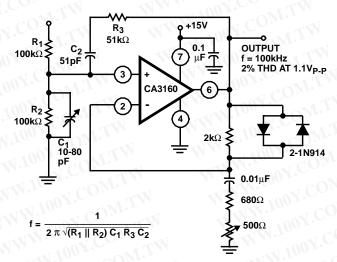

#### Wien Bridge Oscillator

A simple, single supply Wien Bridge oscillator using a CA3160 is shown in Figure 13. A pair of parallel-connected 1N914 diodes comprise the gain-setting network which standardizes the output voltage at approximately 1.1V. The  $500\Omega$  potentiometer is adjusted so that the oscillator will always start and the oscillation will be maintained. Increasing the amplitude of the voltage may lower the threshold level for starting and for sustaining the oscillation, but will introduce more distortion.

FIGURE 13. SINGLE SUPPLY WEIN BRIDGE OSCILLATOR

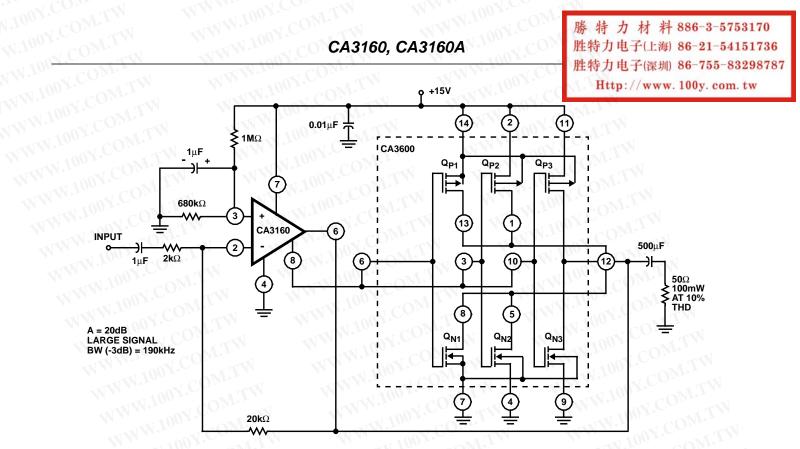

#### **Operation with Output Stage Power Booster**

The current sourcing and sinking capability of the CA3160 output stage is easily supplemented to provide power-boost capability. In the circuit of Figure 14, three CMOS transistorpairs in a single CA3600 IC array are shown parallel-connected with the output stage in the CA3160. In the Class A mode of CA3600E shown, a typical device consumes 20mA of supply current at 15V operation. This arrangement boosts the currenthandling capability of the CA3160 output stage by about 2.5X.

The amplifier circuit in Figure 14 employs feedback to establish a closed-loop gain of 20dB. The typical large-signal-bandwidth (-3dB) is 190kHz.

FIGURE 14. CMOS TRANSISTOR ARRAY (CA3600E) CONNECTED AS POWER BOOSTER IN THE OUTPUT STAGE OF THE CA3160

#### Typical Performance Curves

## Typical Performance Curves (Continued)

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

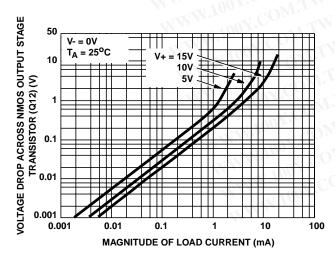

FIGURE 20. VOLTAGE ACROSS PMOS OUTPUT TRANSISTOR (Q<sub>8</sub>) vs LOAD CURRENT

FIGURE 22. EQUIVALENT NOISE VOLTAGE vs FREQUENCY

## Typical Performance Curves (Continued)

FIGURE 23. INPUT CURRENT vs COMMON MODE VOLTAGE

FIGURE 25. TYPICAL INCREMENTAL OFFSET VOLTAGE SHIFT vs OPERATING LIFE

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

<u>intersil</u>

17

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw