# Octal 8-Bit CMOS D/A Converter

DAC8800

# **FEATURES**

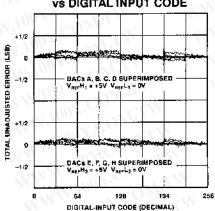

- ±1/2 LSB Total Unadjusted Error

- 2µs Settling Time

- Serial Data Input

- ±Full-Scale Output Set by V<sub>REF</sub>H and V<sub>REF</sub>L

- Unipolar and Bipolar Operation

- TTL Input Compatible

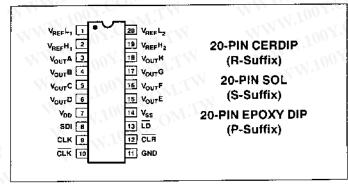

- 20-Pin DIP or SOL Package

- Low Cost

### **APPLICATIONS**

- Voltage Set Point Control

- Digital Offset & Gain Adjustment

- Microprocessor Controlled Calibration

- General Purpose Trimming Adjustments

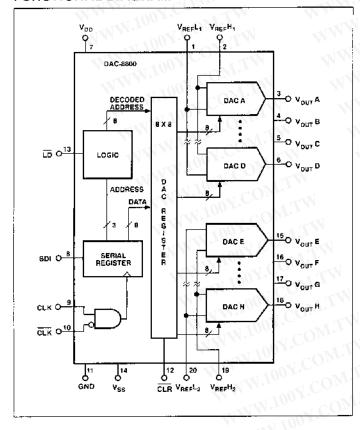

### **FUNCTIONAL DIAGRAM**

# **GENERAL DESCRIPTION**

The DAC-8800 TrimDAC<sup>TM</sup> is designed to be a general purpose digitally controlled voltage adjustment device. The output voltage range can be independently set for each set of four D/A converters. In addition, both unipolar and bipolar output voltage ranges are easy to establish by external reference input high and low terminals. The digitally-programmed output voltages are ideal for op amp trimming, voltage-controlled amplifier gain setting and any general purpose trimming tasks.

A three-wire serial digital interface loads the contents of eight internal DAC registers which establish the output voltage levels. An asynchronous Clear (CLR) input places all DACs in a zero code output condition, very handy for system power-up. An internal regulator provides TTL input compatibility over a wide range of  $\rm V_{\rm DD}$  supply voltages. Single supply operation is available by connecting  $\rm V_{\rm SS}$  to GND.

# ORDERING INFORMATION 1

| U.Y.                    | PACKAGE           | 1,1007       | . OPERATING                       |

|-------------------------|-------------------|--------------|-----------------------------------|

| CERDIP<br>20-PIN        | PLASTIC<br>20-PIN | 50<br>20-PIN | TEMPERATURE<br>RANGE              |

| DAC8800BR*<br>DAC8800FR | DAC8800FP         | DAC6800FS"   | -55°C to +125°C<br>-40°C to +85°C |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- Burn-in is available on commercial and industrial temperature range parts in CerDIP and plastic DIP packages.

- tt For availability and burn-in information on SO package, contact your local sales office.

# PIN CONNECTIONS

# REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

**ELECTRICAL CHARACTERISTICS:** (Note 1) Unless otherwise noted, SINGLE SUPPLY:  $V_{DD} = +12V$ ,  $V_{SS} = 0V$ ,  $V_{REF}H = +5V$ ,  $V_{REF}L = 0V$ ; or DUAL SUPPLY:  $V_{DD} = +12V$ ,  $V_{SS} = -5V$ ,  $V_{REF}H = +2.5V$ ,  $V_{REF}L = -2.5V$ ; F GRADE:  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ ; B GRADE:  $-55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ .

| PARAMETER                               | SYMBOL                                 | CONDITIONS                                          | MIN                | DAC-880<br>TYP | O<br>MAX              | UNITS  |

|-----------------------------------------|----------------------------------------|-----------------------------------------------------|--------------------|----------------|-----------------------|--------|

| STATIC ACCURACY All spe                 | ecifications apply for I               | DACs A, B, C, D, E, F, G, H                         | MM                 | W.Con          | TW                    |        |

| Resolution                              | N                                      | MWW. TOWN. CONT.                                    | 8                  | OUX.CO         | TVI                   | Bits   |

| Total Unadjusted Error<br>(Note 2)      | TUE                                    | WWW.100Y.COM.TW                                     | WWW.               | 100Y.CC        | ±1/2                  | LSB    |

| Differential Nonlinearity<br>(Note 3)   | DNL                                    | WWW.100Y.COM.TW                                     | MAL                | N.100 Y.C      | COM #1                | LSB    |

| Full Scale Error                        | G <sub>FSE</sub>                       | M. TOO T. COMIT                                     |                    | 11.100         | ±1/2                  | LSB    |

| Zero Code Error                         | Vzse                                   | M. 1003. COM'I.                                     | <u></u>            | VIN. 100,      | ±1/2                  | LSB    |

| DAC Output Resistance                   | Вошт                                   | WW. 1001.C. M.T.                                    | 8                  | 12             | 16                    | kΩ     |

| DAC Output Resistance Match             | AR <sub>OUT</sub> /R <sub>OUT</sub>    | WWW.100Y.COM.T                                      | - V                | 0.5            | 01.00                 | (T) %  |

| REFERENCE INPUT                         | of COM                                 | MAN AND COL                                         | TV                 | MM M.          | W.Co.                 | WILL   |

| V 100                                   | V <sub>REF</sub> H                     | Pins 2 & 19                                         | V <sub>REF</sub> L | WWW.           | (V <sub>DD</sub> - 4) | TW     |

| Voltage Range (Note 5)                  | V <sub>REF</sub> L                     | Pins 1 & 20                                         | V <sub>ss</sub>    | WWW            | V <sub>REF</sub> H    | OM. TA |

| input Resistance                        | V <sub>HEF</sub> H                     | Digital Inputs = 55 <sub>H</sub>                    | 2                  | 3              | 1.100                 | kΩ     |

| nput Resistance Match                   | ΔR <sub>REF</sub> H/R <sub>REF</sub> H | Digital Inputs = 55 <sub>H</sub>                    | MITW -             | 0.5            | W.1007.               | %      |

| Reference Input<br>Capacitance (Note 4) | C <sub>REF</sub>                       | Digital Inputs All Zeros<br>Digital Inputs All Ones | OM.TW-             | 50<br>75       | 75<br>100             | CO pF  |

| DIGITAL INPUTS                          | 11.100                                 | W.114 100                                           | COM.               |                | M.IU                  | CON    |

| ogic High                               | V <sub>INH</sub>                       | M.TW W. 100%                                        | 2.4                |                | 40                    | O.Y.   |

| Logic Low                               | VINL 100Y.C                            | WY TIOO                                             | M.E.M.             | _ 1            | 0.8                   | 007. A |

| nput Current                            | IN                                     | V <sub>IN</sub> = 0V ar +5V                         | N.CO.              | N -            | ±1                    | μA     |

| nput Capacitance (Note 4)               | CIN                                    | CONT. WWW.                                          | ON CONT            | 4              | 8                     | pF     |

| nput Coding                             | WW.100                                 | COMP. MANN'S                                        | ON COM             | BINAR          |                       | V.     |

| POWER SUPPLIES (Note 6)                 | W.100                                  | COM.                                                | Ing COM            | . I            | WW                    |        |

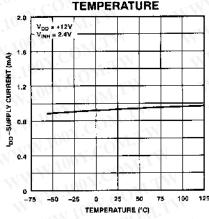

| Positive Supply Current                 | IDD                                    | Dual Supply CMOS                                    | 1007.CON           | 1<br>0.2       | 2<br>0.4              | mA     |

| Negative Supply Current                 | 'ss                                    | Oual Supply                                         | W. CO              | 0.01           | 0.2                   | mA     |

| Power Dissipation                       | P <sub>DISS</sub>                      | Single Supply Operation Dual Supply Operation       | W.1007-C           | 12<br>12       | 24<br>25              | mW     |

| OC Power Supply<br>Rejection Ratio      | PSRR                                   | ΔV <sub>DD</sub> =±5%                               | WW.1007.           | 0.001          | 0.01                  | %/%    |

| DYNAMIC PERFORMANCE (No                 | te 4)                                  | W.Ing COM.                                          | TWW.Ioo            | a COM.,        |                       |        |

| V <sub>QU1</sub> Seltling Time          | ts                                     | ±1/2 LSB Error Band                                 | W. 100             | 0.8            | 2                     | μs     |

|                                         | ст                                     | Measured Between Adjacent DAC Outputs               | _                  | 80             |                       | nVs    |

**ELECTRICAL CHARACTERISTICS:** (Note 1) Unless otherwise noted, SINGLE SUPPLY:  $V_{DD} = +12V$ ,  $V_{SS} = 0V$ ,  $V_{REF}H = +5V$ ,  $V_{REF}L = 0V$ ; or DUAL SUPPLY:  $V_{DD} = +12V$ ,  $V_{SS} = -5V$ ,  $V_{REF}H = +2.5V$ ,  $V_{REF}L = -2.5V$ ; F GRADE:  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ ; B GRADE:  $-55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ . *Continued*

|                                      | M .                               | VIOUT. COM.III          | W.100     | DAC-8800 |         |       |

|--------------------------------------|-----------------------------------|-------------------------|-----------|----------|---------|-------|

| PARAMETER                            | SYMBOL                            | CONDITIONS              | MIN       | TYP      | MAX     | UNITS |

| SWITCHING CHARACTERISTIC             | S (Notes 4, 8)                    | W. JOY.CO. TW. W.       | N. TOON.C | TIT      |         |       |

| Input Clock Pulse Width              | t <sub>cH</sub> , t <sub>cL</sub> | Clock Level High or Low | 60        | 50 1 LA  | _       | ns    |

| Data Setup Time                      | t <sub>D</sub> s                  | MM.Inc. COM.            | 30        | COJ.     | N -     | ns    |

| Data Hold Time                       | t <sub>DH</sub>                   | 27N 100 2 COM . 1       | 30        | COM      | - XXI - | ns    |

| DAC Register Load Pulse Width        | t <sub>LD</sub>                   | M. M 1001.              | 50        | COM      |         | ns    |

| Clear Pulse Width                    | t <sub>CLR</sub>                  | WW TIOON ON TW          | 50        | MO-YO    | TW-     | ns    |

| Clock Edge to Load Time              | t <sub>CKLD</sub>                 | WW TOON.CO TW           | 50        | 001:00   | LTV     | ns    |

| Load Edge to Next Clock<br>Edge Time | t <sub>LDCK</sub>                 | WWW.MOOY.COM.TW         | 50        | 1001-CO  | M.T.W   | กร    |

#### NOTES:

- Testing performed in SINGLE SUPPLY mode, except I<sub>DD</sub>, I<sub>SS</sub>, and PSRR which are tested in DUAL SUPPLY mode.

- 2. Includes Full Scale Error, Relative Accuracy, and Zero Code Error.

- 3. All devices guaranteed monolonic over the full operating temperature range.

- 4. Guaranteed by design and not subject to production test.

- V<sub>DD</sub> 4 valts is the maximum reference valtage for the above specifications. Also V<sub>REF</sub>H ≥ V<sub>REF</sub>L.

- Digital Input voltages V<sub>IN</sub> = V<sub>INL</sub> or V<sub>INH</sub> for TTL condition; V<sub>IN</sub> = 0V or +5V for CMOS condition. DAC outputs unloaded. P<sub>DISS</sub> is calculated from (I<sub>DD</sub> × V<sub>DD</sub>) + (I<sub>SS</sub> × V<sub>SS</sub>).

- + (I<sub>SS</sub> × V<sub>SS</sub>).

7. Measured at V<sub>OUT</sub> pin where an adjacent V<sub>OUT</sub> pin is making a full-scale voltage change.

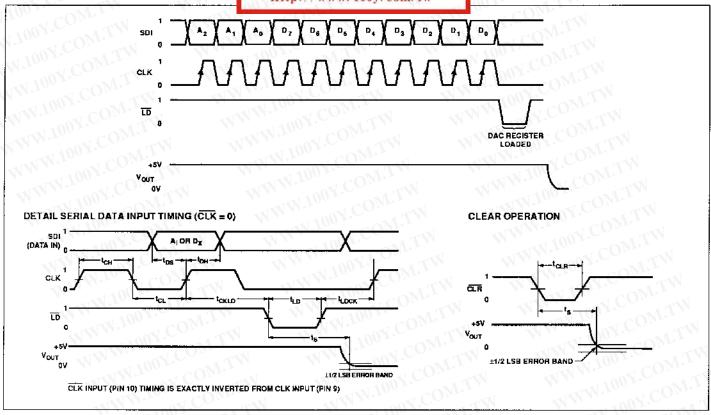

- See timing diagram for location of measured values.

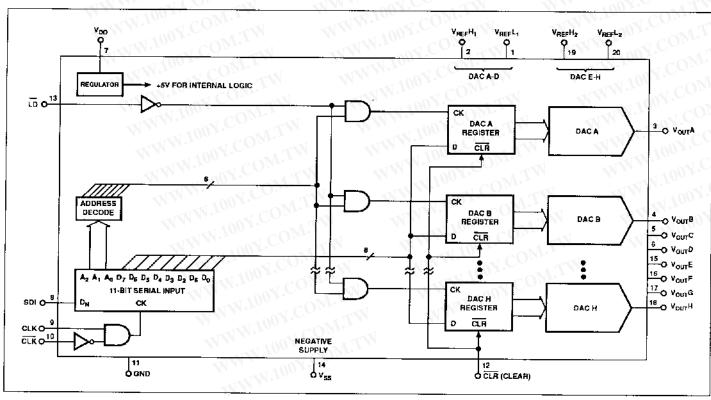

# **DETAILED DAC-8800 BLOCK DIAGRAM**

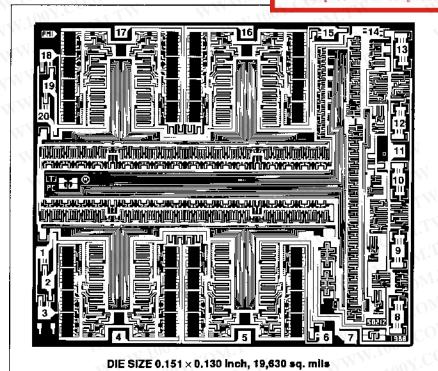

# DICE CHARACTERISTICS

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

(3.8354 × 3.3033 mm, 12.664 sq. mm)

- 1. V<sub>REF</sub>L<sub>1</sub> 2. V<sub>REF</sub>H<sub>1</sub>

- 4. VOUTE

- 5. VOUTC

- 7. V

- 6. SDI

- 9. CLK

- 10. CLK 11. GND

- 12. CLR

- 13. LD

- 14. V<sub>SS</sub>

- 16. V F

- 17. VoutG

- 18. V<sub>OUT</sub>H 19. V<sub>OEE</sub>H,

- 20. VREEL

WAFER TEST LIMITS at VDD = +12V, VSS = 0V, VREFH = +5V, VREFL = 0V; TA = +25°C unless otherwise noted.

| PARAMETER                          | SYMBOL             | Y.CO  | CONDITIONS                  | WV          | VW.100Y   | DA.        | C-8800G<br>LIMIT | UNITS            |

|------------------------------------|--------------------|-------|-----------------------------|-------------|-----------|------------|------------------|------------------|

| Total Unadjusted Error             | TUE                | Oxiv  | OWITW                       |             | -XW.100   | COM        | ±1/2             | LSB MAX          |

| Differential Nonlinearity          | DNL                | 0011  | WILMO                       | V           | 10        | M. OM.     | ±1               | LSB MAX          |

| Full Scale Error                   | G <sub>FSE</sub>   | YOUY. | COTTW                       | -           | WW        | 001.       | ±1/2             | LSB MAX          |

| Zero Code Error                    | V <sub>ZSE</sub>   | 110   | I.COM                       |             | MAM       | "UNA'COL   | ±1/2             | LSB MAX          |

| DAC Output Resistance              | Rout               | 1.10° | JY.COM.T                    | N           | WWW       | 1.100 Y.CO | 8<br>16          | kΩ MiN<br>kΩ MAX |

| Reference Input Resistance         | R <sub>REF</sub> H | 111   | Digital Inputs = 55         | SH SH       | MM.       | N 100 Y.C. | 2                | kΩ MIN           |

| Digital Inputs High                | V <sub>INH</sub>   | AM.   | ON COR                      | TW          | WW        | 1007.0     | 2.4              | V MIN            |

| Digital Inputs Low                 | V <sub>INL</sub>   | MW.   | CON.                        | W           | WV        | M. FOUT    | 0.8              | V MAX            |

| Digital Input Current              | I <sub>IN</sub>    | AT WW | V <sub>1N</sub> = 0V or +5V | VI.         | <b>**</b> | MAIN       | (CO ±1           | да МАХ           |

| Positive Supply Current            | lad                | WW    | V <sub>SS</sub> = -5V       | TTL<br>CMOS |           | NAM 100    | V.CO2<br>0.4     | mA MAX           |

| Negative Supply Current            | I <sub>SS</sub>    | WV    | V <sub>SS</sub> = -5V       | On-         | N         | MAL        | 0.2              | mA MAX           |

| DC Power Supply<br>Rejection Ratio | PSRR               | W     | $\Delta V_{D0} = \pm 5\%$   | COM         | W         | "          | 0.01             | %/% MAX          |

# NOTE:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

|                                    | E MAXIMUM RATINGS (T         | <sub>A</sub> = +25°C, unless        |

|------------------------------------|------------------------------|-------------------------------------|

| otherwise no                       | ted)                         | in a CONTITU                        |

| V <sub>nn</sub> to V <sub>ss</sub> |                              | 0V, +20V                            |

| V <sub>nn</sub> to GND .           |                              | 0V, +20V                            |

| Ves to GND.                        |                              | 20V, 0V                             |

| Digital Input                      | Voltage to GND GNI           | $D = 0.3V$ , $V_{pp} + 0.3V$        |

| V <sub>REE</sub> H to GNI          | D                            | V <sub>BEE</sub> L, V <sub>DD</sub> |

| V <sub>REE</sub> L to GNE          | D<br>D                       | ۷٫۰٫۷ کی آ                          |

| VOUT to GND                        |                              | ٧٫٫٫۴۲, ٧٫٫٫۰                       |

|                                    | mperature Range              | 10 NET TO NET                       |

| Military, DA                       | AC-8800BR                    | 55°C to +125°C                      |

| Extended I                         | ndustrial, DAC-8800FR,FP,F   | S40°C to +85°C                      |

| Maximum Jur                        | nction Temperature (T, Max). | +150°C                              |

|                                    | perature                     |                                     |

|                                    | ature (Soldering, 10 sec)    |                                     |

|                                    | ver Dissipation              |                                     |

|                                    |                              |                                     |

| PACKAGE TYPE            | ⊖ <sub>jA</sub> (Note 1) | $\Theta_{ m jc}$ | UNITS |

|-------------------------|--------------------------|------------------|-------|

| 20-Pin Hermetic DIP (R) | 76                       | 11               | °C/W  |

| 20-Pin Plastic DIP (P)  | 69                       | 27               | °C/W  |

| 20-Pin SO (S)           | 88                       | 25               | °C/W  |

### NOTE:

1.  $\Theta_{iA}$  is specified for worst case mounting conditions, i.e.,  $\Theta_{iA}$  is specified for device in socket for CerDIP, and P-DIP packages;  $\Theta_{jA}$  is specified for device soldered to printed circuit board for SO package.

- 1. Do not apply voltages higher than  $V_{\rm DD}$  or less than  $V_{\rm SS}$  potential on any terminal.

- 2. The digital control inputs are zener-protected; however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam at all times until ready to use,

- 3. Do not insert this device into powered sockets; remove power before insertion

- 4. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to device.

**TABLE 1: PIN Function Description**

| N  | MNEMONIC                        | DESCRIPTION                                                                                                                                                                                   |  |  |  |

|----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1  | V <sub>REF</sub> L <sub>1</sub> | External DAC voltage reference input shared by DAC A, B, C, D, $V_{REF}L_1$ determines the lowest negative DAC output voltage. $V_{REF}L_1$ must be equal to or more positive than $V_{SS}$ . |  |  |  |

| 2  | V <sub>REF</sub> H <sub>1</sub> | External DAC voltage reference input shared by DAC A, B, C, D, V <sub>REE</sub> H, determines the highest positive DAC output voltage.                                                        |  |  |  |

| 3  | V <sub>OUT</sub> A              | DAC A Output 1                                                                                                                                                                                |  |  |  |

| 4  | v <sub>out</sub> e              | DAC B Output                                                                                                                                                                                  |  |  |  |

| 5  | v <sub>out</sub> c              | DAC C Output Voltage determined by external V <sub>REF</sub> H <sub>1</sub> and V <sub>REF</sub> L <sub>1</sub> .                                                                             |  |  |  |

| 5  | V <sub>OUT</sub> D              | DAC D Output                                                                                                                                                                                  |  |  |  |

| 7  | $V_{DD}$                        | Positive supply, allowable input voltage range +4.5V to +16V.                                                                                                                                 |  |  |  |

| 3  | SDI                             | Serial Data Input                                                                                                                                                                             |  |  |  |

| 9  | CLK                             | Serial Clock Input, positive edge triggered                                                                                                                                                   |  |  |  |

| 10 | CLK                             | Clock Enable or Serial Clock Input, negative edge triggered                                                                                                                                   |  |  |  |

| 11 | GND                             | Ground WWW.                                                                                                                                                                                   |  |  |  |

| 2  | CLR                             | Clear Input (Active Low), Asynchronous TTL compatible input that resets all DAC registers to zero code.                                                                                       |  |  |  |

| 3  | ĹD                              | Load DAC Register Strobe, TTL compatible input that transfers data bits from serial input register into the decoded DAC register. See Table 2.                                                |  |  |  |

| 14 | v <sub>ss</sub>                 | Negative Supply, allowable input voltage range 0V to -12V.                                                                                                                                    |  |  |  |

| 15 | $v_{out}$ E                     | DAC E Output                                                                                                                                                                                  |  |  |  |

| 6  | v <sub>out</sub> F              | DAC F Output                                                                                                                                                                                  |  |  |  |

| 17 | V <sub>ou†</sub> G              | DAC G Output  Output voltage determined by external V <sub>REF</sub> H <sub>2</sub> and V <sub>REF</sub> L <sub>2</sub> .                                                                     |  |  |  |

| 18 | $v_{out}H$                      | DAC H Output                                                                                                                                                                                  |  |  |  |

| 19 | $V_{REF}H_2$                    | External DAC voltage reference input shared by DAC E, F, G, H. V <sub>REF</sub> H <sub>2</sub> determines the highest positive DAC output voltage.                                            |  |  |  |

| 20 | $V_{REF}L_2$                    | External DAC voltage reference input shared by DAC E, F, G, H, $V_{REF}L_2$ determines the lowest negative DAC output voltage. $V_{REF}L_2$ must be equal to or more positive than $V_{SS}$ . |  |  |  |

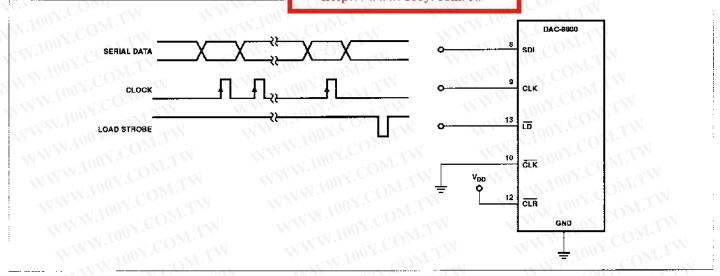

FIGURE 1: Timing Diagrams

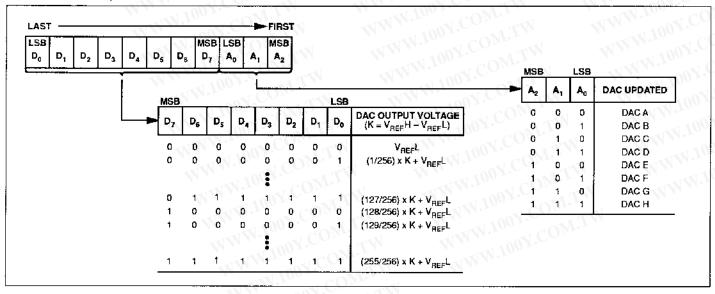

TABLE 2: Serial Input Decode Table

**TABLE 3:** Logic Control Input Truth Table

| CLK      | CLK | INPUT SHIFT REGISTER OPERATON |

|----------|-----|-------------------------------|

| <u>↑</u> | 1   | Shift Data                    |

| Н        | Ţ   | Shift Data                    |

| ï        | ×   | No Operation                  |

| X        | Н   | No Operation                  |

Http://www. 100y. com. tw

# **DAC8800**

# TYPICAL PERFORMANCE CHARACTERISTICS

# **TOTAL UNADJUSTED ERROR** vs DIGITAL INPUT CODE

**SUPPLY CURRENT vs TEMPERATURE**

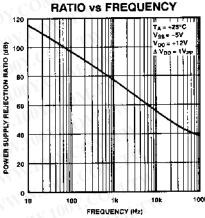

POWER SUPPLY REJECTION

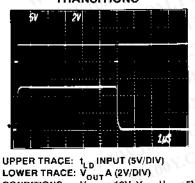

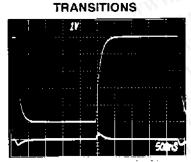

# DAC OUTPUT SETTLING TIME POSITIVE & NEGATIVE **TRANSITIONS**

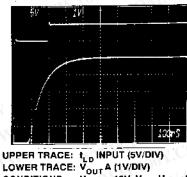

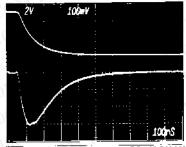

**EXPANDED DAC OUTPUT** SETTLING TIME POSITIVE TRANSITION

CONDITIONS:

V<sub>DD</sub> = +12V, V<sub>REF</sub>H<sub>1</sub> = +5V, V<sub>REF</sub>L<sub>1</sub> = 0V, V<sub>SS</sub> = 0V, H<sub>L</sub> = 1MΩ, C<sub>L</sub> = 3.4pF

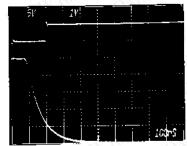

**EXPANDED DAC OUTPUT** SETTLING TIME NEGATIVE TRANSITION

UPPER TRACE: t<sub>LO</sub> INPUT (5V/DIV) LOWER TRACE: Vout A (1V/DIV)  $V_{DD} = +12V, V_{REF}H_1 = +5V, \\ V_{REF}L_1 = 0V, V_{SS} = 0V, \\ R_L = 1M\Omega, C_L = 3.4pF$ CONDITIONS:

# DAC OUTPUT CHANNEL-TO-CHANNEL CROSSTALK BOTH

CONDITIONS:

$V_{\text{DD}} = +12V, V_{\text{REF}}H_1 = +5V, V_{\text{REF}}L_1 = 0V, V_{\text{SS}} = 0V, R_L = 1M\Omega, C_L = 3.4pF$

UPPER TRACE: Vout A 0 TO +5V CHANGE LOWER TRACE: VOUTB (1V/DIV)  $V_{DD} = +12V, V_{REF}H_1 = +5V, V_{REF}L_1 = 0V, V_{SS} = 0V,$ CONDITIONS:  $R_i = 1M\Omega$ ,  $C_i = 3.4pF$

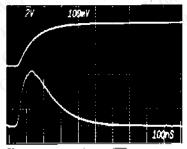

**EXPANDED DAC OUTPUT** CHANNEL-TO-CHANNEL CROSS-TALK NEGATIVE TRANSITION

UPPER TRACE: VOUT A +5V TO 0V CHANGE LOWER TRACE: VoutB (100mV/DIV)  $V_{DD} = +12V, V_{REF}H_1 \approx +5V, V_{REF}L_1 = 0V, V_{SS} = 0V, R_L = 1M\Omega, C_L \approx 3.4pF$ CONDITIONS:

# **EXPANDED DAC OUTPUT** CHANNEL-TO-CHANNEL CROSS-TALK POSITIVE TRANSITION

UPPER TRACE: VOUT A 0 TO +5V CHANGE LOWER TRACE: VOUTB (100mV/DIV) V<sub>DD</sub> = +12V, V<sub>REF</sub>H<sub>1</sub> = +5V, V<sub>REF</sub>L<sub>1</sub> = 0V, V<sub>SS</sub> = 0V, R<sub>L</sub> = 1MΩ, C<sub>L</sub> = 3.4pF CONDITIONS:

# CIRCUIT OPERATION

The DAC-8800 provides a programmable voltage output adjustment capability. Changing the programmed output voltage of each DAC is accomplished by clocking in an 11-bit serial data word into pin SDI (Serial Data Input). The format of this data word is three address bits, MSB first, followed by 8 data bits, MSB first. Table 2 provides the serial input decode table for data loading. DAC outputs can be changed one at a time in random sequence. The fast serial-data clocking of 6.6MHz makes it possible to load all 8 DACs in as little time as 14 microseconds. The exact timing requirements are provided in Figure 1.

A clear (CLR) input pin allows the circuit to be powered-up in the all zero state or a system reset pulse connected to CLR can asynchronously clear all data registers.

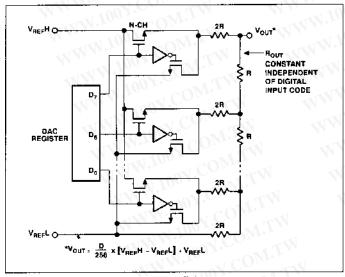

FIGURE 2: DAC-8800 TrimDACTM Equivalent DAC Circuit

The output voltage range is determined by the external input voltages applied to  $V_{\rm REF}H$  and  $V_{\rm REF}L$ . See Figure 2 for a simplified equivalent DAC circuit. If a negative supply is used on  $V_{\rm SS}$  then  $V_{\rm REF}L$  may be set negative resulting in a programmable bipolar output voltage swing.

The actual output voltage,  $V_{OUT}$ , depends on  $V_{REF}H$  and  $V_{REF}L$  as follows:

$$V_{OUT}(D) = D \times (V_{REF}H - V_{REF}L)/256 + V_{REF}L$$

where D is a whole number binary digital input word loaded into the DAC register. For example, when  $V_{\rm REF}H = +5V$  and  $V_{\rm REF}L = 0V$  unipolar output operation results with the following binary digital inputs:

| V <sub>out</sub> (D) | V <sub>REF</sub> H = +5.00V; V <sub>REF</sub> L = 0V  |

|----------------------|-------------------------------------------------------|

| 4.98V                | Full-Scale                                            |

| 2.50V                | Half-Scale                                            |

| 0.02V                | 1 LSB                                                 |

| 0.00V                | Zero-Scale also generated<br>When CLR Input Activated |

|                      | 4.98V<br>2.50V<br>0.02V                               |

Bipolar output operation is achieved when  $V_{REF}H = +2.5V$  and  $V_{REF}L = -2.5V$ , also note  $V_{SS}$  must be equal to or more negative than  $V_{REF}L$ .  $V_{SS} = -5V$  is a good choice for this example. The following example lists the actual bipolar output voltages produced by the binary digital input which would now be considered offset-binary coded:

| D   | D V <sub>OUT</sub> (D) V <sub>REF</sub> H = +2.50V; \ |                     |

|-----|-------------------------------------------------------|---------------------|

| 255 | 2.48V                                                 | Positive Full-Scale |

| 129 | 0,02V                                                 | Positive 1 LSB      |

| 128 | 0.00V                                                 | Bipolar Zero-Scale  |

| 127 | -0.02V Negative 1 LSB                                 |                     |

| 0   | -2.50V                                                | Negative Full-Scale |

REFERENCE INPUTS ( $V_{REF}H_1$ ,  $V_{REF}L_1$ ,  $V_{REF}H_2$ ,  $V_{REF}L_2$ ) The external voltages connected to the  $V_{REF}$  input pins determine the programmable output voltage ranges of the two sets of four DACs in the DAC-8800. Specifically,  $V_{REF}H_1$  and  $V_{REF}L_1$  are connected to DACs, A, B, C, D, and  $V_{REF}H_2$  and  $V_{REF}L_2$  are connected to DACs E, F, G, H.

Inspection of the DAC-8800 equivalent DAC circuit (Figure 2) shows the external  $V_{REF}H$  and  $V_{REF}L$  inputs connected to the internal DAC switches. During updating, the DAC switches produce transient current flowing from  $V_{REF}H$  to  $V_{REF}L$ . It is recommended to place  $0.01\mu F$  bypass capacitors across the  $V_{REF}H$  and  $V_{REF}L$  inputs to minimize the voltage transients.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

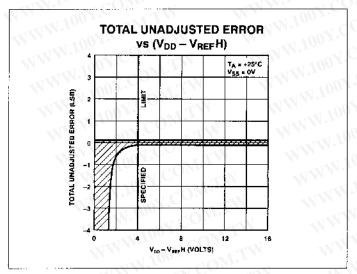

A wide range of external voltage references can be used subject to the reference input voltage range boundary conditions. First V<sub>REF</sub>H should always be more positive than V<sub>REF</sub>L. DC voltages are recommended.  $V_{\rm REF}L$  can be equal to the negative power supply  $V_{\rm SS}$ . This feature results in single supply operation when  $m V_{SS}$  is at ground.  $m V_{REF}H$  should not be closer than four volts to  $m V_{DD}$ . This is due to the DAC-8800 NMOS only DAC switches which will no longer operate properly if V<sub>REF</sub>H is closer to V<sub>DD</sub> than four volts. Total unadjusted error degrades when (VDD- $V_{\rm REF}H$ ) is less than four volts as shown in Figure 3.

FIGURE 3: Effect on TUE Operating Beyond  $(V_{OD} - V_{HEF}H) > 4V Limit$

# RECOMMENDED OPERATING POWER SUPPLY **VOLTAGE RANGES**

Although the DAC-8800 is thoroughly specified for operation with  $V_{DD} = +12V$  and  $V_{SS} = 0V$  or -5V, it will still function with the following recommended boundary conditions:

- $(V_{DD} V_{SS}) < 18V$

- $4.5V < V_{DD} < 16V$

- $0V > V_{SS} > -12V$

In all cases the reference voltage boundary conditions still apply. The boundary conditions described here make it possible to use DAC-8800 with a wide variety of readily available supply voltages. Some choices include, but are not limited to:

$$V_{np}/V_{ss} = +15V/0V; +12V/0V; +12V/-5V; +5V/-5V; +5V/-12V$$

DAC OUTPUTS (V<sub>OUT</sub> A, B, C, D, E, F, G, H)

The eight D/A converter voltage outputs have a constant output resistance independent of digital input code. The distribution of  $R_{OUT}$  from DAC to DAC within the DAC-8800 typically matches by 0.5%. Device to device  $R_{\rm OUT}$  matching is process-lot to process-lot dependent having a  $\pm 20\%$  variation. The change in ROUT with temperature is very small as a result of PMI's low temperature coefficient SiCr thin-film resistor process.

The nominal DAC output capacitance measures three picofarads and has little variation with temperature.

One aspect of the nominal 12.5k\O DAC output resistance is channel-to-channel crosstalk. Under a worst case condition of adjacent DAC outputs when DAC A makes a five volt output voltage change DAC B exhibits a 300mV voltage transient. See photograph in typical characteristics section of data sheet.

The channel-to-channel crosstalk is due to the 0.15pF inter-pin package capacitance. A FET probe with 3.4pF input capacitance was used to measure the DAC output channel-to-channel crosstalk characteristics shown. In voltage transient sensitive applications, minimization of crosstalk can be accomplished by placing ground traces between adjacent DAC output pins. DAC output bypass capacitors will also minimize voltage transients.

Output settling time has a dominant pole response as the photograph in the typical characteristics section shows. The output settling time characteristic consists of an 80 nanosecond propagation delay followed by a single RC decay waveform determined by the nominal  $R_{OUT}$  of 12.5k $\Omega$  times  $C_{OUT}$  plus  $C_{LOAD}$ which includes the oscilloscope probe.

The digital feedthrough from the serial data inputs (CLK, and SDI) to the DAC outputs measures less than 20mV.

#### DIGITAL INTERFACING

The DAC-8800 contains a standard three-wire serial input control interface. The three inputs are clock (CLK), load (LD), and serial data input (SDI). A CLK input pin is available for negative edge triggered data loading. The edge sensitive clock input pin requires clean transitions to avoid clocking incorrect data into the serial input register. Standard logic families work well. If mechanical switches are used for product evaluation they should be debounced by a flip-flop or other suitable means.

The logic control input truth table (Table 3) defines operation of the serial data input register.

The CLK input is used to place data in the serial data input register. The unused clock input (CLK or CLK) should be tied to the active state (CLK = 1 or  $\overline{CLK}$  = 0 for active). The load strobe ( $\overline{LD}$ ) which must follow the eleventh active CLK edge transfers the

特力材料886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

FIGURE 4: Three-Wire Serial Interface Connections

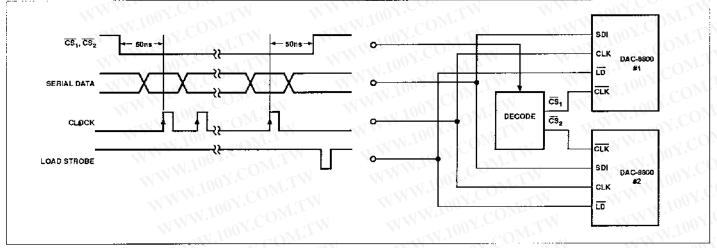

FIGURE 5a: Decoding Multiple DAC-8800s

data from the serial data input register to the DAC register decoded from the first three address bits clocked into the input register. Any extra CLK edges after the eleventh edge looses the first bits shifted in. See Table 2 for a complete description. See Figure 4 for an example using the CLK input pin to clock data into the SDI.

The unused clock input of Figure 4 can be used to provide a chip select  $(\overline{CS})$  feature for applications using more than one DAC-8800. Figure 5a shows the proper connection and timing of the CLK inputs which assures that the  $\overline{CLK}$  acting as a chip select  $(\overline{CS})$  is taken to the active low state selecting the desired DAC-8800.

**DAC8800**

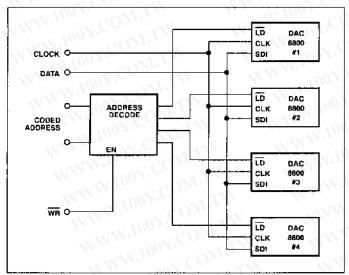

Another method of decoding multiple DAC-8800s is shown in Figure 5b. Here all the DAC serial input registers receive the same input data; however, only one of DAC's  $\overline{\text{LD}}$  input is activated to transfer its serial input register contents into the destination DAC register. In this circuit the  $\overline{\text{LD}}$  timing generated by the address decoder should follow the DAC-8800 standard timing requirements. Note the address decoder should not be activated by its WR input while the coded address inputs are changing.

FIGURE 5b: Decoding Multiple DAC-8800s Using the LD Input Pin

# **APPLICATIONS**

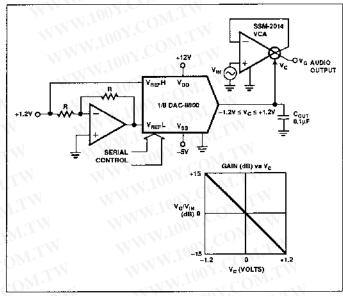

# DIGITALLY PROGRAMMABLE AUDIO AMPLIFIER

The DAC-8800 is well suited to digitally control the gain or attenuation settings of eight voltage controlled amplifiers (VCAs). In professional audio mixing consoles, music synthesizers and other audio processor's VCAs, such as the SSM-2014, adjust audio channel gain and attenuation from front panel potentiometers. The VCA provides a clean gain transition control of audio level when the slew rate of the analog input control voltage (V $_{\rm C}$ ) is properly chosen. Taking advantage of the 12.5k $\Omega$  nominal output resistance of the DAC-8800 it is very easy to control the slew rate of V $_{\rm OUT}$  by appropriate selection of C $_{\rm OUT}$  Figure 6 shows one channel of a digitally programmable audio amplifier.

The reference high (V<sub>REF</sub>H) and reference low (V<sub>REF</sub>L) input voltages of the DAC-8800 provide a digitally programmable output voltage of –1.2V to +1.2V which is connected to the control voltage (V<sub>C</sub>) input terminal of the SSM-2014 VCA. The gain of the SSM-2014 is guaranteed to change from –15dB to + 15dB for 1.2 to –1.2V input V<sub>C</sub> voltage. A C<sub>OUT</sub> of 0.1µF provides a control voltage transition time of 1.2ms which generates a click free change in audio channel gain.

FIGURE 6: Digitally Programmable Amplifier

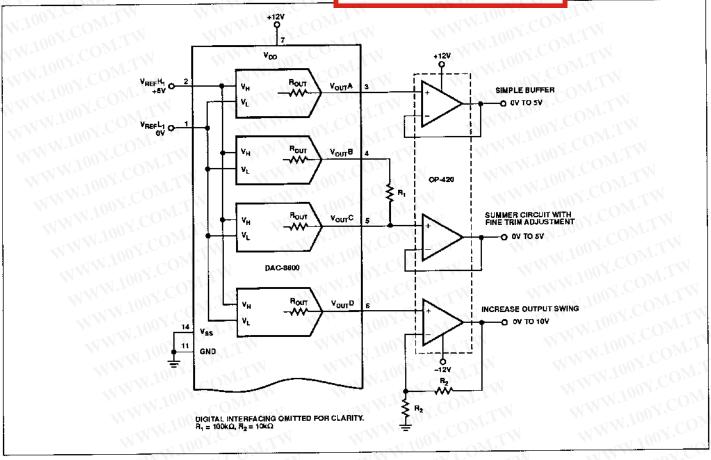

# **BUFFERING THE DAC-8800 OUTPUT**

External op amps can be used to buffer the output of the DAC-8800's nominal  $12.5 \mathrm{k}\Omega$  output resistance. In Figure 7 a variety of possibilities are shown. The quad low power OP-420 is used as a simple buffer to reduce the output resistance of DAC A. The OP-420 was chosen for its wide operating supply range, both single and dual, low power consumption, and low cost.

The next two DACs, B and C, are configured in a summing arrangement where DAC C provides the course output voltage setting and DAC B can be used for fine adjustment. The insertion of R<sub>1</sub> in series with DAC B attenuates its contribution to the voltage sum node at the DAC C output.

DAC D in Figure 7 is in a noninverting gain of two configuration increasing the available output swing to 10V. Appropriate choice of external op amp gain can achieve output voltage swings beyond the range of the DAC-8800 if the external op amp power supply voltages are sufficiently high. In addition, the op amp feedback network termination could be a bias voltage which would provide an offset to the output signal swing.

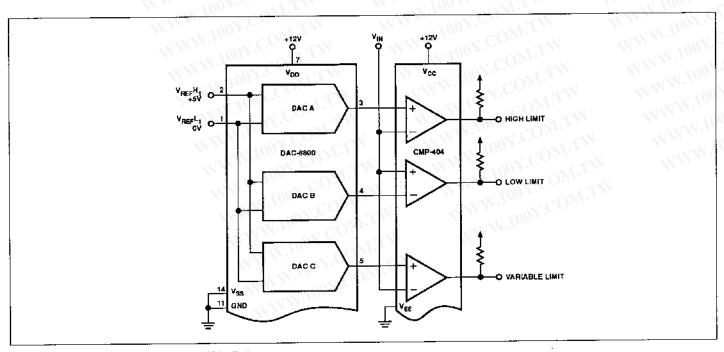

### SETTING COMPARATOR TRIP POINTS

The DAC-8800 is ideal to provide setpoints for voltage input comparators. In Figure 8 the very low power CMP-404 detects whether input voltage (V<sub>iN</sub>) is higher or lower than the programmed limit values providing TTL compatible output signals. The compactness of the DAC-8800 makes it ideal for high density testing applications found in pin head electronics.

FIGURE 7: Buffering the DAC-8800 Output

FIGURE 8: Setting the Comparator Trip Points

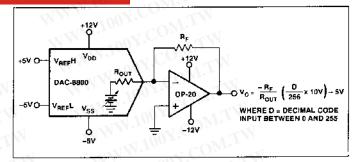

### CURRENT SUMMING OUTPUT OPERATIONS

Since the DAC-8800 has a constant output resistance regardless of digital input code, it can be used in a current summing application. Figure 9 depicts the DAC output connected to the inverting input of an OP-20 low power consumption op amp. An external feedback resistor sets the output signal swing according to the formula given. The gain accuracy of this circuit has a wide variation due to the 30% output tolerance of the DAC-8800 R<sub>OUT</sub> specification. A second DAC in the DAC-8800 could be used with an external resistor summed into the OP-20 current summing node to digitally adjust the full-scale swing.

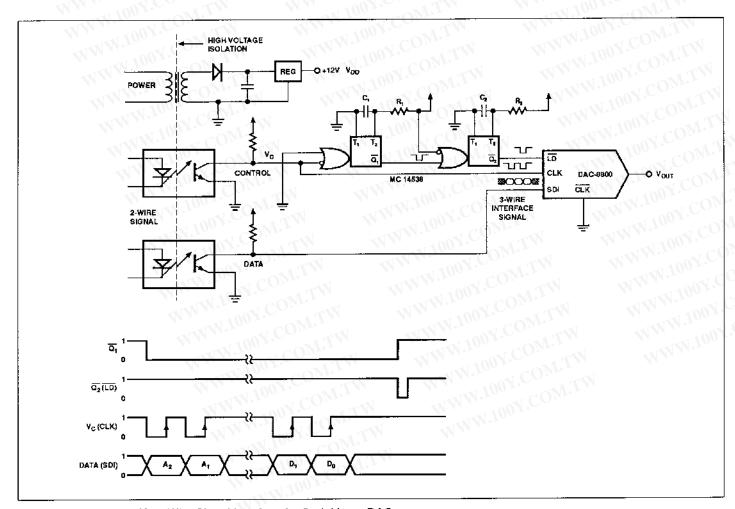

# **OPTICALLY ISOLATED TWO-WIRE INTERFACE**

Two-wire signal interfacing is often found in process control applications where electrical isolation of hazardous environments and minimization of wiring is necessary. Isolation transformers or optocouplers provide the high voltage isolation. Normally the DAC-8800 requires a three-wire interface to update the DAC contents. One technique which translates a two-wire interface into the three-wire signal control required by the

FIGURE 9: Current Summing Output Operation

DAC-8800 is shown in Figure 10. A single package CMOS-logic dual-retriggerable one-shot MC14538 provides the solution. At rest the optocouplers are both OFF allowing the pull-up resistors to sit at logic high. No undefined transients should occur on the control input line  $\rm V_C$  to avoid inadvertently clocking incorrect data into the DAC-8800 serial input register. When it is time to update one of the DAC-8800 DACs, the CONTROL line will go

FIGURE 10: Isolated Two-Wire Signal Interface for Serial Input DAC

low, triggering the first one-shot  $(\overline{Q}_1)$ . At this time valid data should also be applied to the DATA input optocoupler. Sufficient time must be allowed before the control (V<sub>C</sub>) input returns to logic high to make sure the DAC-8800 input data is stabilized. When V<sub>C</sub> changes to logic high, the first DATA bit shifts into the DAC-8800 serial data input register. The time constant of the first one-shot established by R, and C, should be at least twice as long as the basic CONTROL input clock period. This will prevent the  $\overline{\mathbf{Q}}_i$  output from returning to the high state. The next control input negative edge retriggers the first one-shot and sets up the DAC-8800 clock for the next DATA bit. All eleven positive clock edges will fill the DAC-8800 serial input register and each negative clock edge will retrigger the first one shot. As soon as the CONTROL line returns to the passive state, the first one shot will time out, triggering the second one shot  $(\overline{\mathbb{Q}}_2)$ , which will produce the required load LD pulse for the DAC-8800 to transfer its serial input register contents to the internal DAC register completing the DAC update. The R<sub>1</sub>C<sub>1</sub> and R<sub>2</sub>C<sub>2</sub> times need to be designed based on the system's CONTROL-input clock rate. The optocoupler clocking rate must also be considered in setting the system clock rate.

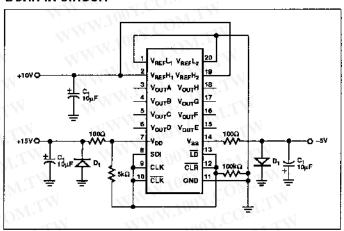

# **BURN-IN CIRCUIT**

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

-14-

REV. A