勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

GM16C550

ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFOs

#### Version 1.0

#### Descriptions

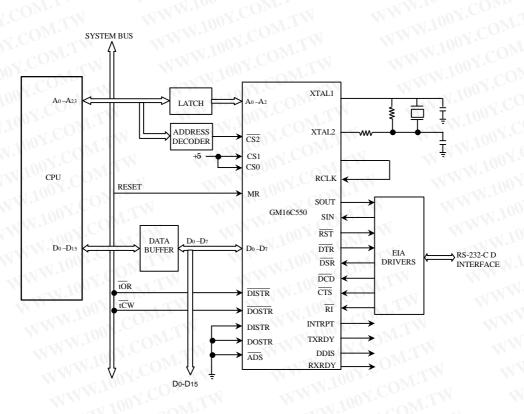

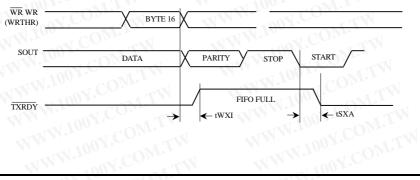

The GM16C550 is an asynchronous communications element (ACE) that is functionally equivalent to the GM16C450, and addition-ally incorporates a 16byte FIFOs are available on both the transmitter and receiver, and can be activated by placing the device in the FIFO mode. After a reset, the registers of the GM16C550 are identical to those of the GM16C450.

The UART performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to- serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (parity, overrun, framing, or break interrupt).

#### Features

- Compatible to the Industry Standard 16C550

- Modem control signals include CTS, RTS, DSR DTR, RI and DCD

- Programmable serial characteristics :

- 5-, 6-, 7- or 8-bit characters

- Even-, odd-, or no-parity bit generation and detection

- 1-, 11/2- or 2-stop bit generation

- Baud rate generation (DC to 256K baud)

- 16 byte FIFO reduces CPU interrupts.

- Independent control of transmit, receive, line status, data set interrupts, FIFOs.

- Full status reporting capabilities

- Three-state, TTL drive capabilities for bi-directional data bus and control bus.

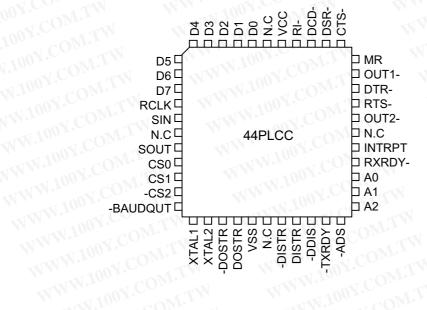

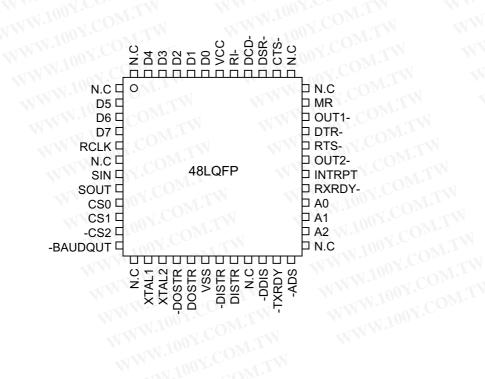

- 40DIP/44PLCC/48LQFP

#### **Device Code Name**

| Part Number | Voltage | PKG     |

|-------------|---------|---------|

| GM16C550    | COMIT   | 40 DIP  |

| GM16C550-44 | 5V      | 44 PLCC |

| GM16C550-48 | 3.3V    | 48 LQFP |

**Pin Configuration**

|       |          |       | ↓ vcc  |

|-------|----------|-------|--------|

| ,001. | D1 4     |       | P RI-  |

|       | D2 🗆     |       | DCD-   |

|       | D3 🗆     |       | DSR-   |

|       | D4 🗆     |       | CTS-   |

|       | D5 🗆     |       |        |

|       | D6 🗆     |       | DUT1-  |

|       | D7 🗆     |       | DTR-   |

|       |          |       | P RTS- |

|       | SIN 🗆    |       | DUT2-  |

|       | SOUT D   | 40DIP | INTRPT |

|       | CS0 🗆    |       | RXRDY- |

|       | CS1 🗖    |       | D A0   |

|       | -CS2 🗆   |       | □ A1   |

|       | -BAUDQUT |       | □ A2   |

|       | XTAL1 🗆  |       | D ADS- |

|       | XTAL2    |       | TXRDY- |

|       | -DOSTR 🗆 |       | DDIS-  |

|       | DOSTR 🗆  |       |        |

|       | VSS 🗆    |       | DISTR- |

|       |          |       |        |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

GM16C550

# Pin Configuration - continue

WWW.100Y.COM.TW

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### Absolute Maximum Ratings

| Temperature under Bias                           | 0℃ to 70℃       |

|--------------------------------------------------|-----------------|

| Storage Temperature                              | - 65 ℃ to 150 ℃ |

| All Input or Output Voltages with respect to Vss | - 0.5V to 7.0V  |

| Power Dissipation                                | 500mW           |

#### Note :

Maximum ratings indicates limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics

#### **DC Electrical Characteristics**

$T_{A}$  = 0 °C ~ 70 °C, Vcc = 5V  $\pm$  5% & 3.3V  $\pm$  5%, Vss = 0V unless otherwise specified

| Cumbal               | Doromotor                             | 3.3V                          |       | 5V             |      | Units |                                  |

|----------------------|---------------------------------------|-------------------------------|-------|----------------|------|-------|----------------------------------|

| Symbol               | Parameter                             | Min                           | Max   | Min            | Max  | Units | Conditions                       |

| V <sub>ILX</sub> C   | Clock Input Low Voltage               | -0.3                          | 0.8   | -0.5           | 0.8  | V     | 100Y.COM.TW                      |

| V <sub>IHX</sub>     | Clock Input High Voltage              | 1.6                           | Vcc   | 2.0            | Vcc  | V     | 100Y.COM.TW                      |

| V <sub>IL</sub>      | Input Low Voltage                     | w Voltage -0.3 0.8 -0.5 0.8 V |       | N. 100Y.COM.TW |      |       |                                  |

| V <sub>IH</sub>      | Input High Voltage                    | 2.0                           | Vcc   | 2.2            | Vcc  | V     | WILLON.COM.TW                    |

| NN.10                | Quitaut Law Valtage                   | WW. 100Y.CC                   |       | 0.4            |      |       | I <sub>OL</sub> = 1.6mA          |

| V <sub>OL</sub>      | Output Low Voltage                    | WW.                           | 0.4   | WILM           |      | V     | I <sub>OL</sub> =mA              |

| WWW.                 | Output High Voltage                   |                               | 100Y. | 2.4            | 2.4  |       | $I_{OH} = -1.0 mA$               |

| V <sub>OH</sub>      |                                       |                               | 1005  | .Com.TW        |      |       | I <sub>OH</sub> =mA              |

| / <sub>CC</sub> (AV) | Average Power Supply<br>Current (Vcc) | K K                           | 4.5   | Y.CUM          | 10   | mA    | Vcc = 5.25V or 3.5V              |

|                      | Input Leakage                         | N.                            | ±10   | N.C            | ±10  | uA    | Vcc = 5.25V  or  3.5V,           |

| I <sub>CL</sub>      | Clock Leakage                         | V                             | ±10   | 100Y.C         | ±10  | uA    | Vss = 0V<br>Vin = 0V, 3.5V/5.25V |

| I <sub>oz</sub> <    | 3-state Leakage                       |                               | ±20   | 1001           | ±20  | uA    | Vout = 0V, 3.5V/5.25V            |

| V <sub>ILMR</sub>    | MR Schmitt V <sub>IL</sub>            |                               | 0.8   | 100            | 0.8  | V     | WWW.100Y                         |

| V <sub>IHMR</sub>    | MR Schmitt V <sub>IH</sub>            | 2.0                           | WW    | 2.2            | N.CO | V     | WW 100                           |

#### **Capacitance** $T_A = 25^{\circ}C$ Vcc = Vss = 0V

| Capacitan | <b>ce</b> T <sub>A</sub> = 25°C Vcc = Vss = 0V | N N   | MWN. | 1.100Y.C | COM.TY | WWWW.100        |

|-----------|------------------------------------------------|-------|------|----------|--------|-----------------|

| Symbol    | Parameter                                      | Min   | Тур  | Max      | Units  | Conditions      |

| CXIN      | Clock Input Capacitance                        | TW    | 15   | 20       | pF     | Fc = 1MHz       |

| CXOUT     | Clock Output Capacitance                       | I.T.W | 20   | 30       | рF     | Unmeasured pins |

| CIN       | Input Capacitance                              | M.T.W | 6    | 10       | рF     | Returned to Vss |

| COUT      | Output Capacitance                             |       | 10   | 20       | pF     |                 |

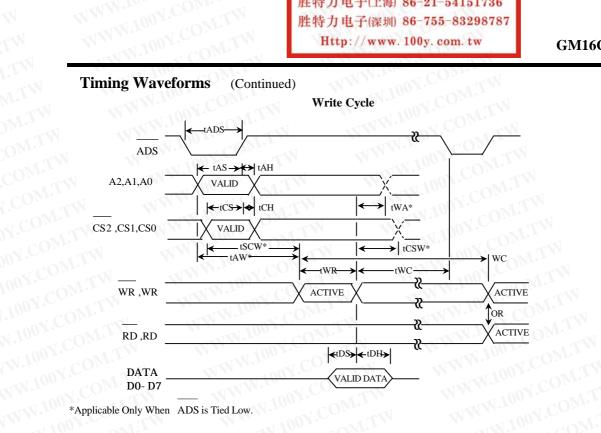

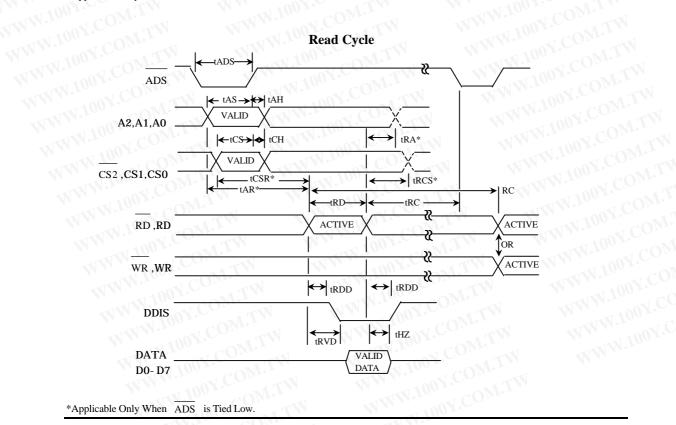

| Symbol | Parameter                                       | Min   | Max               | Units | Conditions                     |

|--------|-------------------------------------------------|-------|-------------------|-------|--------------------------------|

| ADS    | Address Srobe Width                             | 60    |                   | ns    | WT.                            |

| AH     | Address Hold Time                               | 0     | N.P               | ns    | Dur.                           |

| AR     | RD, RD Delay from Address                       | 30    |                   | ns    | Note 1                         |

| AS     | Address Setup Time                              | 60    |                   | ns    | TIM                            |

| AW     | WR, WR Delay from Select                        | 30    | N/V               | ns    | Note 1                         |

| СН     | Chip Select Hold Time                           | 0     | Vin               | ns    | CONL                           |

| CS     | Chip Select Setup time                          | 60    | N.                | ns    | I. M.I.W                       |

| CSR    | RD, RD Delay from Chip Select                   | 30    | NN                | ns    | Note 1                         |

| CSW    | WR, WR Delay from Select                        | 30    |                   | ns    | Note 1                         |

| DH     | Data Hold Time                                  | 30    | NA .              | ns    | Mr. CONLI                      |

| DS     | Date Setup Time                                 | 30    | Z                 | ns    | INDY. CONTRACT                 |

| HZ     | RD, RD to Floating Data Delay                   | 0     | 100               | ns    | 100 pF loading, Note 3         |

| MR     | Master Reset Pulse Width                        | 5     |                   | ns    | 1.100 COMPT                    |

| RA     | Address Hold Time from $\overline{RD}$ , RD     | 20    |                   | ns    | Note 1                         |

| RC     | Read Cycle Delay                                | 125   |                   | ns    | W. ON COM                      |

| RCS    | Chip Select Hold Time from RD, RD               | 20    | T                 | ns    | Note 1                         |

| RD     | RD, RD Strobe Width                             | 125   |                   | ns    | 1001. ONIT                     |

| RDD    | RD, RD to Driver Enable/Disable                 | Jon T | 60                | ns    | 100 pF loading, Note 3         |

| RVD    | Delay from - RD, RD to Data                     | CON., | 125               | ns    | 100 pF loading,                |

| WA     | Address Hold Time from WR, WR                   | 20    | T.A.              | ns    | Note 1                         |

| WC     | Write Cycle Delay                               | 150   | WT                | ns    | WW 100Y.C.                     |

| WCA    | Chip Select Hold Time from $\overline{WR}$ , WR | 20    |                   | ns    | Note 1                         |

| WR     | WR, WR Strobe Width                             | 100   | $V_{-1}$          | ns    | W.100 COM                      |

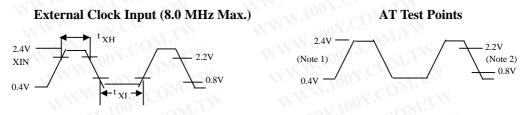

| XH     | Duration of clock High Pulse                    | 55    | T                 | ns    | External Clock (8.0 MHz Max.)  |

| XL     | Duration of clock Low Pulse                     | 55    |                   | ns    | Exrternal Clock (8.9 MHz Max.) |

| RC 100 | Read Cycle= ${}^{t}AR + {}^{t}RD + {}^{t}RC$    | 280   | 0 <sub>N' 1</sub> | ns    | Note 4                         |

| VC     | Write Cycle= ${}^{t}AW + {}^{t}WR + {}^{t}WC$   | 280   | M                 | ns    | W 1001.                        |

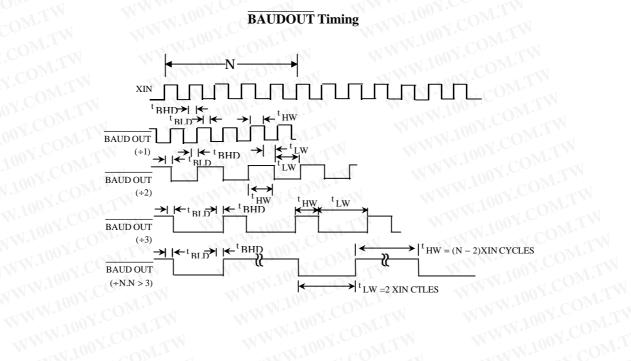

## Baud Generator

WWW.100Y.COM.TW

WWW.100Y.CO

MM<u>M.</u>

ADDY.COM.TW

WWW.100Y.COM.TW

ITT

WW.100Y.COM.TW

COM.TW

WOY.COM 100X.CON

.100X.CO

VWW.100

COM.TW

| N                | Baud Divisor                    | 1   | 2 <sup>16</sup> -1 |    | NO01 NN                             |

|------------------|---------------------------------|-----|--------------------|----|-------------------------------------|

| <sup>t</sup> BHD | Baud Output Positive Edge Delay | WW. | 175                | ns | 100 pF load                         |

| <sup>t</sup> BLD | Baud Output Negative Edge Delay |     | 175                | ns | 100 pF load                         |

| <sup>t</sup> HW  | Baud Output Up Time             | 75  | 100Y               | ns | $f_{X} = 8.0 MHz$ , +2, 100 pF load |

| <sup>t</sup> LW  | Baud Output Down Time           | 100 | 1.10-              | ns | $f_{X} = 8.0 MHz$ , +2, 100 pF load |

4

WW

WWW.100Y.COM.TW

#### **AC Characteristics** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V/3.3V$

| Min | Max  | Units    | Conditions     |

|-----|------|----------|----------------|

| 1   | viin | viin Max | viin Max Units |

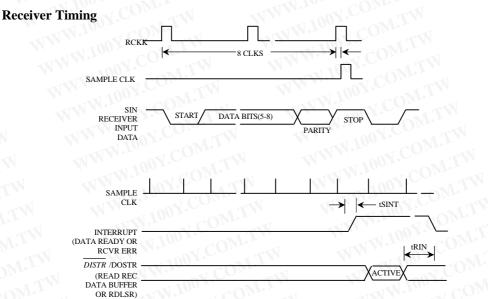

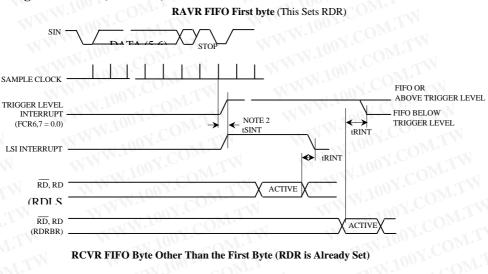

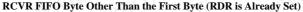

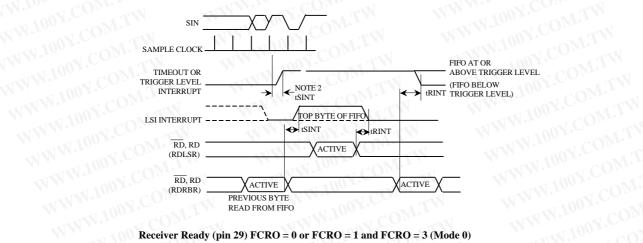

#### Receiver

| Receiver          |                                                            |       |                |             |

|-------------------|------------------------------------------------------------|-------|----------------|-------------|

| <sup>t</sup> RINT | Delay from RD, RD (RD RBR/ or<br>RD LSR) to Reset Interupt | 1/1/1 | μs             | 100 pF load |

| <sup>t</sup> SCD  | Delay from RCLK to Sample Time                             | 2     | μs             | WT          |

| <sup>t</sup> SINT | Delay from Stop to Set Interrupt                           | 1     | RCLK<br>Cycles | Note 2      |

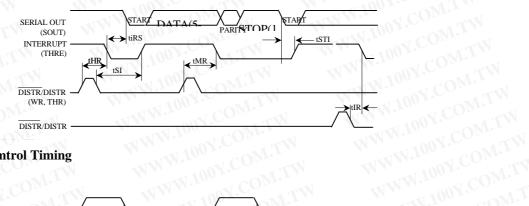

#### Transmitter

| <sup>t</sup> HR  | Delay from WR, WR (WR THR)<br>To Reset Interrupt        |      | 175 | ns                                     | 100 pF load      |

|------------------|---------------------------------------------------------|------|-----|----------------------------------------|------------------|

| <sup>t</sup> IR  | Delay from RD, RD (RD IIR)<br>To Reset Interrupt (THRE) |      | 250 | ns                                     | 100 pF load      |

| <sup>t</sup> IRS | Delay from Initial INTR Reset<br>To Transmit Start      | 8    | 24  | Baudout<br>Cycles                      | OUX.COM.IW       |

| <sup>t</sup> SI  |                                                         |      | 24  | Baudout<br>Cycles<br>Baudout<br>Cycles | Note 5<br>Note 5 |

| <sup>t</sup> STI |                                                         |      | 8   |                                        |                  |

| <sup>t</sup> SXV | Delay from Start to TXRDY Active                        | OW.T | 8   | Baudout<br>Cycles                      | 100 pF load      |

| <sup>t</sup> WXI | Delay from Write to TXRDY inactive                      | ON.  | 195 | ns                                     | 100 pF load      |

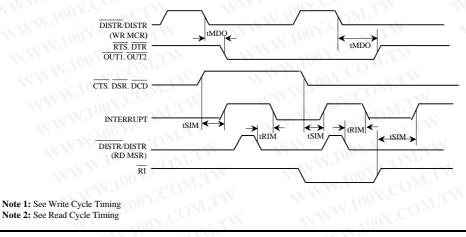

#### Modem Control

| <sup>t</sup> MDO<br><sup>t</sup> RIM | Delay from         WR, WR         (WR MCR) to Output           Delay to Reset Interrupt from         RD, RD         (RD MSR) | CON  | 200<br>250 | ns<br>N ns | 100 pF load<br>100 pF load |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------------|------------|----------------------------|

| <sup>t</sup> SIM                     | Delay to Set Interrupt from MODEM Input                                                                                      | 4.CU | 250        | ns         | 100 pF load                |

#### Notes

- 1. Applicable only when ADS is tied low.

- 2. In the FIFO mode (FCRO=1) the trigger level interrupts, the receiver data available indication, the active RXRDY indica-tion and the overrun error indication will be delayed 3 RCLKs. Status indicators (PE, FE, BI) will be delayed 3 RCLKs after the first byte has been received. For subsequently received bytes these indicators will be updated immediately after RDRBR goes inactive. Timeout interrupt is delayed 8 RCLKs.

- 3. Change and discharge time is determined by VOL, VOH and the external loading.

- 4.In FIFO mode RC=425 ns (minimum) between reads of the receiver FIFO and the status registers (interrupt identification register or line status register).

- 5. This delay will be lengthened by 1 character time, minus the last stop bit time if the transmitter interrupt delay circuit is active (See FIFO Interrupt Mode Operatione)

**Timing Waveforms** (All timings are referenced to valid 0 and valid)

N.COM.TW **Note 2:** The 2.2V and 0.8V levels are the voltages at which the timing tests are made. Note 1: The 2.4V and 0.4V levels are the voltages that the inputs are driven to during AC testing.

WW

NWW.100Y.COM.TW

WWW.100Y.CC

ONY.COM.TW

WWW.100Y.COM.TV

WWW.100Y.COM.TW

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

GM16C550

\*Applicable Only When ADS is Tied Low. WWW.1007

<sup>\*</sup>Applicable Only When  $\overline{\text{ADS}}$  is Tied Low.

WWW.100X.COM.TV

WW

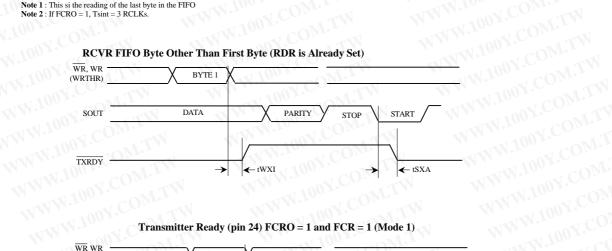

WW.100Y.COM.T **Transmitter Timing**

**MODEM Comtrol Timing**

Note 2: See Read Cycle Timing

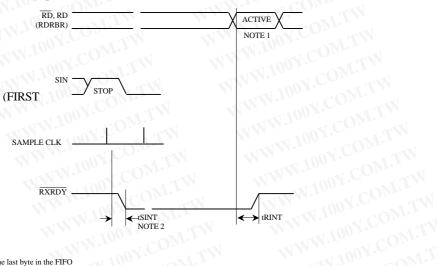

Note 1: This is the reading of the last byte in the FIFO Note 2: If FCRO =1, then Tsint = 3 RCLKs. For a timeout tSINT = 0 RCLKs.

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

GM16C550

#### Timing waveforms (Continued)

Receiver Ready (pin 29) FCRO = 0 or FCRO = 1 and FCRO = 1 (Mode 1)

WW.100Y.COM.TW Note 1 : This si the reading of the last byte in the FIFO Note 2 : If FCRO = 1, Tsint = 3 RCLKs

WWW.100Y.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

GM16C550

#### **Pin Descriptions**

The following describes the function of all UART pins. Some of these descriptions reference internal circuits. In the following descriptions, a low represents a logic 0 (0V

nominal) and a high represents a logic 1 (+2.4V nominal).

#### INPUT SIGNALS

**Chip Select (CS0, CS1, \overline{CS2}) Pins 12-14**: When CS0 and CS1 are high and  $\overline{CS2}$  is low, the chip is selected. This enable communication between the UART and the CPU. The positive edge of an active Address Strobe signal latches the decoded chip select signals, completing chip selection. If  $\overline{ADS}$  is always low, valid chip selects should stabilize according to the CSW parameter.

**Read (RD,**  $\overline{RD}$ ), **Pins 22 and 21**: When Rd is high or RD is low while the chip selected, the CPR can read status information or data from the selected UART <u>regi</u>ster.

**Note:** Only an active RD or  $\overline{RD}$  input is required to transfer data from the UART during a read operation. Therefore tie either the RD input permanently low or the RD input permanently high, when it is not used.

Write (WR,  $\overline{WR}$ ), Pin 19 and 18: When WR is high or  $\overline{WR}$  is low while the chip selected, the CPU can write control words or data into the selected UART register.

Note: Only an active WR or  $\overline{WR}$  input is required to transfer data to the UART during a write operation. Therefore, tie either the WR input permanently low or the  $\overline{WR}$  input permanently high, when it is not used.

Address Strobe ( $\overline{\text{ADS}}$ ), Pin 25: The positive edge of an active Address Strobe ( $\overline{\text{ADS}}$ ) signal latches the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals.

**Note:** An active ADS input is required when the Register Select (A0, A1, A2) signals are not stable for the duration of a read or a write operation. If not required, tie the ADS input permanently low.

**Register Select (A0, A1, A2), Pins 26-28**: Address signals connected to these 3 inputs select a UART register for the CPU to read from or write to during data transfer. A table of registers and addresses is shown below. Note that the state of the Divisor Latch Access Bit (DLAB), which is the most significant bit of the Line Control Register, affects the selection of certain UART registers. The DLAB must be set high by the system software to access the Baud Generator Divisor Latches.

**Master Reset (MR), Pin 35:** When this input is high it clears all the registers (except the Receiver Buffer, Transmitter Holding, and Divisor Latches), and the control logic of the <u>UART</u>. The state of various output signals (SOUT, INTR,  $\overline{OUT1}$ ,  $\overline{OUT2}$ ,  $\overline{RTS}$ , DTR) are affected by an active MR input (Refer to Table 1). This input is buffered with a TTLcompatible Schmitt Trigger with 0.5V typical hysteresis.

**Receiver Clock (RCLK), Pin 9**: This input is the 16 X baud rate clock for the receiver section of the chip.

**Ring Indicator (RI), Pin 39:** When low, this indicates that a telephone ringing signal is received by the MODEM or data set. The RI signal is a MODEM status input

#### **Register Address**

| DLAB | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Register                        |

|------|----------------|----------------|----------------|---------------------------------|

| 0    | 0              | 0              | 0              | Receiver Buffer (read)          |

| NN.  |                | J C            | 174-           | Transmitter Holding             |

|      |                |                | A              | Register (Write)                |

| 0    | 0              | - 0            | 1              | Interrupt Enable                |

| ×    | 0              | 1              | 0              | Interrupt Identification (read) |

| ×    | 0              | 17             | 0              | FIFO Control (Write)            |

| ×    | 0              | 1              | 1              | Line Control                    |

| ×    | 1              | 0              | 0              | MODEM Control                   |

| ×    | 1              | 0              | 1              | Line Status                     |

| ×    | 1              | 1              | 0              | MODEM Status                    |

| ×    | 1              | 1              | 1              | Scratch                         |

| 1    | 0              | 0              | 0              | Divisor Latch                   |

| 0    |                | 110            | 0 .            | (least significant byte)        |

| 1    | 0              | 0              | 11             | Divisor Latch                   |

|      |                |                | 00 -           | (most significant byte)         |

Serial Input (SIN), Pin 10: Serial data input from the communications link (peripheral device, MODEM, or data set).

**Clear to Send (** $\overline{\text{CTS}}$ **), Pin 36**: When low, this indicates that the MODEM or data set is ready to exchange data. The  $\overline{\text{CTS}}$ signal is a MODEM status input whose conditions can be tested by the CPU reading bit 4 (CTS) of the MODEM Status Register. Bit 4 is the complement of the  $\overline{\text{CTS}}$  signal. Bit 0 (DCTS) of the MODEM Status Register indicates whether the  $\overline{\text{CTS}}$  input has changed state since the previous reading of the MODEM Status Register.  $\overline{\text{CTS}}$  has no effect on the Transmitter.

Note: Whenever the CTS bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

Data Set Ready (  $\overline{DSR}$  ), Pin 37: When low, this indicates that the MODEM or data set is ready to establish the communications link with the UART. The  $\overline{DSR}$  signal is a MODEM status input whose condition can be tested by the CPU reading bit 5 (DSR) of the MODEM Status Register. Bit 5 is the complement of the  $\overline{DSR}$  signal. Bit 1 (DDSR) of the MODEM Status Register indicates whether the  $\overline{DSR}$  input has changed state since the previous reading of the MODEM Status Register.

Note: Whenever the DSR bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status interrupt is enabled.

**Data Carrier Detect** ( $\overrightarrow{DCD}$ ), **Pin 38**: When low, indicates that the data carrier has been detected by the MODEM or data set. The  $\overrightarrow{DCD}$  signal is a MODEM status input whose condition can be tested by the Register. Bit 7 is the complement of the  $\overrightarrow{DCD}$  signal. Bit 3 ( $\overrightarrow{DDCD}$ ) of the MODEM Status Register indicates whether the  $\overrightarrow{DCD}$  input has changed state since the previous reading of the MODEM Status Register.  $\overrightarrow{DCD}$  has no effect on the receiver.

Note: Whenever the DCD bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

whose condition can be tested by the CPU reading bit 6 (RI) of the MODEM Status Register. Bit 6is the complement of the RI signal. Bit 2 (TERI) of the MODEM

Status Register indicates whether the RI input signal has changed from a low to a high state since the previous reading of the MODEM Status Register

Note: Whenever the RI bit of the MODEM Status Register changes from a high to a low state, an interrupt is generated if the MODEM Status Interrupt is enabled.

Vcc, Pin 40 : +5V supply. Vss, Pin 20 : Ground(0V) reference.

#### OUTPUT SIGNALS

**Data Terminal Ready (DTR), Pin 33:** When low, this informs the MODEM or data set that th<u>e UART</u> is ready to establish communications link. The DTR output signal can be set to an active low by programming bit 0 (DTR) of the MODEM Control Register to high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.

**Request to Send (RTS), Pin 32:** When low, this informs the MODEM and data set that the UART is ready to exchange data. The RTS output signal can be set to an active low by programming bit 1 (RTS) of the MODEM Control Register. A Master Reset operation sets this signal to its inactive state. Loop node operation holds this signal in its inactive state.

**Output 1** ( $\overline{\text{OUT1}}$ ), Pin 34: This user-designed out-put can be set to an active low by programming bit 2 (OUT1) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive state. Loop Mode operation holds this signal to its inactive state.

**Output 2 (OUT2), Pin 31:** This user-designated output can be set to an active low by programming bit 3 (OUT2) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal to its inactive state.

**TXRDY, RXRDY, Pin 24, 29:** Transmitter and Receiver DMA signaling is available through two pins (24 and 29). When operating in the FIFO mode, one of two types DMA signaling per pin can be selected via FCR3, When operating as in the GM16C16450 Mode., only DMA Mode 0 is allowed. Mode 0 supports single transfer DMA where a transfer is made between CPU bus cycles. Mode 1 supports multi-transfer DMA where multiple transfers ard made continuously until the RCVR FIFO has been emptied or the XMIT FIFO has been filled.

**RXRDY Mode 0:** When in the GM16C450 Mode (FCR0 = 0) or in the FIFO Mode (FCRO = 1, RCR3 = 0) and there is at least 1 character in the RCVR FIFO of RCVR holding register, the RXRDY pin (29) will be low active. Once it is activated the RXRCY pin will go inactive when there are no more characters in the FIFO of holding register.

**RXRDY Mode 1:** In the FIFO Mode (FCR0 = 1) when the FRC3 = 1 and the trigger level or the timeout has been reached, the RXRDY pin will go low active. Once it is activated it will go inactive when there are no more characters in the FIFO or holding register.

**TXRDY Mode 0:** in the GM16C450 Mode (FCR0 = 0) or in the FIFO Mode (FCR = 1, FCR3 = 0) and there are no characters in the XMIT FIFO or XMIT hold register, the TXRDY pin(24) will be low active. Once it is activated the TXRDY pin will go inactive after the first character is loaded into the XMIT FIFO or holding register.

**TXRDY Mode 1**: In the FIFO Mode (FCR0 = 1) when FCR3 = 1 and there is at least one unfilled position in the XMIT FIFO, it will go low active. This pin will become inactive when the XMIT FIFO is completely full.

**Driver Disable (DDIS), Pin 23:** this goes low whenever the CPU is reading data from the UART. It can disable or control the direction of a data bus transceiver between the CPU and the UART.

**Baud Out (BAUDOUT), Pin 23:** This is the 16X clock signal from the transmitter section of the UART. The clock rate is equal to the main reference oscillator frequency divided by the specified divisor in the Baud Generator Divisor Latches. The BAUDOUT may also be used for the receiver section by tying this output to the RCLK input of the chip.

Interrupt (INTR), Pin 30: This pin goes high when-ever any one of the following interrupt types has an active high cognition and is enabled via the IER; Receiver Error Flag; Received Data Avail-able; timeout (FIFO Mode only); Transmitter Holding Register Empty; and MODEM Status, The INTR signal is reset low upon the appropriate interrupt service or a Master Reset operation.

Serial output (SOUT), Pin 11: Composite serial data output to the communications link (peripheral. MODEM or data set). The SOUT signal is set to the Marking (logic 1) state upon a Master Reset operation.

#### **INPUT / OUTPUT SIGNALS**

**Data (D7-D0) Bus, Pin 1-8:** This bus comprises eight TRI-state input/output lines. The bus provides bidirectional communications between the UART and the CPU, Data, control words. And status information are transferred via the D7-D0 Data Bus.

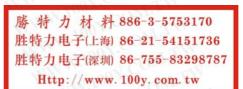

**External Clock Input/Output (XIN, XOUT), Pins 16 and 17:** These two pins connect the main timing reference (crystal or signal clock) to the UART.

LOOY.COM

#### 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

GM16C550

#### **TABLE I. UART Reset Configuration**

COMTW

WW.100Y.COM.TW

| Register / Signal △                                                                                                                                                                                                                                                                                                                                                      | Reset Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset State                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Enable Register<br>Interrupt Identification Register<br>FIFO Control<br>Line Control Register<br>MODEM Control Register<br>Line status Register<br>MODEM Status Register<br>SOUT<br>INTR (RCVR Errs)<br>INTR (RCVR Data Ready)<br>INTR (RCVR Data Ready)<br>INTR (THRE)<br>INTR (Modem Status Changes)<br>OUT2<br>RTS<br>DTR<br>OUT1<br>RCVR FIFO<br>XMIT FIFO | Master Reset<br>Master Reset<br>Master Reset<br>Master Reset<br>Master Reset<br>Master Reset<br>Master Reset<br>Master Reset<br>Read LSR/MR<br>Read RBR/MR<br>Read IIR/Write THR/MR<br>Read MSR/MR<br>Master Reset<br>Master Reset | 0000 0000 (Note<br>0000 0001<br>0000 0000<br>0000 0000<br>0110 0000<br>xxxx 0000 (Note<br>High<br>Low<br>Low<br>Low<br>High<br>High<br>High<br>High<br>High<br>High<br>High<br>All Bits Low<br>All Bits Low |

WWW.100Y.COM.TW Note 2 : Bits 7-4 are driven by the input signals. WWW.10 WWW.100Y.COM

WWW.100Y.COM.TW

WWW.100Y.CU

WWW.

LON TW

WWW.100Y.COM.TW

WW

WWW.100Y.COM.TW

100X.COM.TW

#### 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### GM16C550

M.TW

OM.TW

COM.TW

N.COM.I

JOY.COM 100X.CON

| GM16                                     |                                          |                                              | 98787                      | 755-832                                | 明) 86-                            | 特力电子(上;<br>特力电子(深;<br>Http://ww                                               | 正<br>正<br>正<br>上<br>上<br>上                                     | CO,<br>ON<br>DAT | 00Y.CC                                             | 1.1<br>1.17<br>171             |                  | W.          |

|------------------------------------------|------------------------------------------|----------------------------------------------|----------------------------|----------------------------------------|-----------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|------------------|----------------------------------------------------|--------------------------------|------------------|-------------|

| Bit 15                                   | Bit 14                                   | Bit 13                                       | Bit 12                     | Bit 11                                 | Bit 10                            | Bit 9                                                                         | Bit 8                                                          | DLM              | Divisor<br>Latch<br>(MS)                           | 1 DLAB =                       | A                |             |

| Bit 7                                    | Bit 6                                    | Bit 5                                        | Bit 4                      | Bit 3                                  | Bit 2                             | BitJ                                                                          | Bit 0                                                          | DLL              | Divisor<br>Latch<br>(LS)                           | 0 DLAB =                       | -                |             |

| Bit 7                                    | Bit 6                                    | Bit 5                                        | Bit 4                      | Bit 3                                  | Bit 2                             | Bit 1                                                                         | Bit 0                                                          | SCR              | Scratch<br>Register                                | 7                              |                  | LN<br>M     |

| Data<br>Camer<br>Detect<br>(DCD)         | Ring<br>Indicator<br>(RI)                | Data<br>Set<br>Ready<br>(DSR)                | Clear to<br>Send<br>(CTS)  | Delta<br>Data<br>Camer<br>Delect       | Trading<br>Edge Ring<br>Indicator | Delta<br>Data<br>Set<br>Ready<br>(DDSR)                                       | Delta<br>Clear<br>To Send<br>(DCTS)                            | MSR              | MODEM<br>Status<br>Register                        | 9                              | z z z            | L           |

| Error in<br>RCBR<br>FIFO<br>(Note2)      | Transmitter<br>Empty<br>(TEMT)           | Transmitter<br>Holding<br>Register<br>(THRE) | Break<br>Interrupt<br>(BI) | Framing<br>Error<br>(FE)               | Parity<br>Error<br>(PE)           | Overrun<br>Error<br>(OE)                                                      | Data<br>Ready<br>(DR)                                          | LSR              | Line<br>Status<br>Register                         | 252                            | 1.T<br>1.T<br>2. | e rs        |

| °M                                       | 000                                      | N.100                                        | Loop                       | Out2                                   | Out1                              | Request<br>to Send<br>(RTS)                                                   | Data<br>Terminal<br>Ready<br>(DTR)                             | MCR              | MODEM<br>Control<br>Register                       | 14 H                           | Address          | of Registe  |

| Divisor<br>Latch<br>Access Bit<br>(DLA3) | Set<br>Break                             | Stick<br>Parity                              | Even<br>Parity<br>Select   | Parity<br>Enable<br>(PEN)              | Number of<br>Stop Bits<br>(STB)   | Word<br>Length<br>Select<br>Bit 1<br>(WLS1)                                   | Word<br>Length<br>Select<br>Bit ()<br>(WLS0)                   | LCR              | Line<br>Control<br>Register                        | <b>G</b> <sup>3</sup> <b>Z</b> | Register         | Summary     |

| RCVR<br>Trigger<br>(MSB)                 | RCVR<br>Trigger<br>(LSB)                 | Reserved                                     | Reserved                   | DMA<br>Mode<br>select                  | XMIT<br>FIFO<br>Reset             | RCVR<br>FIFO<br>Reset                                                         | FIFO<br>Enable                                                 | FCR              | FIFO<br>Control<br>Register<br>(Write Only)        | 2                              | 07.0<br>100      | TABLE II. S |

| HFO <sub>3</sub><br>enabled<br>(note 2)  | FIFO <sub>3</sub><br>enabled<br>(note 2) | 0 N                                          | 0                          | Interrupt<br>ID<br>Bit (2)<br>(Note 2) | Interrupt<br>ID<br>Bit (1)        | Interrupt<br>ID<br>Bit (0)                                                    | "0" if<br>Interrupt<br>Pending                                 | IIR              | Interrupt<br>Enable<br>Register                    | E E                            | 100<br>1.10      | TA          |

| 81.10<br>W.1                             | ° 1                                      | 0                                            | 0                          | Enable<br>MODEM<br>Status<br>Interrupt | Enable<br>Receiver<br>Line        | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBEI) | Enable<br>Received<br>Data<br>Available<br>Interupt<br>(ERBFI) | IER              | Interrupt<br>Enable<br>Register                    | 1 DLAB0=                       | N.               | N N         |

| Data bit 7                               | Data bit 6                               | Data bit 5                                   | Data bit 4                 | Data bit 3                             | Data bit 2                        | Data bit 1                                                                    | Data bit 0                                                     | THR              | Transmitter<br>Holding<br>Register<br>(Write Only) | 0 DLAB =                       |                  | 1 2         |

| Data bit 7                               | Data bit 6                               | Data bit 5                                   | Data bit 4                 | Data bit 3                             | Data bit 2                        | Data bit 1                                                                    | Data bit 0                                                     | RBR              | Receiver<br>Buffer<br>Register<br>(Read Only)      | 0 DLAB =                       | N.               |             |

| L                                        | 9                                        | S                                            | 400                        | m 100                                  | 5                                 | 2                                                                             | ° OM.                                                          | 001              | N.W.I                                              | No.                            | Bit              |             |

WW

WWW.100Y.CO

WWW.100Y.COM.TW

WWW.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

GM16C550

#### Registers

The system programmer may be Access any of the UART registers summarized in Table II via the CPU. These registers control UART operations including transmission and reception of data. Each register bit in Table II has its name and reset state shown.

#### LINE CONTROL REGISTER

The system programmer specifies the format of the asynchronous data communications exchange and set the Divisor Latch Access bit via the Line Control Register (LCR). The programmer can also read the contents of the Line Control Register. The read capability simplifies system programming and eliminates the need for separate storage in system memory of the LCR. Details on each bit follow:

**Bit 0 and 1:** These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 is as follows.

| Bit 1    | Bit 0 | Character Length |

|----------|-------|------------------|

| 0        | 0     | 5 Bits           |

| 0        | 1     | 6 Bits           |

| 1        | 0     | 7 Bits           |

| $CP^{r}$ | 1     | 8 Bits           |

**Bit 2:** This bit specifies the number of Stop bits transmitted and received in each serial character. If bit 2 is a logic 0, one Stop bit is generated in the transmitted data. If Bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half Stop bits are generated. If bit 2 is a logic 1 When either a 6-, 7-, or 8-bit word length is selected, two Stop bit are generated. The Receiver checks the first Stop bit only, regardless of the number of Stop bit selected.

**Bit 3:** This bit is the Parity Enable bit. When bit 3 is a logic 1, a Parity bit is generated (transmit data) or checked (receive data) between the last data word bit and Stop bit of the serial data. (The Parity bit is used to produce an even or odd number of 1s when the data word bits and the Parity bit

#### **Typical Clock Circuits**

are summed).

**Bit 4:** This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, and odd number of logic 1s is transmitted or checked in the data word bits and Parity bit. When bit 3 is a logic 1 and it 4 is a logic 1, an even number of logic 1s is transmitted or checked.

**Bit 5:** This bit is the Stick Parity bit. When bit3, 4 and 5 are logic 1 the Parity bit is transmitted and checked as a logic 0. If bit 3 and 5 are 1 and bit 4 is a logic 0 then the Parity bit is transmitted and checked as a logic 1. If bit 5 is a logic 0 Stick Parity is disabled.

**Bit 6:** This bit is the Break Control bit. It causes a break condition to be transmitted to the received UART. When it is set to logic 1, The serial output (SOUT) is forced to the Spacing (logic 0) state. The break is disabled by setting bit 6 to a logic 0. The Break Control bit acts only on SOUT and has no effect on the transmitted logic.

**Note :** This feature enables the CPU to alert a terminal in during the break. The Transmitter can be used as a character timer to accurately establish the break duration.

a computer communications system.

If the following sequence is followed, no erroneous or extraneous characters will be transmitted because of the break.

1. Load on all Os, pad character, in response to THRE.

2. Set break after the next THRE

3. Wait for the transmitter to be idle. (TEMT = 1), and clear break when normal transmission has to be tired.

During the bread, the Transmitter can be used as a character timer to accurately establish the break duration.

**Bit 7:** This bit is the Divisor Latch Access Bit (DLAB). It must be set high (logic) to access the Divisor Latches of the Baud Generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.

## WW.100Y.COM.TW **Typical Crystal Oscillator Network**

COM.TW

| 3.1MHz    | 1MO          |          |         |         |

|-----------|--------------|----------|---------|---------|

|           | 1 <b>M</b> Ω | 1.5k     | 10-30pF | 40-60pF |

| 1.8MHz    | 1ΜΩ          | 1.5k     | 10-30pF | 40-60pF |

| 1.01/11/2 | 110132       | 1. There | 10 Sopr |         |

### I.COM.TW OY.COM.TW TABLE III. Baud Rates Using 1.8432 MHz Crystal

WWW.100Y.COM.TW

WWW.100Y.CO

WWW.

1001 COM.TW

WWW.100Y.COM.TW

COM.TW

| Desired Baud Rate | Decimal Divisor<br>Used to Generate<br>16 <sup>-</sup> Clock | Percent Error Difference<br>Between Desired and Actual |

|-------------------|--------------------------------------------------------------|--------------------------------------------------------|

| 50                | 2304                                                         | COM.                                                   |

| 75                | 1536                                                         | N 1 1001. ONLIN                                        |

| 110               | 1047                                                         | 0.026                                                  |

| 134.5             | 857                                                          | 0.058                                                  |

| 150               | 768                                                          | WWWWWWWWWWWWWWW                                        |

| 300               | 384                                                          | W.IO = COM.                                            |

| 600               | 192                                                          | WW 1002 ON TW                                          |

| 1200              | 96                                                           | WWW. IC OW                                             |

| 1800              | 64                                                           | MILL COMPT                                             |

| 2000              | 58                                                           | 0.69                                                   |

| 2400              | 48                                                           | COM.                                                   |

| 3600              | 32                                                           | N NN 100X.                                             |

| 4800              | 24                                                           | TWN - TO COM.                                          |

| 7200              | 16                                                           | W 1001. ON                                             |

| 9600              | 12 COM                                                       | WWW. OV.COM                                            |

| 19200             | 6                                                            |                                                        |

| 38400             | 3                                                            | AN WW TOOX.CO                                          |

| 56000             | $^{2}$                                                       | 2.86                                                   |

WW

WWW.100Y.COM.TW

| 勝特力材料      | 886-3-5753170   |

|------------|-----------------|

| 胜特力电子(上海)  | 86-21-54151736  |

| 胜特力电子(深圳)  | 86-755-83298787 |

| Http://www | . 100y. com. tw |

#### TABLE IV. Baud Rates Using 3.072 MHz crystal

COMIN

WW.100Y.COM.TW

| Desired Baud Rate | Decimal Divisor<br>Used to Generate<br>16´Clock | Percent Error Difference<br>Between Desired and Actua |

|-------------------|-------------------------------------------------|-------------------------------------------------------|

| 50                | 3840                                            | WWW. CON- TW                                          |

| 75                | 2560                                            | W.100 COM. I                                          |

| 110               | 1745                                            | 0.026                                                 |

| 134.5             | 1428                                            | 0.034                                                 |

| 150               | 1280                                            | N 1001.0 - M.TW                                       |

| 300               | 640                                             | WWW. W COM                                            |

| 600               | 320                                             | 100 1. OM. 1                                          |

| 1200              | 160                                             | WWW. ONLOW                                            |

| 1800              | 107                                             | 0.312                                                 |

| 2000              | 96                                              | WW 100Y CONT                                          |

| 2400              | 80                                              | COM.                                                  |

| 3600              | 53                                              | 0.628                                                 |

| 4800              | 40                                              | WWW. Park COn-                                        |

| 7200              | 27                                              | 1.23                                                  |

| 9600              | 20                                              | WW TOY.CO                                             |

| 19200             | 10                                              | CON CONTRACTOR                                        |

| 38400             | 5                                               | WWW TOOL                                              |

## VN.100Y.CO WWW.100Y.C

WWW.100Y.CO

WWW.100Y.COM.TW

WWW

| Desired Baud Rate | Decimal Divisor<br>Used to Generate<br>16´Clock | Percent Error Difference<br>Between Desired and Actual |

|-------------------|-------------------------------------------------|--------------------------------------------------------|

| 50 0              | 10000                                           | OW TANK AND TANK CON                                   |

| 75                | 6667                                            | 0.005                                                  |

| 110 COM           | 4545                                            | 0.010                                                  |

| 134.5             | 3717                                            | 0.013                                                  |

| 150               | 3333                                            | 0.010                                                  |

| 300               | 1667                                            | 0.020                                                  |

| 600               | 833                                             | 0.040                                                  |

| 1200              | 417                                             | 0.080                                                  |

| 1800              | 277                                             | 0.080                                                  |

| 2000              | 250                                             | MY - WT - 100                                          |

| 2400              | 208                                             | 0.160                                                  |

| 3600              | 139                                             | 0.080                                                  |

| 4800              | 104                                             | 0.160                                                  |

| 7200              | 69                                              | 0.644                                                  |

| 9600              | 52                                              | 0.160                                                  |

| 19200             | 26                                              | 0.160                                                  |

| 38400             | 13                                              | 0.160                                                  |

| 56000             | 9                                               | 0.790                                                  |

| 128000            | 4                                               | 2.344                                                  |

| 256000            | 2                                               | 2.344                                                  |

WW

| Interrupt Set and Reset Function           Priorit<br>Level         Interrupt Type         Interrupt Source         Interrupt Reset Control           -         None         None         None         None           +         None         None         None         -           Highest         Receiver Line Status         Overnun Error or Parity Error or<br>Framing Error or Break Interrupt         Reading the Line Status           Second         Receiver Data         Receiver Data Available or<br>Trigger Level Reached         Register           Second         Available         None         Register           Second         Receiver Data Available or<br>Trigger Level Reached         Register for the FIFO Drops           Second         Indication         No Characters Have Been         Register for the FIFO Drops           Second         Indication         Resolved Pata         Reading the Receiver Buffer           Second         Indication         Register Level Reached         Register Grow           Second         Indication         Reading the Line Status         Reading the Receiver Buffer           Second         Reading the Line Status         Reading the Receiver Buffer         Register Invel           Second         Printing Receiver Bufter         Register Invel         Reading the Receiver Buffer <th>WW.100Y</th> <th>COM<br/>N.COM</th> <th>TW<br/>A.TW</th> <th>4</th> <th>胜特力电<br/>Http:</th> <th>子(深圳) 86-755-8<br/>//www.100y.com</th> <th>3298787<br/>a. tw</th> <th>GM16C550</th> | WW.100Y                                                        | COM<br>N.COM            | TW<br>A.TW                                                | 4                                                                    | 胜特力电<br>Http:                                                                        | 子(深圳) 86-755-8<br>//www.100y.com                                                                                                                                    | 3298787<br>a. tw                                                                                            | GM16C550                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------|-----------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Interrupt Type Interrupt Type None Receiver Line Status Received Data Available Character Timeout Indication Transmitter Holding Register Empty MODEM Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A A A A A A A A A A A A A A A A A A A                          | Interrupt Reset Control | 0M.TV<br>CONLT<br>CONL<br>CONL<br>V.COM<br>0V.CO<br>0V.CO | Reading the Line Status<br>Register                                  | Reading the Receiver Buffer<br>Register or the FIFO Drops<br>Below the Trigger Level | Reading the Receiver<br>Buffer Register                                                                                                                             | Reading the IIR Register (if<br>Source of interrupt) or Writing<br>into the Transmitter Holding<br>Register | Reading the MODEM Status<br>Register                                           |

| Interrupt Type Interrupt Type None Receiver Line Status Received Data Available Character Timeout Indication Transmitter Holding Register Empty MODEM Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Interrupt Set and Reset Function                               | Interrupt Source        | None                                                      | Overrun Error or Parity Error or<br>Framing Error or Break Interrupt | Receiver Data Available or<br>Trigger Level Reached                                  | No Characters Have Been<br>Removed From or Input to the<br>RCVR FIFO During the Last 4<br>char.<br>Times and There is at Least 1<br>char.<br>In it During This Time | Transmitter Holding<br>Register Empty                                                                       | Clear to Send or Data Set Ready<br>or Ring Indicator or Data Carrier<br>Detect |

| Priorit       y       Level       -       -       -       Second       Second       Third       Third       Fourth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 201 <del>7.</del> 1<br>2.COM.T<br>22.COM.<br>12.COM<br>107.COM | Interrupt Type          | None                                                      | Receiver Line Status                                                 | Received Data<br>Available                                                           | Character Timeout<br>Indication                                                                                                                                     | Transmitter Holding<br>Register Empty                                                                       | MODEM Status                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100Y.CC                                                        | Priorit<br>y<br>Level   | 2                                                         | Highest                                                              | Second                                                                               | Second                                                                                                                                                              | Third                                                                                                       | Fourth                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | aterrup<br>ntificat                                            | Bit<br>1                | on                                                        | 1                                                                    | 0                                                                                    | 0                                                                                                                                                                   | 1                                                                                                           | 0                                                                              |

| Bit     1       0     0       0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Idei                                                           | Bit<br>2                | 0                                                         |                                                                      | AMM.                                                                                 | TON.COM.I                                                                                                                                                           | 0                                                                                                           | 0                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FIFO<br>Mode<br>Only                                           | Bit 3                   | CO M                                                      | 0                                                                    | 0                                                                                    | W.1001.COM                                                                                                                                                          | 0                                                                                                           | 0                                                                              |

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

WW

WWW.100Y.CO

WWW.100Y.COM.TW

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

#### PROGRAMMABLE BAUD GENERATOR

The UART contains a programmable Baud Generator that is capable of taking any clock input from 2 to  $2^{16}$ –1. 4MHz is the highest input clock frequency recommended when the divisor = 1. The output frequency of the Baud Generator is 16 × the Baud [divisor # = (frequency input) ÷ (baud rate ×16)] Two 8-bit latches store the divisor in a 16-bit binary format. These Divisor Latches must be loaded during initialization to ensure proper operation of the Baud Generator. Upon loading either or the Divisor Latches, a 16-bit Baud counter is immediately loaded.

Tables III, IV and V provide decimal divisors to use with crystal frequencies of 1.8432 MHz 3.072MHz and 8 MHz, respectively. For baud rates of 38400 and below, the error obtain is minimal. The accuracy of the desired baud rate is dependent on the crystal frequency chosen. Using a divisor of zero is not recommended.

#### LINE STATUS REGISTER

This register provides status information to the CPU concerning the data transfer. Table II shows the contents of the Line Status Register. Details on each bit follow.

**Bit 0:** This bit is the receiver Data Ready (DR) indicator. Bit 0 is set to logic 1whenever a complete incoming character has been received and transferred into the Receiver Buffer Register or the FIFO. Bit 1 is reset to a logic 0 by reading all of the data in the Receiver Buffer Register or the FIFO.

**Bit 1:** This bit is the Overrun Error (OE) indicator. Bit 1 indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, thereby destroying the previous character. The OE indicator is set to a logic 1 upon detection of an overrun condition and reset whenever the CPU reads the contents of the Line Status Register