# HD74LS195A.4-bit Parallel-Access Shift Registers

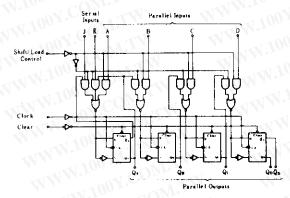

This 4-bit register features parallel inputs, parallel outputs, JR serial inputs, shift/load control input, and a direct overriding clear. All inputs are buffered to lower the input drive requirements. The registers have two modes of operation:

Parallel (broadside) load

Shift (in the direction  $Q_A$  toward  $Q_D$ )

Parallel loading is accomplished by applying the four bits of data and taking the shift/load control input low. The data

## BLOCK DIAGRAM

is loaded into the associated flip-flop and appears at the outputs after the positive transition of the clock input. During loading, serial data flow is inhibited. Shifting is accomplished synchronously when the shift/load control input is high, Serial data for this mode is entered at the J-R inputs. These inputs permit the first stage to perform as a J-R, D-, or T-type flip-flop as shown in the function table.

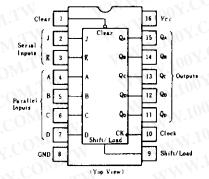

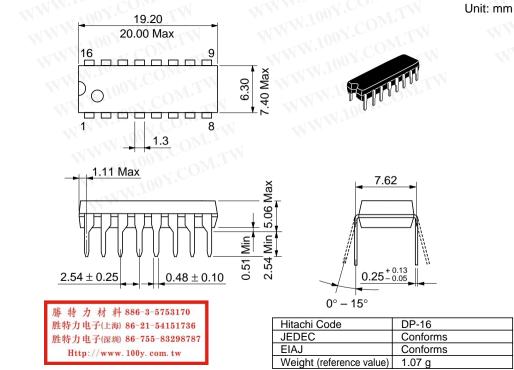

# PIN ARRANGEMENT

### RECOMMENDED OPERATING CONDITIONS

| 100               | Item                     | Symbol   | min | typ   | max | Unit |

|-------------------|--------------------------|----------|-----|-------|-----|------|

| Clock frequency   | N.CO. mil                | felock   | 0   | 1     | 30  | MHz  |

| Clock pulse width | COM-                     | te(CK)   | 16  | Mr.   |     | ns   |

| Clear pulse width | 001.001.114              | tw(CLR)  | 12  | M.T.Y | - V | ns   |

|                   | Shift/load               |          | 25  | VT.   |     |      |

| Setup time        | Seiral and parallel data | tou .    | 15  | COM.  | a l | ns   |

|                   | Clear inactive-state     |          | 25  | -Ma   |     |      |

| Release time      | AT STREET                | tretease |     |       | 5   | ns   |

| Hold time         |                          | th       | 0   | T COM | -   | ns   |

# **EFUNCTION TABLE**

|       | WITTE       | Inpu  | ts | <u>Dir.</u> |   |     |       | <u>MM</u> |      | 1001 | Outputs | ļ   |     |

|-------|-------------|-------|----|-------------|---|-----|-------|-----------|------|------|---------|-----|-----|

| Clear | Shift/Load  | Clock | Se | rial        |   | Раг | allel |           | · QA | QB   | Qc      | QD  | ā   |

| Ciear | Juilt/ Load | CIOCK | 1  | ĸ           | A | В   | C     | D         | -10  |      | 100     |     |     |

| L     | ×           | ×     | ×  | X           | × | X   | ×     | ×         | L    | L    | L L     | L   | }   |

| н     | L           |       | ×  | ×           | a | b   | c     | d         | a    | Ь    | c       | d   |     |

| н     | н 🗸         | L     | X  | ×           | × | ×   | ×     | ×         | QAO  | QBO  | Qco     | Quo | Ğ   |

| н     | Н           |       | L  | Н           | × | ×   | ×     | ×         | QAO  | QAO  | QBn     | Qua | Q   |

| Н     | Н           | 1     | L  | L           | × | ×   | ×     | ×         | L    | QAn  | QHe     | QCn | ្រុ |

| H     | н           |       | Н  | H           | × | ×   | ×     | ×         | H    | QAn  | QBn     | Qcn | Q   |

| н     | н           |       | Н  | L           | x | ×   | ×     | ×         | QAD  | QAn  | QBn     | Qcn | Q   |

Notes) 1. H; high level, L; low level, X; irrelevant

2. 1; transition from low to high level

3. 4; transition from high to low level

4. a~d; the level of steady-state input at inputs A,B,C, or D, respectively

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

5. QA0~QD0; the level of QA, QB, QC, or QD, respectively, before the indicated steady-state input conditions were established.

6. QAn~QDn; the level of QA, QB, QC, or QD, respectively, before the most-recent 1 transition of the clock.

# ELECTRICAL CHARACTERISTICS ( $Ta = -20 \sim +75^{\circ}C$ )

| Item                         | Symbol | Test Conditio                                     | ns <                      | min  | typ*    | max  | Unit |

|------------------------------|--------|---------------------------------------------------|---------------------------|------|---------|------|------|

|                              | VIN    | TOO CONTRACT                                      |                           | 2.0  |         | 0/7. | V    |

| Input voltage                | VIL    | 1001.                                             |                           |      | 1002.0  | 0.8  | v    |

|                              | Von    | $V_{CC} = 4.75V, V_{IH} = 2V, V_{IL} = 0.8V$      | , <i>Іон</i> == – 400 µ А | 2.7  | 100     |      | V    |

| Output voltage               |        | $V_{CC} = 4.75V, V_{IH} = 2V,$                    | $I_{OL} = 4mA$            |      | 1.75    | 0.4  | v    |

| 100Y.COM TH                  | Voi.   | $V_{IL}=0.8V$                                     | IoL=8mA                   |      | x 100 Y | 0.5  | 3.14 |

| · CONTRACT                   | Ін     | $V_{cc} = 5.25 V, V_l = 2.7 V$                    | W                         |      |         | 20   | μA   |

| Input current                | II.    | $V_{cc} = 5.25 V, V_I = 0.4 V$                    |                           |      | 11-1°   | -0.4 | mA   |

| TION.CONTR                   | lı -   | $V_{cc} = 5.25 V, V_I = 7 V$                      | 1.7                       | _    | 1       | 0.1  | mA   |

| Short-circuit output current | los    | Vcc=5.25V                                         | WT.                       | - 20 | N 7.    | -100 | mA   |

| Supply current**             | Icc    | Vcc=5.25V                                         | M.                        | -    | 14      | 21   | mA   |

| Input clamp voltage          | Vik    | $V_{CC} = 4.75 \text{V}, \ I_{IN} = -18 \text{m}$ | M.I.                      | -    |         | -1.5 | V    |

\* VCC=5V, Ta=25°C

\*\* With all outputs open, shift/load grounded, and 4.5V applied to the J, K, and data inputs, I<sub>CC</sub> is measured by applying a momentary ground, followed by 4.5V, to clear and then applying a momentary ground, followed by 4.5V, to clock.

### **ESWITCHING CHARACTERISTICS** ( $V_{cc} = 5V$ , $T_a = 25^{\circ}C$ )

| Item                     | Symbol | Inputs | Outputs                        | Test Conditions      | min        | typ 🔨 | max | Unit |

|--------------------------|--------|--------|--------------------------------|----------------------|------------|-------|-----|------|

| Maximum clock frequency  | . Smox | Clock  | QA~QD                          | N.COM                | 30         | 39    |     | MHz  |

|                          | LPHL.  | Clear  | QA~QD                          | $C_L = 15 \text{pF}$ | . <u>-</u> | 19    | 30  | ns   |

| Propagation delay time   | tPLH . |        |                                | $R_L = 2k \Omega$    | N Per      | 14    | 22  | ns   |

| A Topugation actual that | tPHL.  | Clock  | $Q_A \sim Q_D, \overline{Q}_D$ | N. LUI COT           |            | 17    | 26  | ns   |

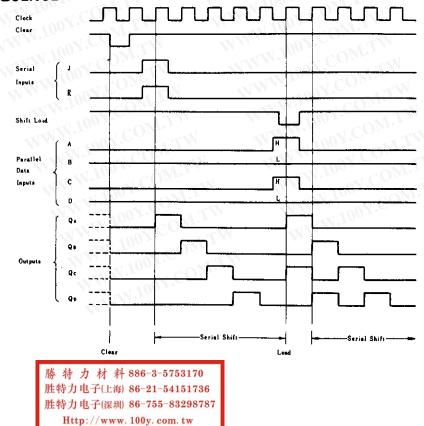

# COUNT SEQUENCE

# HD74LS195A

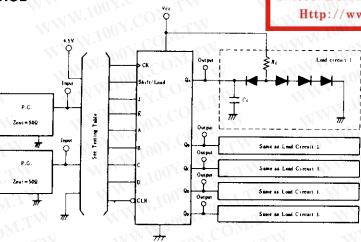

# TESTING METHOD

1) Test Circuit

#### Notes) 1. $C_L$ includes probe and jig capacitance. 2. All diodes are 1S2074 (f).

### 2) Testing Table

| . 📢          | From input                     | 100  | Inputs     |      |      |    |      |      |      |      | Outputs |     |     |     |     |  |

|--------------|--------------------------------|------|------------|------|------|----|------|------|------|------|---------|-----|-----|-----|-----|--|

| Item         | to output                      | CLR  | Shift/Load | J    | ĸ    | СК | A    | В    | С    | D    | Q۸      | Qв  | Qc  | QD  | QD  |  |

| fmaz         | 100                            | 4.5V | 4.5V       | 4.5V | GND  | IN | 4.5V | 4.5V | 4.5V | 4.5V | OUT     | OUT | OUT | OUT | OUT |  |

| tphl         | Clear→<br>Qa∼QD                | IN   | GND        | 4.5V | 4.5V | IN | 4.5V | 4.5V | 4.5V | 4.5V | OUT     | OUT | OUT | OUT | 100 |  |

| <b>I</b> PLH | Clock→                         | 4.5V | 4.5V       | 4.5V | GND  | IN | 4.5V | 4.5V | 4.5V | 4.5V | OUT     | OUT | OUT | OUT | OUT |  |

| <b>I</b> PHL | $Q_A \sim Q_D, \overline{Q}_D$ | 4.5V | GND        | 4.5V | 4.5V | IN | IN   | IN   | IN   | IN   | OUT     | OUT | OUT | OUT | OUT |  |

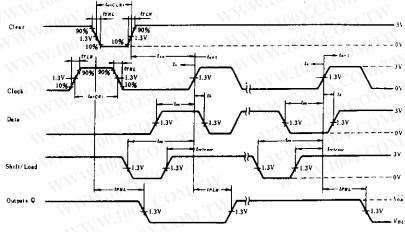

### Waveform

- Notes) 1. Input pulse; <sup>t</sup>TLH≤15ns, <sup>t</sup>THL≦6ns, PRR=1MHz, duty cycle 50%

- 2. A clear pulse is applied prior to each test.

- 3. Propagation delay times  $(t_{PLH} \text{ and } t_{PHL})$  are measured at  $t_{n+1}$ . Proper shifting of data is verified at  $t_{n+4}$  with a functional test.

- 4. J and  $\vec{K}$  inputs are tested the same as data A, B, C, and D

inputs except that shift/load input remains high.

- 5.  $t_n$ ; bit time before clocking transition.

- 6.  $t_{n+1}$ ; bit time after one clocking transition.

- 7.  $t_{n+4}$ ; bit time after four clocking transition.

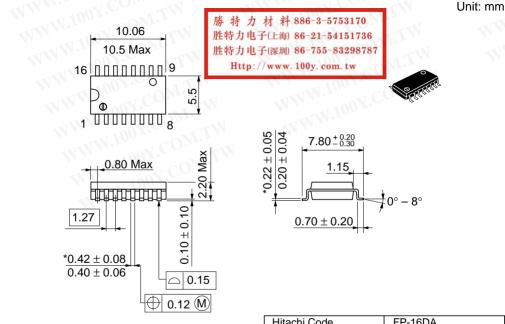

\*Dimension including the plating thickness Base material dimension

| Hitachi Code             | FP-16DA  |

|--------------------------|----------|

| JEDEC                    | —        |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.24 g   |

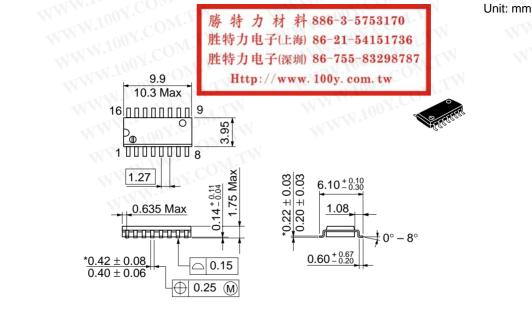

\*Dimension including the plating thickness Base material dimension

| Hitachi Code             | FP-16DN  |

|--------------------------|----------|

| JEDEC                    | Conforms |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.15 g   |

Cautions

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI

# HITACHI