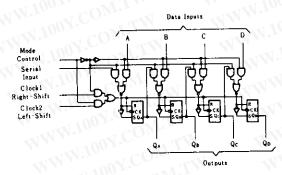

This 4-bit register features parallel and serial inputs, parallel outputs, mode control, and two clock inputs. The register has three mode operation:

- Parallel (broadside) load

- Shift right (the direction Cl<sub>A</sub> toward Q<sub>D</sub>)

- ◆ Shift left (the direction Q<sub>D</sub> toward Q<sub>A</sub>)

Parallel loading is accomplished by applying the four bits of data and taking the mode control input high. The data is loaded into the associated flip-flops and appears at the outputs after the high-to-low transition of the clock-2 input. During loading, the entry of serial data is inhibited. Shift right is accomplished on the high-to-low transition of clock-1 when the mode control is low; shift left is accomplished on the high-tolow transition of clock-2 when the mode control is high by connecting the output of each flip-flop to the parallel input of the previous flip-flop (QD to input C, etc.) and serial data is entered at input D. The clock input may be applied commonly to clock-1 and clock-2 if both modes can be clocked from the same source. Changes at the mode control input should normally be made while both clock inputs are low: however, conditions described in the last three lines of the function table will also ensure that register contents are protected.

#### BLOCK DIAGRAM

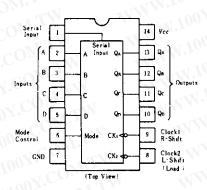

#### ARRANGEMENT

#### ■FUNCTION TABLE

|                   |        | TW. Ju | Inpu   | its              |     | - TANIV          | $CO_{M}$ . | Outputs         |                 |                 |                 |

|-------------------|--------|--------|--------|------------------|-----|------------------|------------|-----------------|-----------------|-----------------|-----------------|

| Mode Control 2(L) | Clocks |        | 07.    | Parallel         |     |                  |            | QA              | Qв              | Qc              | QD              |

|                   | 2(L)   | 100    | Serial | A                | В   | C                | D          | ( Q/A           | Ø.              | 87              | ₩.              |

| Н                 | Н      | ×      | ×      | ×                | ×   | ×                | ×          | QAO             | Qво             | <b>Q</b> co     | Qoo             |

| н                 | ţ      | ×      | ×      | a                | ь   | с                | d 10       | a               | b               | С               | d               |

| н                 | 1      | ×      | ×      | Q <sub>B</sub> † | Qc† | Q <sub>D</sub> † | d.         | Q <sub>Bn</sub> | Q <sub>Cn</sub> | QDn             | d               |

| L                 | L      | Н      | ×      | ×                | ×   | ×                | ×          | QAO             | Qво             | Qco             | Quo             |

| L                 | ×      | 11/1   | н      | ×                | ×   | ×                | ×          | Н               | QAn             | Q <sub>Bn</sub> | Qcn             |

| L                 | ×      | 411    | L      | ×                | ×   | ×                | ×          | L               | QAn             | Q <sub>Bn</sub> | Q <sub>Cn</sub> |

| 1                 | L      | L      | ×      | ×                | ×   | ×                | ×          | Qao             | Qво             | Qco             | Qυσ             |

| 1                 | L      | L.     | ×      | ×                | ×   | ×                | ×          | QAO             | Qво             | Qco             | QDO             |

| <b>.</b>          | L      | H      | ×      | ×                | ×   | N ×              | ×          | QAO             | Q <sub>BO</sub> | Qco             | Qoo             |

| <u>†</u>          | Н      | L.     | ×      | ×                | ×   | ×                | ×          | QAO             | Qво             | Qco             | Qpo             |

| <u>†</u>          | н      | Н      | ×      | 10×              | ×   | ×                | ×          | QAO             | Qво             | Qco             | QDO             |

- Notes) 1. H; high level, L; low level, X; irrelevant 2. †; transition from low to high level

- 3. 4; transition from high to low level

- 4. a~d; the level of steady-state input at inputs A,B,C, or D,

- 5. QA0~QD0; the level of QA, QB, QC, or QD, respectively,

before the indicated steady-state input conditions were established.

- 6. QAn~QDn; the level of QA, QB, QC, or QD, respectively, before the most-recent (†) transition of the clock.

- 7. †; Shifting left requirs external connection of QB to A, QC to B, and QD to C. Serial data is entered at input D.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

#### **TRECOMMENDED OPERATING CONDITIONS**

| Item              | Symbol     | min | typ  | max                              | Unit |  |

|-------------------|------------|-----|------|----------------------------------|------|--|

| Clock frequency   | fclock     | 0   | -71( | 25                               |      |  |

| Clock pulse width | į tw(CK)   | 25  | Mrs  |                                  | ns   |  |

| Setup time        | tre        | 20  | . W. | $I_{\Omega \overline{\Omega}}$ . | ns   |  |

| Hold time         | th         | 10  |      | 100                              | ns   |  |

| Enable time 1     | tenable 1  | 20  |      |                                  | ns   |  |

| Enable time 2     | tenable 2  | 20  | -311 | 1 70                             | ns   |  |

| Inhibit time 1    | Linkibit 1 | 20  | ME.  | - <del></del>                    | ns   |  |

| Inhibit time 2    | Linkibit 2 | 20  |      | W.                               | ns   |  |

Clock Enable/Inhibit Times

## **ELECTRICAL CHARACTERISTICS** ( $Ta = -20 \sim +75^{\circ}C$ )

| Item                         | Symbol | Test Condition                                                       | ns                    | min   | typ* | max  | Unit |

|------------------------------|--------|----------------------------------------------------------------------|-----------------------|-------|------|------|------|

| TAN MILE OF COMP.            | VIH    | WWW.                                                                 | On The                | 2.0   | -11  |      |      |

| Input voltage                | VIL    | W.100                                                                | <u>-</u>              | = 131 | 0.8  |      |      |

| MAN 100X                     | Voн    | $V_{CC} = 4.75 \text{V}, V_{IH} = 2 \text{V}, V_{IL} = 0.8 \text{V}$ | $I_{OH} = -400 \mu A$ | 2.7   |      | 100  | v    |

| Output voltage               |        | $V_{CC} = 4.75V$ , $V_{IH} = 2V$ ,                                   | IoL = 4mA             | TW    |      | 0.4  | NY.U |

|                              | Vol    | $V_{IL}=0.8V$                                                        | IoL = 8mA             | 3     |      | 0.5  | ~J.( |

| 11/1007:0                    | ItH    | $V_{CC} = 5.25 \text{V},  V_I = 2.7 \text{V}$                        |                       |       |      | 20   | μA   |

| Input current                | In     | $V_{CC} = 5.25 \text{V},  V_I = 0.4 \text{V}$                        | MY.Co                 | (Pr   |      | -0.4 | mA   |

|                              | II II  | $V_{CC} = 5.25 \text{ V},  V_I = 7 \text{ V}$                        | <1 CO                 | 11.   |      | 0.1  | mA   |

| Short-circuit output current | Ios    | $V_{CC}=5.25V$                                                       | 1001.                 | -20   |      | -100 | mA   |

| Supply current * *           | lec .  | $V_{CC} = 5.25 \text{V}$                                             | TOUX.C.               |       | 13   | 21   | mА   |

| Input clamp voltage          | Vik    | $V_{CC} = 4.75 \text{V}, I_{IN} = -18 \text{m} A$                    | - 1 C                 | OM.   |      | -1.5 | V    |

<sup>\*</sup> VCC=5V, Ta=25°C

#### **ESWITCHING CHARACTERISTICS** ( $V_{CC} = 5V$ , $T_a = 25^{\circ}C$ )

| Item                    | Symbol | Test Conditions                               | min       | typ | max | Unit |

|-------------------------|--------|-----------------------------------------------|-----------|-----|-----|------|

| Maximum clock frequency | fmoz   | W.TW                                          | 25        | 36  |     | MHz  |

|                         | tPLH   | $C_L = 15 \text{pF},  R_L = 2 \text{k}\Omega$ | 1. VOOT ! | 18  | 27  | ns   |

| Propagation delay time  | tPHL . |                                               |           | 21  | 32  | ns   |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

WWW.100X

<sup>\*\*</sup>I<sub>CC</sub> is measured with all outputs and serial input open; A,B,C, and D inputs grounded; mode control at 4.5V; and momentary 3V, then ground, applied both clock inputs.

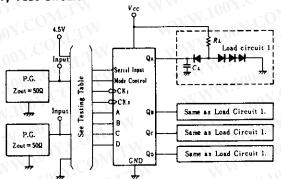

#### **TESTING METHOD**

#### 1) Test Circuit

Notes) 1. C<sub>L</sub> includes probe and jig capacitance.

2. All diodes are 1S2074 B.

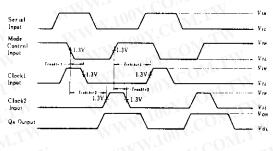

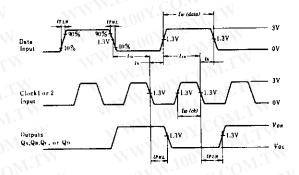

#### Waveform

Note) 1. Input pulse: t<sub>TLH</sub>, t<sub>THL</sub>≤10ns, Data PRR=500kHz Clock PRR=1MHz

#### 2) Testing Table

| Îtem | From input | Inputs |      |                 |                  |      |      |      |      | Outputs |     |     |     |

|------|------------|--------|------|-----------------|------------------|------|------|------|------|---------|-----|-----|-----|

|      | to output  | CK-1   | CK-2 | Mode<br>Control | Secial<br>Inputs | A    | В    | С    | D    | Q۸      | Qв  | Qυ  | Qυ  |

| fmax | CK-1→Q     | IN     | 4.5V | 0V              | IN               | 4.5V | 4.5V | 4.5V | 4.5V | OUT     | OUT | OUT | OUT |

|      | CK-2→Q     | 4.5V   | IN   | 4.5V            | 4.5V             | IN   | IN   | IN   | IN   | OUT     | OUT | OUT | OUT |

| tPLH | CK-1→Q     | IN     | 1.5V | 0V              | IN               | 4.5V | 4.5V | 4.5V | 4.5V | OUT     | OUT | OUT | OUT |

| tPHL | CK-2→Q     | 4.5V   | IN   | 4.5V            | 4.5V             | IN   | IN   | IN   | IN   | OUT     | OUT | OUT | OUT |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

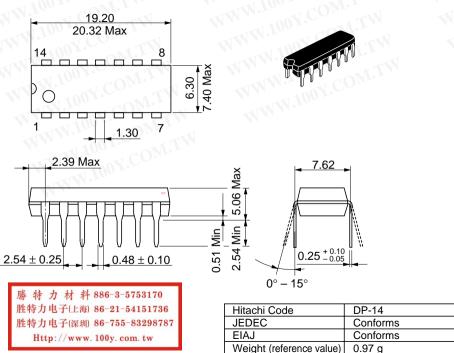

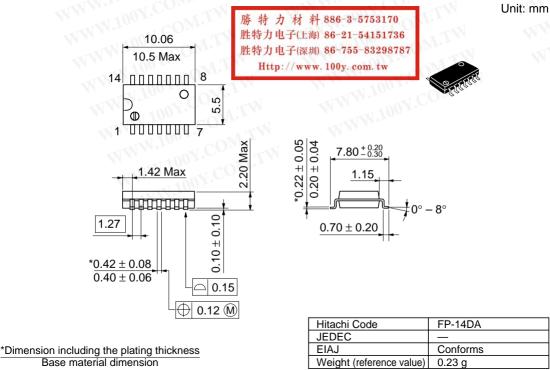

Unit: mm

Unit: mm 特力材料886-3-5753170 海) 86-21-54151736 电子(深圳) 86-755-83298787 8.65 Http://www.100y.com.tw 9.05 Max 14<u>000000</u> 8 3.95 7 000000 7 .75 Max  $*0.20 \pm 0.05$  $6.10^{+0.10}_{-0.30}$ 0.635 Max 1.08  $0.60 \pm 0.67$ 1.27  $0.14^{+0.11}_{-0.04}$ \*0.40 ± 0.06 0.15 0.25 M Hitachi Code FP-14DN **JEDEC** Conforms EIAJ Conforms Weight (reference value) 0.13 g

\*Pd plating

# 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI