## INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

# HEF4007UB gates Dual complementary pair and inverter

Product specification

File under Integrated Circuits, IC04

January 1995

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

HEF4007UB gates

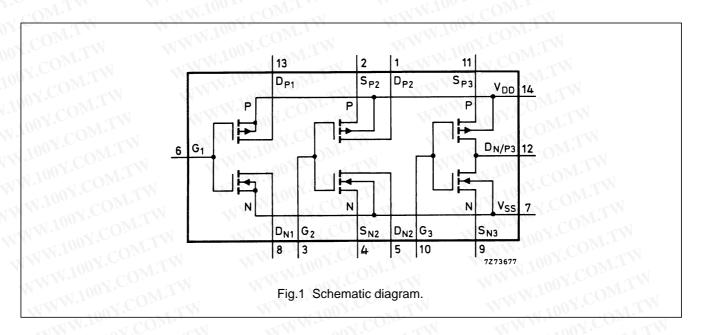

#### DESCRIPTION

The HEF4007UB is a dual complementary pair and an inverter with access to each device. It has three n-channel and three p-channel enhancement mode MOS transistors.

WWW. COX.CO.

(SOT27-1)

14-lead DIL; plastic

HEF4007UBD(F): 14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4007UBT(D): 14-lead SO; plastic

(SOT108-1)

(): Package Designator North America

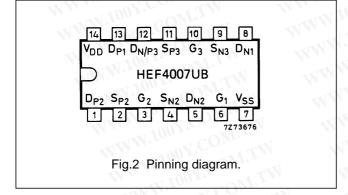

### **PINNING**

S<sub>P2</sub>, S<sub>P3</sub> source connections to 2nd and 3rd

p-channel transistors

$D_{P1}$ ,  $D_{P2}$  drain connections from the 1st and 2nd

p-channel transistors

$D_{N1},\,D_{N2}-$  drain connections from the 1st and 2nd

n-channel transistors

n-channel transistors

D<sub>N/P3</sub> common connection to the 3rd p-channel

and n-channel transistor drains

G<sub>1</sub> to G<sub>3</sub> gate connections to n-channel and

p-channel of the three transistor pairs

## FAMILY DATA, IDD LIMITS category GATES

See Family Specifications for V<sub>IH</sub>/V<sub>IL</sub> unbuffered stages

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

HEF4007UBP(N):

HEF4007UB gates

|                         | V <sub>DD</sub><br>V | SYMBOL           | TYP. | MAX. |      | TYPICAL EXTRAPOLATION FORMULA       |

|-------------------------|----------------------|------------------|------|------|------|-------------------------------------|

| Propagation delays      | W.1003               | COMIT            | ī    | WW   | 700. | COMP                                |

| $G_n \to D_N  ;  D_P$   | 5.00                 | T.M.T            | 40   | 80   | ns   | 13 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW             | 10                   | t <sub>PHL</sub> | 20   | 40   | ns   | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   | MY.COM           | 15   | 30   | ns   | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

| COM.                    | 5                    | CON              | 40   | 75   | ns   | 13 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> | 20   | 40   | ns   | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   | 1.100 1. CO      | 15   | 30   | ns   | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

| Output transition times | 5                    | N 100 Y          | 60   | 120  | ns   | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| HIGH to LOW             | 10                   | t <sub>THL</sub> | 30   | 60   | ns   | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                         | 15                   | M. TOOX.C        | 20   | 40   | ns   | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

| M. Ind COM.             | 5                    | WW. FOOT         | 60   | 120  | ns   | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| LOW to HIGH             | 10                   | t <sub>TLH</sub> | 30   | 60   | ns   | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                         | 15                   | N 1 100          | 20   | 40   | ns   | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                 | V <sub>DD</sub> | TYPICAL FORMULA FOR P ( $\mu$ W)              | WWW.100Y.COM.TW                        |

|-----------------|-----------------|-----------------------------------------------|----------------------------------------|

| Dynamic power   | 5               | 4500 $f_i + \sum (f_o C_L) \times V_{DD}^2$   | where                                  |

| dissipation per | 10              | 20 000 $f_i + \sum (f_o C_L) \times V_{DD}^2$ | f <sub>i</sub> = input freq. (MHz)     |

| package (P)     | 15              | 50 000 $f_i + \sum (f_0 C_L) \times V_{DD}^2$ | f <sub>o</sub> = output freq. (MHz)    |

|                 | JAN             |                                               | C <sub>L</sub> = load capacitance (pF) |

|                 | OM              |                                               | $\Sigma(f_0C_L)$ = sum of outputs      |

|                 | $CO_{M',T}$     |                                               | V <sub>DD</sub> = supply voltage (V)   |

N.100Y.COM.TW

# HEF4007UB gates

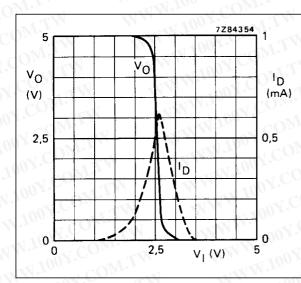

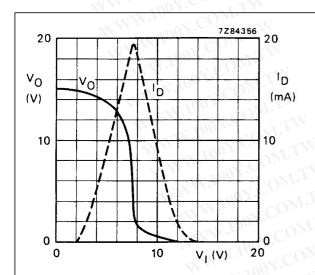

Fig.3 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD} = 5 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$ .

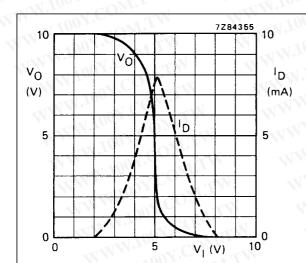

Fig.4 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD} = 10 \text{ V}$ ;  $T_{amb} = 25 ^{\circ}\text{C}$ .

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Fig.5 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD}$  = 15 V;  $T_{amb}$  = 25 °C.

HEF4007UB gates

#### **APPLICATION INFORMATION**

Some examples of applications for the HEF4007UB are:

- · High input impedance amplifiers

- Linear amplifiers

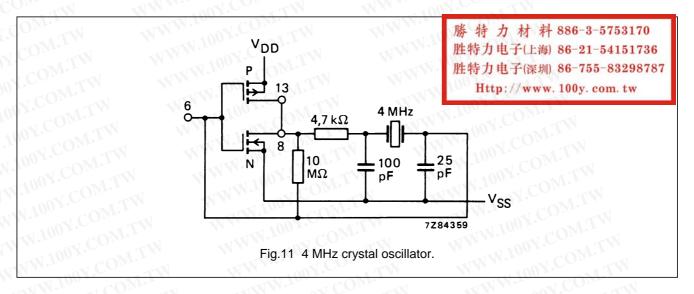

- · (Crystal) oscillators

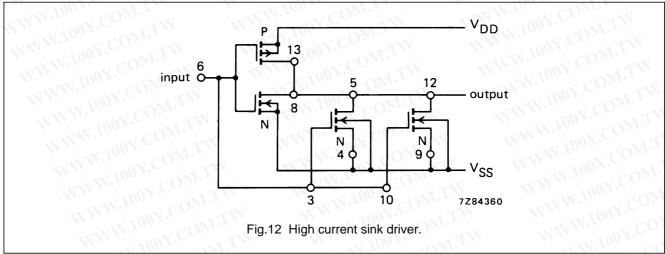

- · High-current sink and source drivers

- · High impedance buffers.

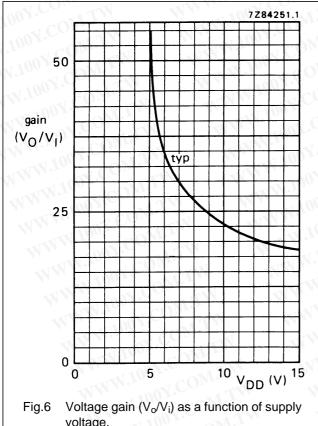

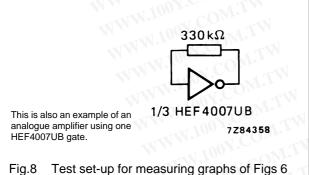

voltage.

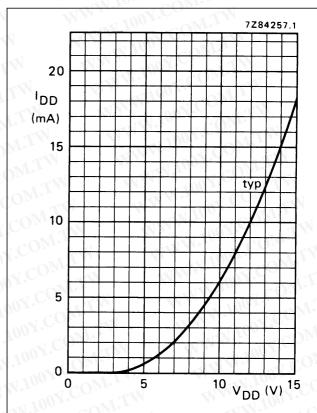

Supply current as a function of supply voltage.

and 7.

# HEF4007UB gates

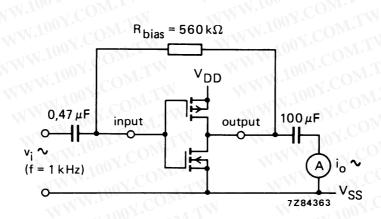

Fig.9 Test set-up for measuring forward transconductance  $g_{fs} = di_0/dv_i$  at  $v_0$  is constant (see also graph Fig.10).

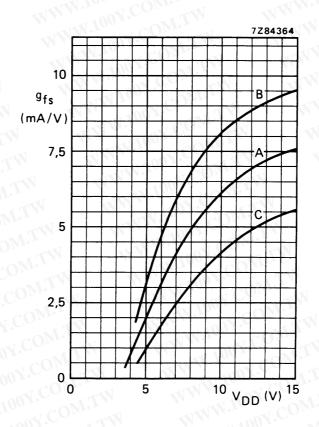

- A: average,

- B: average + 2 s,

- C: average 2 s, in where 's' is the observed standard deviation.

Fig.10 Typical forward transconductance  $g_{fs}$  as a function of the supply voltage at  $T_{amb}$  = 25 °C.

Philips Semiconductors Product specification

## Dual complementary pair and inverter

HEF4007UB gates

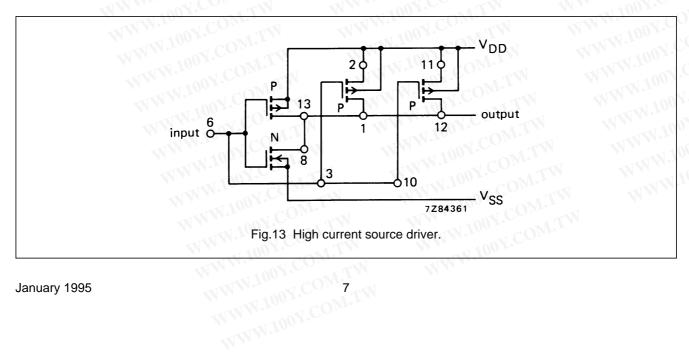

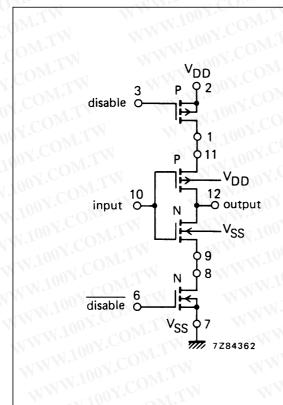

Figures 11 to 14 show some applications in which the HEF4007UB is used.

# HEF4007UB gates

Fig.14 High impedance buffer.

#### FUNCTION TABLE for Fig.14.

| INPUT   | INPUT DISABLE |      |

|---------|---------------|------|

| H 100   | CONLTW        | L    |

| WYL 100 | Y.CO. L.TW    | Н    |

| X       | V.CO'H        | open |

#### **Notes**

- H = HIGH state (the more positive voltage)

- L = LOW state (the less positive voltage)

- X = state is immaterial

#### NOTE

Rules for maintaining electrical isolation between transistors and monolithic substrate:

- Pin number 14 must be maintained at the most positive (or equally positive) potential with respect to any other pin of the HEF4007UB.

- Pin number 7 must be maintained at the most negative (or equally negative) potential with respect to any other pin of the HEF4007UB.

Violation of these rules will result in improper transistor operation and/or possible permanent damage to the HEF4007UB.

WWW.100Y.CON