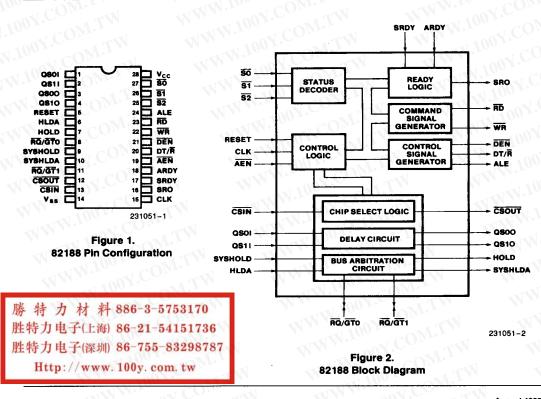

# 82188 INTEGRATED BUS CONTROLLER FOR 8086, 8088, 80186, 80188 PROCESSORS

Provides Flexibility in System Configurations

intal

- Supports 8087 Math Coprocessor in 8 MHz 80186 and 80188 Systems

- Provides a Low-cost Interface for 8086, 8088 Systems to an 82586 LAN Coprocessor or 82730 Text Coprocessor

- Facilitates interface to one or more Multimaster Busses

- Supports Multiprocessor, Local Bus Systems

- Allows use of 80186/80188 Highintegration Features

- 3-State, Command Output Drivers

- Available in EXPRESS — Standard Temperature Range — Extended Temperature Range

- Available in Plastic DIP or Cerdip Package

(See Packaging Outlines and Dimensions, Order #231369)

The 82188 Integrated Bus Controller (IBC) is a 28-pin HMOS III component for use with 80186, 80186, 8086 and 8088 systems. The IBC provides command and control timing signals plus a configurable  $\overline{RQ}/\overline{GT} \leftrightarrow$  HOLD-HLDA converter. The device may be used to interface an 8087 Math Coprocessor with an 80186 or 80188 Processor. Also, an 82586 Local Area Network (LAN) Coprocessor or 82730 Text Coprocessor may be interfaced to an 8086 or 8088 with the IBC.

August 1989 Order Number: 231051-005

10Y.COM.TW

## **PIN DESCRIPTIONS**

| Symbol         | Pin No.              | Туре                                                                     | WT.M                                                                                            | Nar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ne and Funct                         | tion                                                                                                                                                   |  |  |

|----------------|----------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 50<br>S1<br>S2 | 27<br>26<br>25       | 100 <sup>1</sup> X.C<br>1.100 <sup>1</sup> X.C<br>1.100 <sup>1</sup> X.C | S0-S2 corre<br>The 82188 u<br>bus cycles. T<br>control signa<br>SRO line dur<br>input on all th | Status Input Pins<br>$\overline{S0}$ - $\overline{S2}$ correspond to the status pins of the CPU.<br>The 82188 uses the status lines to detect and identify the processor<br>bus cycles. The 82188 decodes $\overline{S0}$ - $\overline{S2}$ to generate the command and<br>control signals. $\overline{S0}$ - $\overline{S2}$ are also used to insert 3 wait states into the<br>SRO line during the first 256 80186 bus cycles after RESET. A HIGH<br>input on all three lines indicates that no bus activity is taking place.<br>The status input lines contain weak internal pull-up devices. |                                      |                                                                                                                                                        |  |  |

|                | W                    | 111.10                                                                   | <u>52</u>                                                                                       | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SO                                   | Bus Cycle Initiated                                                                                                                                    |  |  |

|                | 7                    | MMM<br>MMM<br>MMM                                                        | 0<br>0<br>0<br>1<br>1<br>1<br>1                                                                 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | interrupt acknowledge<br>read I/O<br>write I/O<br>halt<br>instruction fetch<br>read data from memory<br>write data to memory<br>passive (no bus cycle) |  |  |

| CLK            | 15                   | WW<br>WW                                                                 |                                                                                                 | CLK is the clock signal generated by the CPU or clock generator device. CLK edges establish when signals are sampled and                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |                                                                                                                                                        |  |  |

| RESET          | 5<br>1.1<br>M.1<br>W |                                                                          | signal. The s<br>enabling the<br>SRO signal o<br>determined o                                   | <b>RESET</b><br>RESET is a level triggered signal that corresponds to the system reset<br>signal. The signal initializes an internal bus cycle counter, thus<br>enabling the 82188 to insert internally generated wait states into the<br>SRO signal during system initialization. The 82188 mode is also<br>determined during RESET. RD, WR, and DEN are driven HIGH during<br>RESET regardless of AEN. RESET is active HIGH.                                                                                                                                                                  |                                      |                                                                                                                                                        |  |  |

| AEN            | 19                   | 1 1<br>7<br>7                                                            | This signal e<br>inactive (HIG<br>driven LOW                                                    | Address Enable<br>This signal enables the system command lines when active. If $\overline{\text{AEN}}$ is<br>inactive (HIGH), RD, WR, and DEN will be tri-stated and ALE will be<br>driven LOW (DT/R will not be effected). $\overline{\text{AEN}}$ is an asynchronous<br>signal and is active LOW.                                                                                                                                                                                                                                                                                             |                                      |                                                                                                                                                        |  |  |

| ALE            | 24                   | 0                                                                        | active HIGH                                                                                     | used to strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | d occur on the                       | to address latches. ALE is<br>HIGH to LOW transition.<br>-type latches.                                                                                |  |  |

| DEN            | 21                   | 0                                                                        | This signal is<br>local or syste                                                                | <b>Data Enable</b><br>This signal is used to enable data transceivers located on either the<br>local or system data bus. The signal is active LOW. DEN is tri-stated<br>when AEN is inactive.                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                                                                                                                                                        |  |  |

| DT/R           | 20                   | 0                                                                        | This signal e<br>transceivers.                                                                  | A HIGH on this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | irection of dat<br>line indicates    | a flow through the data<br>TRANSMIT (write to I/O or<br>Read from I/O or memory).                                                                      |  |  |

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw 100Y.COM.TW

24-813

# PIN DESCRIPTIONS (Continued)

| Symbol           | Pin No.                                                | Туре                     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD               | 23                                                     | I.COM                    | <b>READ</b><br>This signal instructs an I/O or memory device to drive its<br>data onto the data bus. The RD signal is similiar to the<br>RD signal of the 80186(80188) in Non-Queue-Status<br>Mode. RD is active LOW and is tri-stated when AEN is<br>inactive.                                                                                                                                                                                                           |

| WA               | 22                                                     | 0050<br>1003.CC          | WRITE<br>This signal instructs an I/O or memory device to record<br>the data presented on the data bus. The WR signal is<br>similiar to the WR signal of the 80186(80188) in Non-<br>Queue-Status Mode. WR is active LOW and is tri-stated<br>when AEN is inactive.                                                                                                                                                                                                       |

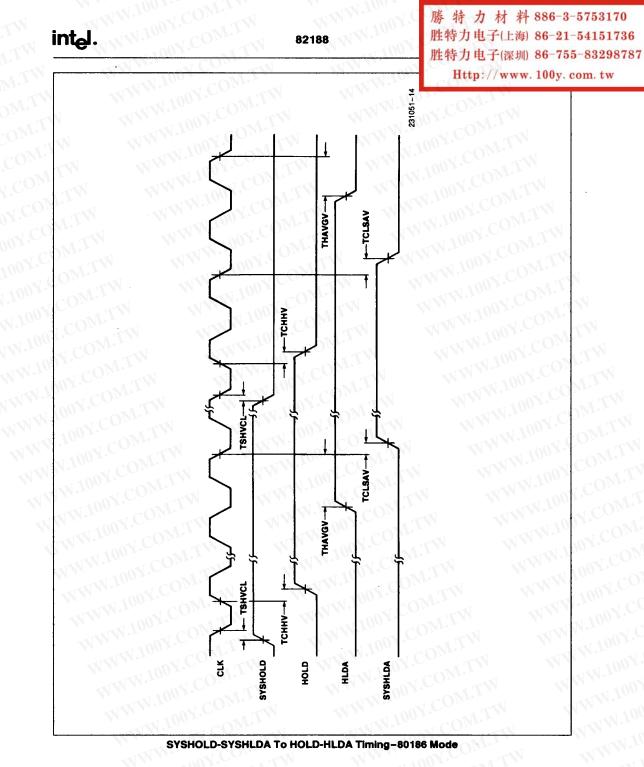

| HOLD             | 7                                                      | 0                        | HOLD<br>The HOLD signal is used to request bus control from the<br>80186 or 80188. The request can come from either the<br>8087 (RQ/GTO) or from the third processor (SYSHOLD).<br>The signal is active HIGH.                                                                                                                                                                                                                                                             |

| HLDA             | 6                                                      | MMM<br>MMM<br>MMM<br>MMM | HOLD Acknowledge<br>80186 MODE-This line serves to translate the HLDA<br>output of the 80186(80188) to the appropriate signal of<br>the device requesting the bus. HLDA going active (HIGH)<br>indicates that the 80186 has relinquished the bus. If the<br>requesting device is the 8087, HLDA will be translated<br>into the grant pulse of the RQ/GTO line. If the<br>requesting device is the optional third processor, HLDA<br>will be routed into the SYSHLDA line. |

|                  | M.TW<br>M.TW                                           | WW Y                     | This pin also determines the mode in which the 82188 will operate. If this line is HIGH during the falling edge of RESET, the 82188 will enter the 8086 mode. If LOW, the 82188 will enter the 80186 mode. For 8086 mode, this pin should be strapped to $V_{\rm CC}$ .                                                                                                                                                                                                   |

| RQ/GTO           | DM 8<br>COM.TW<br>COM.TW                               | 1/0                      | <b>Request/Grant O</b><br>$\overline{RQ}/\overline{GTO}$ is connected to $\overline{RQ}/\overline{GTO}$ of the 8087 Numeric.<br>Coprocessor. When initiated by the 8087, $\overline{RQ}/\overline{GTO}$ will<br>be translated to HOLD-HLDA to acquire the bus from the<br>80186(80188). This line is bidirectional, and is active<br>LOW. $\overline{RQ}/\overline{GTO}$ has a weak internal pull-up device to<br>prevent erroneous request/grant signals.                |

| RQ/GT1           | NCOM                                                   | 1/0                      | Request/Grant 1<br>80186 Mode–In 80186 Mode, RQ/GT1 allows a third<br>processor to take control of the local bus when the 8087<br>has bus control. For a HOLD-HLDA type third processor,<br>the 82188's RQ/GT1 line should be connected to the                                                                                                                                                                                                                            |

| 电子(上海)<br>电子(深圳) | 886-3-5753<br>86-21-5415<br>86-755-832<br>100y. com. t | 1736<br>98787            | RQ/GT1 line of the 8087.<br>8086 MODE – In 8086 Mode, RQ/GT1 is connected to<br>either RQ/GT0 or RQ/GT1 of the 8086. RQ/GT1 will<br>start its request/grant sequence when the SYSHOLD<br>line goes active. In 8086 Mode, RQ/GT1 is used to gain<br>bus control from the 8086 or 8088.<br>RQ/GT1 is a bidirectional line and is active LOW. This                                                                                                                           |

|                  | W.100Y                                                 | COM.                     | RQ/GT1 is a bidirectional line and is active LOW. This<br>line has a weak internal pull-up device to prevent<br>erroneous request/grant signals.                                                                                                                                                                                                                                                                                                                          |

# PIN DESCRIPTIONS (Continued)

| Symbol       | Pin No.                      | Туре              | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSHOLD      | 9,000                        | K.COM             | System Hold<br>80186 MODE-SYSHOLD serves as a hold input for an<br>optional third processor in an 80186(80188)-8087 system.<br>If the 80186(80188) has bus control, SYSHOLD will be<br>routed to HOLD to gain control of the bus. If the 8087 has<br>bus control, SYSHOLD will be translated to RQ/GT1 to<br>gain control of the bus.                                                                                                                                          |

|              | WWW.                         | 100X.CC           | 8086 MODE-SYSHOLD serves as a hold input for a coprocessor in an 8086 or 8088 system. SYSHOLD is translated to RQ/GT1 of the 82188 to allow the coprocessor to take control of the bus.                                                                                                                                                                                                                                                                                        |

| WT A         | N. V.                        | 1 100Y.           | SYSHOLD may be an asynchronous signal.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYSHLDA      | 10                           | 0                 | System Hold Acknowledge<br>SYSHLDA serves as a hold acknowledge line to the<br>processor or coprocessor connected to it. The device<br>connected to the SYSHOLD-SYSHLDA lines is allowed<br>the bus when SYSHLDA goes active (HIGH).                                                                                                                                                                                                                                           |

| SRDY         | 17                           | WWW<br>WWW<br>WWW | Synchronous Ready<br>The SRDY input serves the same function as SRDY of the<br>80186(80188). The 82188 combines SRDY with ARDY to<br>form a synchronized ready output signal (SRO). SRDY<br>must be synchronized external to the 82188 and is active<br>HIGH. If tied to $V_{CC}$ , SRO will remain active (HIGH) after<br>the first 256 80186 cycles following RESET. If only ARDY<br>is to be used, SRDY should be tied LOW.                                                 |

| ARDY         | A 18<br>M.TW<br>M.TW<br>M.TW | 4 4 4 A           | Asynchronous Ready<br>The ARDY input serves the same function as ARDY of the<br>80186(80188). ARDY may be an asynchronous input, and<br>is active HIGH. Only the rising edge of ARDY is<br>synchronized by the 82188. The falling edge must be<br>synchronized external to the 82188. If connected to V <sub>CC</sub> ,<br>SRO will remain active (HIGH) after the first 256 80186<br>bus cycles following RESET. If only SRDY is to be used,<br>ARDY should be connected LOW. |

| SRO          | CO 16<br>COM 1<br>COM 1      | 0                 | Synchronous READY Output<br>SRO provides a synchronized READY signal which may<br>be interfaced directly with the SRDY of the 80186(80188)<br>and READY of the 8087. The SRO signal is an<br>accumulation of the synchronized ARDY signal, the SRDY<br>signal, and the internally generated wait state signal.                                                                                                                                                                 |

| QS0I<br>QS1I | 1 2                          | WT.N              | Queue-Status Inputs<br>QS0I, QS1I are connected to the Queue-Status lines of<br>the 80186(80188) to allow synchronization of the queue-<br>status signals to 8087 timing requirements.                                                                                                                                                                                                                                                                                         |

| QS00<br>QS10 | 3 4                          | 0                 | Queue-Status Outputs<br>QSOO, QS1O are connected to the queue-status pins of<br>the 8087. The signals produced meet 8087 Queue-Status<br>input requirements.                                                                                                                                                                                                                                                                                                                   |

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

WWW.100Y.COM.TW

intel.

胜特力电子(上海) 86-21-54151736

勝特力材料 886-3-5753170

胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

| Symbol | Pin No. | Туре                       | Name and Function                                                                                                                                                                                                                                                                                                                                              |

|--------|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSIN   | 13      | 100X.C<br>(.100X<br>(.100X | Chip-Select Input<br>CSIN is connected to one of the chip-select lines of the<br>80186(80188). CSIN informs the 82188 that a bank select is taking<br>place. The 82188 routes this signal to the chip-select output<br>(CSOUT). CSIN is active LOW. This line is not used when memory<br>and I/O device addresses are decoded external to the<br>80186(80188). |

| CSOUT  | 12      | 0                          | Chip-Select Output<br>This signal is used as a chip-select line for a bank of memory devices<br>It is active when CSIN is active or when the 8087 has bus control.<br>CSOUT is active LOW.                                                                                                                                                                     |

# FUNCTIONAL DESCRIPTION

PIN DESCRIPTIONS (Continued)

#### BUS CONTROLLER

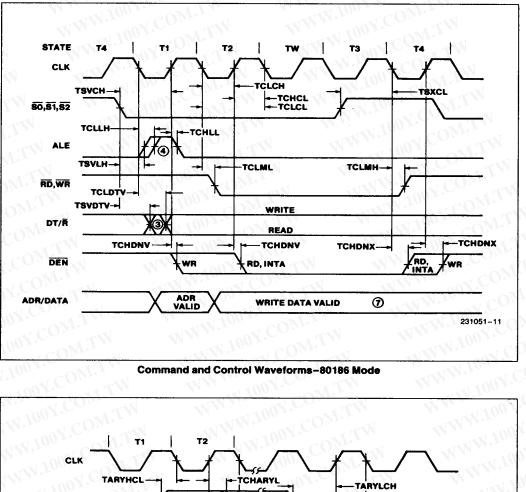

The 82188 Integrated Bus Controller (IBC) generates system control and command signals. The signals generated are determined by the Status Decoding Logic. The bus controller logic interprets status lines  $\overline{S0}-\overline{S2}$  to determine what type of bus cycle is taking place. The appropriate signals are then generated by the Command and Control Signal Generators.

The Address Enable (AEN) line allows the command and control signals to be disabled. When AEN is inactive (HIGH), the command signals and DEN will be tri-stated, and ALE will be held low (DT/R will be uneffected). AEN inactive will allow other systems to take control of the bus. Control and command signals respond to a change in the AEN signal within 40 ns.

The command signals consist of  $\overline{RD}$  and  $\overline{WR}$ . The 82188's  $\overline{RD}$  and  $\overline{WR}$  signals are similiar to  $\overline{RD}$  and  $\overline{WR}$  of the 80186(80188) in the non-Queue-Status Mode. These command signals do not differentiate between memory and I/O devices.  $\overline{RD}$  and  $\overline{WR}$  can be conditioned by  $\overline{S2}$  of the 80186(80188) to obtain separate signals for I/O and memory devices.  $\overline{RD}$  is asserted during INTA cycles, unlike  $\overline{RD}$  on the 80186(80188).

The control commands consist of Data Enable (DEN), Data Transmit/Receive (DT/ $\overline{R}$ ), and Address Latch Enable (ALE). The control commands are similiar to those generated by the 80186(80188). DEN determines when the external bus should be enabled onto the local bus. DT/ $\overline{R}$  determines the direction of the data transfer, and ALE determines when the address should be strobed into the latches (used for demultiplexing the address bus). DT/ $\overline{R}$  does not go to an inactive (high) state at the end of bus ustrobed, unlike DT/ $\overline{R}$  on the 80186(80188).

#### MODE SELECT

The 82188 Integrated Bus Controller (IBC) is configurable. The device has two modes: 80186 Mode and 8086 Mode. Selecting the mode of the device configures the Bus Arbitration Logic (see BUS ARBI-TRATION section for details). In 80186 Mode, the 82188 IBC may be used as a bus controller/interface device for an 80186(80188), 8087, and optional third processor system. In 8086 Mode, the 82188 IBC may be used as an interface device allowing a maximum mode 8086(8088) to interface with a coprocessor that uses a HOLD-HLDA bus exchange protocol.

The mode of the 82188 is determined during RE-SET. If the HLDA line is LOW at the falling edge of RESET (as in the case when tied to the HLDA line of the 80186 or 80188), the 82188 will enter into 80186 Mode. If the HLDA line is HIGH at the falling edge of RESET, the 82188 will enter 8086 Mode. In 8086 Mode, only the Bus Arbitration Logic is used. The eight pins used in 8086 Mode are: SYSHOLD, SYSHLDA, HLDA, CLK, RESET, RQ/GT1, V<sub>CC</sub>, and V<sub>SS</sub>. The other pins may be left unconnected.

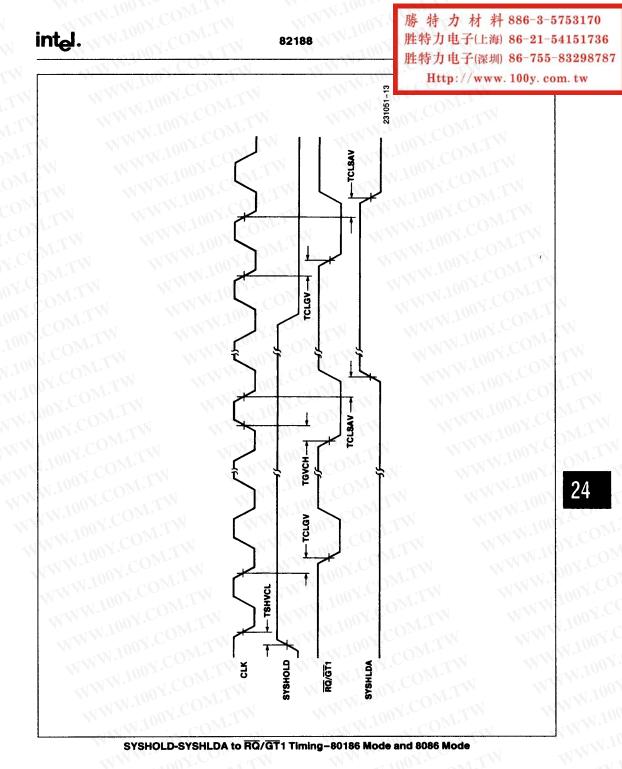

#### **BUS ARBITRATION**

The Bus Exchange Logic interfaces up to three sets of bus exchange signals:

- HOLD-HLDA

- SYSHOLD-SYSHLDA

- RQ/GT0 (RQ/GT1)

This logic executes translating, routing, and arbitrating functions. The logic translates HOLD-HLDA signals to  $\overline{RQ}/\overline{GT}$  signals and  $\overline{RQ}/\overline{GT}$  signals to HOLD-HLDA signals. The logic also determines which set of bus exchange signals are to be interfaced. The mode of the 82188 and the priority of the devices requesting the bus determine the routing of the bus exchange signals.

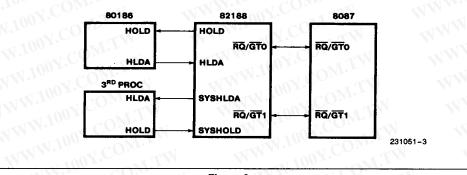

#### 80186 MODE

In 80186 Mode, a system may have three potential bus masters: the 80186 or 80188 CPU, the 8087 Numerics Coprocessor, and a third processor (such as the 82586 LAN or 82730 Text Coprocessor). The third processor may have either a HOLD-HLDA or  $\overline{RQ}/\overline{GT}$  bus exchange protocol. The possible bus exchange signal connections and paths for 80186 Mode are shown in Figures 3 & 4 and Tables 1 & 2, respectively. If no HOLD-HLDA type third processor is used, SYSHOLD should be tied LOW to prevent an erroneous SYSHOLD signal. In 80186 mode, the bus priorities are:

| Highest Priority        | . Third Processor |

|-------------------------|-------------------|

| Second Highest Priority |                   |

| Default Priority        |                   |

#### - THREE-PROCESSOR SYSTEM OPERATION (HOLD-HLDA TYPE THIRD PROCESSOR)

In the configuration shown in Figure 3, the third processor requests the bus by sending SYSHOLD HIGH. The 82188 will route (and translate if necessary) the request to the current bus master. This includes routing the request to HOLD if the 80186(80188) is the current bus master or routing and translating the request to  $\overline{RQ}/\overline{GT1}$  if the 8087 is in control of the bus. The third processor's request is not passed through the 8087 if the 80186 is the bus master (see Table 1).

The 8087 requests the bus using  $\overline{RQ}/\overline{GT0}$ . The request pulse from the 8087 will be translated and routed to HOLD if the 80186 is the bus master. If the third processor has control of the bus, the grant pulse to the 8087 will be delayed until the third processor relinquishes the bus (sending SYSHOLD LOW). In this case, HOLD will remain HIGH during the third processor-to-8087 bus control transfer. The 80186 will not be granted the bus until both coprocessors have released it.

#### Table 1. Bus Exchange Paths (80186 Mode) (HOLD-HLDA Type 3rd Proc)

| Requesting | Current Bus Master                                                                                                                                                                      |                                                                                                        |          |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Device     | 80186                                                                                                                                                                                   | 8087                                                                                                   | 3rd Proc |  |  |  |

| 80186      | n/a                                                                                                                                                                                     | n/a                                                                                                    | n/a      |  |  |  |

| 8087       | $\overline{RQ}/\overline{GT}0 \longleftrightarrow \frac{HOLD}{HLDA}$                                                                                                                    | n/a                                                                                                    | n/a      |  |  |  |

| 3rd Proc   | $\xrightarrow{\text{SYSHOLD}} \longleftrightarrow \xrightarrow{\text{HOLD}} \\ \xrightarrow{\text{SYSHLDA}} \longleftrightarrow \xrightarrow{\text{HOLD}} \\ \xrightarrow{\text{HLDA}}$ | $\frac{\text{SYSHOLD}}{\text{SYSHLDA}} \longleftrightarrow \overline{\text{RQ}}/\overline{\text{GT}}1$ | n/a      |  |  |  |

Figure 3.

Bus Exchange Signal Connections (80186 Mode) for a Three Local Processor System

(HOLD-HLDA Type 3rd Proc)

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

24-817

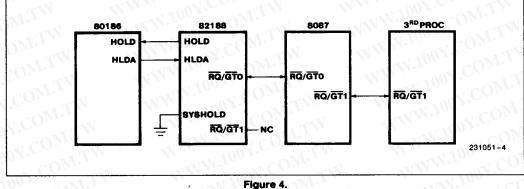

24

| Requesting | Current Bus Master                                                                                                    |        |          |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------|--------|----------|--|--|

| Device     | 80186                                                                                                                 | 8087   | 3rd Proc |  |  |

| 80186      | n/a                                                                                                                   | n/a    | n/a      |  |  |

| 8087       | RQ/GT0 ↔ HOLD<br>HLDA                                                                                                 | n/a    | n/a      |  |  |

| 3rd Proc   | $\overline{RQ}/\overline{GT}1 \longleftrightarrow \overline{RQ}/\overline{GT}0 \longleftrightarrow \frac{HOLD}{HLDA}$ | RQ/GT1 | n/a      |  |  |

Table 2. Bus Exchange Paths (80186 Mode) (RQ/GT Type 3rd Proc)

Bus Exchange Signal Connections (80186 Mode) for a Three Local Processor System (RQ/GT Type 3rd Proc)

When the bus is requested from the 80186(80188), a bus priority decision is made. This decision is made when the HLDA line goes active. Upon receipt of the HLDA signal, the highest-priority requesting device will be acknowledged the bus. For example, if the 8087 initially requested the bus, the bus will be granted to the third processor if SYSHOLD became active before HLDA was received by the 82188. In this case, the grant pulse to the 8087 will be delayed until the third processor relinquishes the bus.

#### THREE-PROCESSOR SYSTEM OPERATION (RQ/GT TYPE THIRD PROCESSOR)

In the configuration shown in Figure 4, the third processor requests the bus by initiating a request/grant sequence with the 8087's  $\overline{RQ}/\overline{GT1}$  line. The 8087 will grant the bus if it is the current bus master or will pass the request on if the 80186 is the current bus master (see Table 2). In this configuration, the 82188's Bus Arbitration Logic translates  $\overline{RQ}/\overline{GT0}$  to HOLD-HLDA. The 8087 provides the bus arbitration in this configuration.

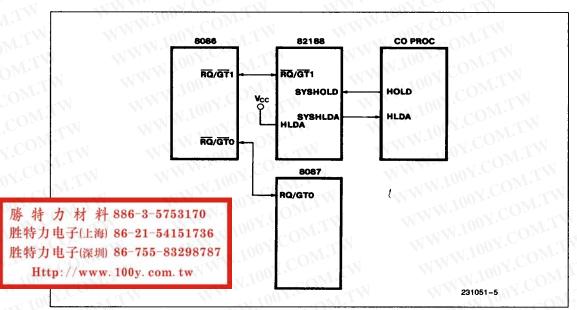

#### 8086 MODE

The 8086 Mode allows an 8086, 8088 system to contain both RQ/GT and HOLD-HLDA type coprocessors simultaneously. In 8086 Mode, two possible bus masters may be interfaced by the 82188; an 8086 or 8088 CPU and a coprocessor which uses a HOLD-HLDA bus exchange protocol (typically an 82586 LAN Coprocessor or an 82730 Text Coprocessor). The bus exchange signal connections for 8086 Mode are shown in Figure 5. Bus arbitration signals used in the 8086 Mode are:

- RQ/GT1

- SYSHOLD

- SYSHLDA

In 8086 Mode, no arbitration is necessary since only two devices are interfaced. The coprocessor has bus priority over the 8086(8088). SYSHOLD-SYSHLDA are routed and translated directly to  $\overline{RQ}/GT1$ .  $\overline{RQ}/\overline{GT1}$  of the 82188 may be tied to either  $\overline{RQ}/\overline{GT0}$  or  $\overline{RQ}/\overline{GT1}$  of the 8086(8088).

> 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

> > Http://www.100y.com.tw

intel.

Figure 5. Bus Exchange Signal Connections (8086 Mode)

# QUEUE-STATUS DELAY

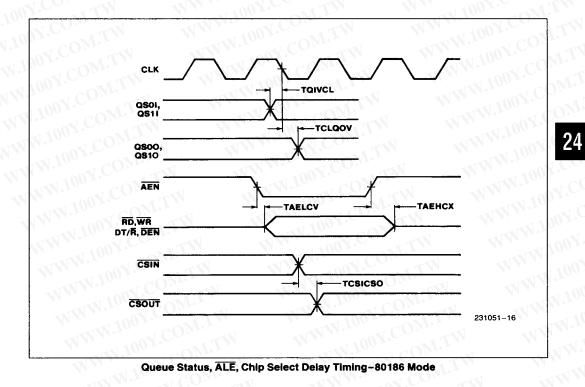

The Queue-Status Delay logic is used to delay the queue-status signals from the 80186(80188) to meet 8087 queue-status timing requirements. QSOI, QS11 correspond to the queue-status lines of the 80186(80188). The 82188 delays these signals by one clock phase. The delayed signals are interfaced to the 8087 queue-status lines by QS00, QS10.

#### CHIP-SELECT

The Chip-Select Logic allows the utilization of the chip select circuitry of the 80186(80188). Normally, this circuitry could not be used in an 80186(80188). 8087 system since the 8087 contains no chip select circuitry. The Chip-Select Logic contains two external connections: Chip-Select Input (CSIN) and Chip-Select Output (CSOUT). CSOUT is active when either CSIN is active or when the 8087 has control of the bus.

By using CSOUT to select memory containing data structures, no external decoding is necessary. The 80186 may gain access to this memory bank through the CSIN line while the 8087 will automatically obtain access when it becomes the bus master. Note that this configuration limits the amount of memory accessible by the 8087 to the physical memory bank selected by CSOUT. Systems where the 8087 must access the full 1 Megabyte address space must use an external decoding scheme.

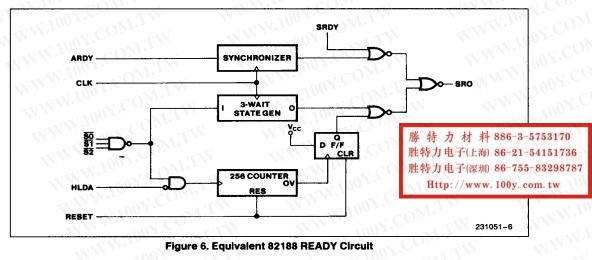

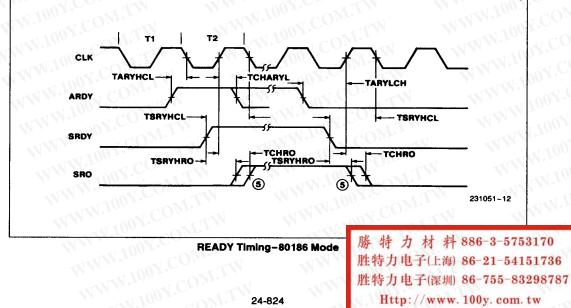

# READY

The Ready logic allows two types of Ready signals: a Synchronous Ready Signal (SRDY) and an Asynchronous Ready Signal (ARDY). These signals are similiar to SRDY and ARDY of the 80186. Wait states will be inserted when both SRDY and ARDY are LOW. Inserting wait states allows slower memory and I/O devices to be interfaced to the 80186(80188)-8087 system.

24

ARDY's LOW-to-HIGH transition is synchronized to the CPU clock by the 82188. The 82188 samples ARDY at the beginning of T2, T3 and Tw until sampled HIGH. Note that ARDY of the 82188 is sampled one phase earlier than ARDY of the 80186. ARDY's falling edge must be synchronous to the CPU clock. ARDY allows an easy interface with devices that emit an asynchronous ready signal.

The SRDY signal allows direct interface to devices that emit a synchronized ready signal. SRDY must be synchronized to the CPU clock for both of its transitions. SRDY is sampled in the middle of T2, T3 and in the middle of each Tw. An 82188-80186(80188)'s SRDY setup time is 30 ns longer than the 80186(80188)'s SRDY setup time. SRDY eliminates the half-clock cycle penalty necessary for ARDY to be internally sychronized.

The sychronized ready output (SRO) is the accumulation of SRDY, ARDY, and the internal wait-state

generator. SRO should be connected to SRDY of the 80186(80188) (with 80186(80188)'s ARDY tied LOW), and READY of the 8087.

| SRDY | ARDY | SRO |

|------|------|-----|

| 0    | 0    | 0   |

| 1    | X    | 1   |

| X    | 1.1  | 01. |

The internal wait state generator allows for synchronization between the 80186(80188) and 8087 in 80186 mode. Upon RESET, the 82188 automatically inserts 3 wait-states per 80186(80188) bus cycle, overlapped with any externally produced wait-states created by ARDY and SRDY.

Since the 8087 has no provision for internal waitstate generation, only externally created wait states will be effective. The 82188, upon RESET, will inject 3 wait states for each of the first 256 80186(80188) bus cycles onto the SRO line. This will allow the 8087 to match the 80186(80188)'s timing.

The internally-generated wait states are overlapped with those produced by the SRDY and ARDY lines. Overlapping the injected wait states insures a minimum of three wait states for the first 256 80186(80188) bus cycles after RESET. Systems with a greater number of wait states will not be affected. Internal wait state generation by the 82188 will stop on the 256th 80186(80188) bus cycle after RESET. To maintain sychronization between the 80186(80188) and 8087, the following conditions are necessary:

The 80186(80188)'s control block must be mapped in I/O space before it is written to or read from.  All memory chip-select lines must be set to 0 WAIT STATES, EXTERNAL READY ALSO USED within the first 256 80186(80188) bus cycles after RESET.

An equivalent READY logic diagram is shown in Figure 6.

# SYSTEM CONSIDERATIONS

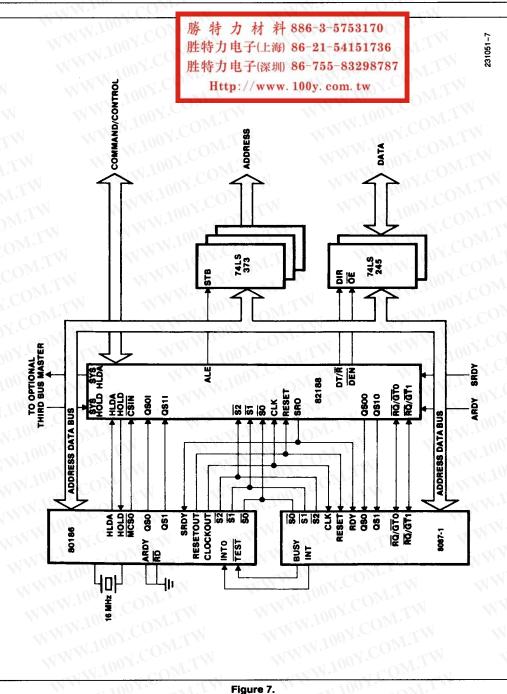

In any 82188 configuration, clock compatibility must be considered. Depending on the device, a 50% or a 33% duty-cycle clock is needed. For example, the 80186 and 80188 (as well as the 82188, 82586, and 82730) requires a 50% duty-cycle clock. The 8086, 8088 and their 'kit' devices' (8087, 8089, 82C88, and 8289) clock requirements, on the other hand, require a 33% duty-cycle clock signal. The system designer must make sure clock requirements of all the devices in the system are met.

Figure 7 demonstrates the usage of the 82188 in 80186 Mode where it is used to interface an 8087 into an 80186 system. In this case, the clock requirements of the 8087 are met by specifying the 10 MHz (8087-1) device, but clocking the system at a maximum rate of 8 MHz.

Status bit six (S6) from the main processor (8086, 8088, 80186, or 80188) is used by the 8087 to track the instruction flow. S6 is multiplexed with address bit 19 (A19). If the third processor generates only 16 bits of address, S6 is not generated. A19/S6 must be driven high by external circuitry during the status portion of bus cycles controlled by the third processor.

24-820

int<sub>e</sub>l.

Figure 7. 80186/8087-1 System Using the 82188 in 80186 Mode 24-821

This Material Copyrighted By Its Respective Manufacturer

24

# **ABSOLUTE MAXIMUM RATINGS \***

| Temperature Under Bias  | 0°C to 70°C    |

|-------------------------|----------------|

| Storage Temperature     | 65°C to 150°C  |

| Case Temperature        | 0°C to +85°C   |

| Voltage on any Pin with |                |

| Respect to GND          | – 1.0V to 7.0V |

| Power Dissipation       |                |

#### **DC CHARACTERISTICS**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C, T_{CASE} = 0^{\circ}C \text{ to } +85^{\circ}C)$

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| Symbol           | Parameter              | Min     | Max                   | Units | Test Cond.                     |

|------------------|------------------------|---------|-----------------------|-------|--------------------------------|

| VIL              | Input Low Voltage      | -0.5    | + 0.8                 | volts | VI. M. VO                      |

| VIH              | Input High Voltage     | 2.0     | V <sub>CC</sub> + 0.5 | volts | N.COm                          |

| VOL              | Output Low Voltage     | coM.    | 0.45                  | volts | $I_{OL} = 2  \text{mA}$        |

| V <sub>OH</sub>  | Output High Voltage    | 2.4     | IN                    | volts | $I_{OH} = -400 \mu A$          |

| Icc              | Power Supply Current   | V.COm   | 100                   | mA    | T <sub>A</sub> = 25°C          |

| J <sub>LI</sub>  | Input Leakage Current  | [00]    | ±10                   | μΑ    | OV <vin<vcc< td=""></vin<vcc<> |

| LO               | Output Leakage Current | 01.0    | ±10                   | μA    | 0.45 < VOUT < VCC              |

| V <sub>CLI</sub> | CLK Input Low Voltage  | -0.5    | + 0.6                 | volts | 1001.00                        |

| VCHI             | CLK Input High Voltage | 3.9     | V <sub>CC</sub> + 1.0 | volts | NN. SV.CC                      |

| CIN              | Input Capacitance      | 100 1.  | 10                    | pF    | .100 C                         |

| CIO              | I/O Capacitance        | . 100Y. | 20                    | pF    | 1002.                          |

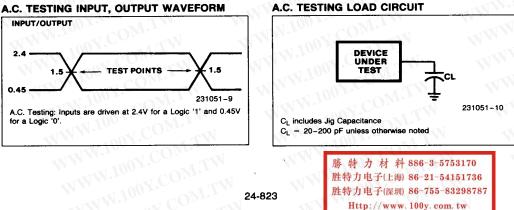

# **AC CHARACTERISTICS**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C, T_{CASE} = 0^{\circ}C \text{ to } +85^{\circ}C)$

## TIMING REQUIREMENTS

| Symbol  | Parameter                       | Min          | Max       | Units | Notes |

|---------|---------------------------------|--------------|-----------|-------|-------|

| TCLCL   | Clock Period                    | 125          | 500       | ns    |       |

| TCLCH   | Clock LOW Time                  | 1/2TCLCL-7.5 | -         | ns    | NN.   |

| TCHCL   | Clock HIGH Time                 | 1/2TCLCL-7.5 | In        | ns    | N.    |

| TARYHCL | ARDY Active Setup Time          | 20           | WT.       | ns    | 111   |

| TCHARYL | ARDY Hold Time                  | 15 0         |           | ns    | 8     |

| TARYLCH | ARDY Inactive Setup Time        | 35           | $M_{1,1}$ | ns    |       |

| TSRYHCL | SRDY Input Setup Time           | 65,50        | TIM       | ns    |       |

| TSVCH   | STATUS Active Setup Time        | 55           | )n-       | 🔨 ns  | W     |

| TSXCL   | STATUS Inactive Setup Time      | 50           | OM        | ns    |       |

| TQIVCL  | QS0I, QS1I Setup Time           | 15           | Mo        | ns    |       |

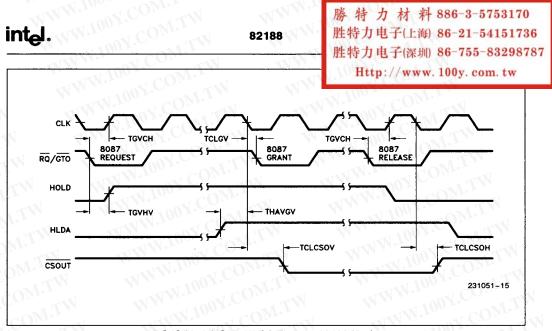

| THAVGV  | HLDA Setup Time                 | 50           |           | ns    |       |

| TSHVCL  | SYSHOLD Asynchronous Setup Time | 25           |           | ns    |       |

| TGVCH   | RQ/GT Input Setup Time          | 01100        |           | ns    | 6     |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

| Symbol  | Parameter                       | Min   | Max | Units | Notes  |

|---------|---------------------------------|-------|-----|-------|--------|

| TSVLH   | STATUS Valid to ALE Delay       | NN.   | 30  | ns    | 4      |

| TCHLL   | ALE Inactive Delay              | WIN   | 30  | ns    |        |

| TCLML   | RD, WR Active Delay             | 10    | 70  | ns    | -1     |

| TCLMH   | RD, WR Inactive Delay           | 10    | 55  | ns    | L.M.   |

| TSVDTV  | STATUS to DT/R Delay            | N     | 30  | ns    | 3      |

| TCLDTV  | DT/R Active Delay               |       | 55  | ns    | 3      |

| TCHDNV  | DEN Active Delay                | 10    | 55  | ns    |        |

| TCHDNX  | DEN Inactive Delay              | 10 🔨  | 55  | ns    | VT.    |

| TCLQOV  | QS0O, QS1O Delay                | 5     | 50  | ns    | DNT    |

| TCHHV   | HOLD Delay                      |       | 50  | ns    | 2,6    |

| TCLSAV  | SYSHLDA Delay                   |       | 50  | ns    | 6      |

| TCLGV   | RQ/GT Output Delay              | N/    | 40  | ns    | 6      |

| TGVHV   | RQ/GT0 To HOLD Delay            | 1     | 50  | ns    | 2,6    |

| TCLLH   | ALE Active Delay                | LN .  | 30  | ns    | 4      |

| TAELCV  | Command Enable Delay            | W     | 40  | ns    | N.CO.  |

| TAEHCX  | Command Disable Delay           |       | 40  | ns    | NT CO  |

| TCHRO   | SRO Output Delay                | 5     | 30  | ns    | 5,6    |

| TSRYHRO | SRDY To SRO Delay               | WT a  | 30  | ns    | 5      |

| TCSICSO | CSIN To CSOUT Delay             | DIVI- | 30  | ns    | No.    |

| TCLCSOV | CLK Low to CSOUT Delay          | 10    | -1  | ns    | 700 -  |

| TCLCSOH | CLK Low to CSOUT Inactive Delay | 10    |     | ns    | x11001 |

### DECONNEEC

NOTES (applicable to both spec listing and timing diagrams):

1. TSRYHOL = (80186's) TSRYCL + 30 ns = 65 ns for 6 MHz operation and 50 ns for 8 MHz operation.

- 2. Timing not tested.

- 3. DT/R will be asserted to the latest of TSVDTV & TCLDTV.

- 4. ALE will be asserted to the latest of TSVLH & TCLLH.

- 5. SRO will be asserted to the latest of TCHRO & TSRYHRO.

- 6. CL = 20-100 pF

- 7. Address/Data bus shown for reference only.

- 8. The falling edge of ARDY must be synchronized to CLK.

int<sub>e</sub>l.

82188

24-826

# int<sub>el</sub>.

# **REVISION HISTORY**

The sections significantly revised since version -004 are:

Bus Controller Added note describing RD during INTA and DT/R compared to the 80186/80188. System Considerations Use of 82188 with 80186 and 8087-1, all at 8 MHz, is clarified.

The sections significantly revised since version -002 are:

**AC Characteristics**

$T_{OIVCL}$  (min.) changed from 10 ns to 15 ns. Minimum timings for  $T_{CLML}, T_{CLMH}$ , and  $T_{CHDNV}$  changed from 0 ns to 10 ns.  $T_{CHDNX}$  (min.) changed from 5 ns to 10 ns. Minimum timings or  $T_{SVDTV}, T_{CLDTV}$ , and  $T_{CLLH}$  are no longer indicated (they were 0 ns).  $T_{CLCSOV}$  and  $T_{CLCSOH}$  added.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw