特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

PD-93839C

IRLR8503

## WWW.100Y.COM International **IOR**Rectifier

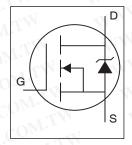

- N-Channel Application-Specific MOSFET

- Ideal for CPU Core DC-DC Converters

- Low Conduction Losses

- Minimizes Parallel MOSFETs for high current applications

- 100% R<sub>G</sub> Tested

#### Description

This new device employs advanced HEXFET Power MOSFET technology to achieve very low on-resistance. The reduced conduction losses makes it ideal for high efficiency DC-DC converters that power the latest generation of microprocessors.

The IRLR8503 has been optimized and is 100% tested for all parameters that are critical in synchronous buck converters including  $\rm R_{\rm DS(on)},$  gate charge and Cdv/dt-induced turn-on immunity. The IRLR8503 offers an extremely low combination of  $Q_{sw} \& R_{DS(on)}$  for reduced losses in control FET applications.

The package is designed for vapor phase, infra-red, convection, or wave soldering techniques. Power dissipation of greater than 2W is possible in a typical PCB mount application.

#### HEXFET<sup>®</sup> MOSFET for DC-DC Converters

#### **DEVICE RATINGS (MAX. Values)**

|                     | IRLR8503 |

|---------------------|----------|

| V <sub>DS</sub>     | 30V      |

| R <sub>DS(on)</sub> | 18 mΩ    |

| Q <sub>G</sub>      | 20 nC    |

| Q <sub>SW</sub>     | 8 nC     |

| Q <sub>OSS</sub>    | 29.5 nC  |

#### **Absolute Maximum Ratings**

| Absolute Maximum Ratings               | W                               | WWW.L                             | N.TW       | WWW   |  |

|----------------------------------------|---------------------------------|-----------------------------------|------------|-------|--|

| Parameter                              | Wm                              | Symbol                            | IRLR8503   | Units |  |

| Drain-Source Voltage                   |                                 | V <sub>DS</sub>                   | 30         | V     |  |

| Gate-Source Voltage                    | $V_{I,I,M}$                     | V <sub>GS</sub>                   | ±20        | v     |  |

| Continuous Drain or Source Current     | $T_{C} = 25^{\circ}C$           | WW                                | 44         | N.    |  |

| Continuous Drain of Source Current     | $T_{\rm C} = 90^{\circ}{\rm C}$ | D                                 | 32         | A     |  |

| Pulsed Drain Current ①                 |                                 | I <sub>DM</sub>                   | 196        |       |  |

| Provention T <sub>C</sub>              |                                 |                                   | 62         | w     |  |

| Power Dissipation (5)                  | $T_{\rm C} = 90^{\circ}{\rm C}$ | PD                                | 30         | vv    |  |

| Junction & Storage Temperature Range   |                                 | T <sub>J</sub> , T <sub>STG</sub> | -55 to 150 | °C    |  |

| Continuous Source Current (Body Diode) |                                 | I <sub>S</sub>                    | 15         | •     |  |

| Pulsed Source Current ①                |                                 | I <sub>SM</sub>                   | 196        | A     |  |

#### **Thermal Resistance**

| Thermal Resistance              |                     |     |     |       |  |  |  |

|---------------------------------|---------------------|-----|-----|-------|--|--|--|

| Parameter                       | Symbol              | Тур | Max | Units |  |  |  |

| Maximum Junction-to-Ambient 3 6 | R <sub>0JA</sub>    |     | 50  | °C/W  |  |  |  |

| Maximum Junction-to-Lead ©      | $R_{	ext{	heta}JL}$ |     | 2.0 | °C/W  |  |  |  |

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

## WWW.100Y.COM.TV WWW.100Y.COM **IRLR8503**

#### International **IOR**Rectifier

| Parameter                                            | Symbol               | Min      | Тур  | Max      | Units      | Conditions                                     |  |

|------------------------------------------------------|----------------------|----------|------|----------|------------|------------------------------------------------|--|

| Drain-to-Source Breadown Voltage*                    | V <sub>(BR)DSS</sub> | 30       | -    |          | V 🔨        | V <sub>GS</sub> = 0V, I <sub>D</sub> = 250µA   |  |

| Static Drain-Source On-Resistance*                   | R <sub>DS(on)</sub>  | 20       | 11   | 16       | mΩ         | V <sub>GS</sub> = 10V, I <sub>D</sub> = 15A ②  |  |

| Static Drain-Source On-Resistance                    |                      |          | 13   | 18       |            | V <sub>GS</sub> = 4.5V, 1 <sub>D</sub> = 15A   |  |

| Gate Threshold Voltage*                              | V <sub>GS(th)</sub>  | 1.0      | A    | 3.0      | V          | $V_{DS} = V_{GS}, I_D = 250 \mu A$             |  |

| Drain Source Lookage Current                         | 11                   | 07.      |      | 1.0      | μA         | $V_{DS} = 30V, V_{GS} = 0$                     |  |

| Drain-Source Leakage Current                         | DSS                  | and l    |      | 150      | ΠµΑ        | $V_{DS} = 24V, V_{GS} = 0, T_J = 100^{\circ}C$ |  |

| Gate-Source Leakage Current*                         | I <sub>GSS</sub>     |          | 4    | ±100     | nA         | V <sub>GS</sub> = ± 20V                        |  |

| Total Gate Charge, Control FET*                      | Qg                   | 100      | 15   | 20       |            | $V_{GS} = 5V, I_{D} = 15A, V_{DS} = 16V$       |  |

| Total Gate Charge, Synch FET*                        | Q <sub>g</sub>       | 10       | 13   | 17       |            | V <sub>GS</sub> = 5V, V <sub>DS</sub> < 100mV  |  |

| Pre-Vth Gate-to-Source Charge                        | Q <sub>gs1</sub>     |          | 3.7  |          |            | V <sub>DS</sub> = 16V, I <sub>D</sub> = 15A    |  |

| Post-Vth Gate-to-Source Charge                       | Q <sub>gs2</sub>     | <u> </u> | 1.3  | CO.      | nC         |                                                |  |

| Gate-to-Drain Charge                                 | Q <sub>gd</sub>      | N.       | 4.1  |          | Nr.        | $v_{\rm DS} = 10v$ , $i_{\rm D} = 15A$         |  |

| Switch Charge* (Q <sub>gs2</sub> + Q <sub>gd</sub> ) | Q <sub>SW</sub>      | 4        | 5.4  | 8        | DW.        |                                                |  |

| Output Charge*                                       | Q <sub>OSS</sub>     |          | 23   | 29.5     | M          | $V_{DS} = 16V, V_{GS} = 0$                     |  |

| Gate Resistance                                      | R <sub>G</sub>       | 0.4      |      | 1.1      | Ω          | TW WY                                          |  |

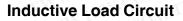

| Turn-On Delay Time                                   | t <sub>d(on)</sub>   | 4        | 10   |          | COF        | V <sub>DD</sub> = 16V, I <sub>D</sub> = 15A    |  |

| Drain Voltage Rise Time                              | tr <sub>v</sub>      |          | 18   |          | CO         | V <sub>GS</sub> = 5.0V                         |  |

| Turn-Off Delay Time                                  | t <sub>d(off)</sub>  |          | 11   | 700      | ns         | Clamped Inductive Load                         |  |

| Drain Voltage Fall Time                              | tf <sub>v</sub>      |          | 3    | N.10     | <b>N</b> . | See Test Diagram Fig. 14                       |  |

| Input Capacitance                                    | C <sub>iss</sub>     |          | 1650 |          | 201.0      | $V_{DS} = 25V$                                 |  |

| Output Capacitance                                   | C <sub>oss</sub>     |          | 650  | <u> </u> | pF         | $V_{GS} = 0$                                   |  |

| Reverse Transfer Capacitance                         | C <sub>rss</sub>     |          | 58   | NN.      | 100        | CON.                                           |  |

#### **Source-Drain Rating & Characteristics**

| Parameter                                              | Symbol             | Min         | Тур | Max | Units | Conditions                                                                                             |

|--------------------------------------------------------|--------------------|-------------|-----|-----|-------|--------------------------------------------------------------------------------------------------------|

| Diode Forward Voltage*                                 | V <sub>SD</sub>    | <u> </u>    |     | 1.0 | V     | $I_{S} = 15A^{O}, V_{GS} = 0V$                                                                         |

| Reverse Recovery Charge ④                              | Q <sub>rr</sub>    | N<br>N      | 76  | N   | WW.   | di/dt = 700A/µs<br>V <sub>DD</sub> = 16V, V <sub>GS</sub> = 0V, I <sub>S</sub> = 15A                   |

| Reverse Recovery Charge<br>(with Parallel Schottsky) ④ | Q <sub>rr(s)</sub> | 11.<br>11.1 | 67  |     | nC    | di/dt = 700A/µs<br>(with 10BQ040)<br>V <sub>DD</sub> = 16V, V <sub>GS</sub> = 0V, I <sub>S</sub> = 15A |

#### Notes:

- Repetitive rating; pulse width limited by max. junction temperature. (s) Calculated continuous current based on maximum allowable 1

- Pulse width  $\leq$  300 µs; duty cycle  $\leq$  2%. 2

- When mounted on 1 inch square copper board, t < 10 sec. 3

- Typ = measured  $Q_{oss}$ 4

$\circledast~R_{\theta}$  is measured at  $T_J$  approximately at  $90^{\circ}C$

www.irf.com

2

<sup>\*</sup>Devices are 100% tested to these parameters.

Junction temperature; switching and other losses will decrease RMS current capability; package limitation current = 20A.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## International

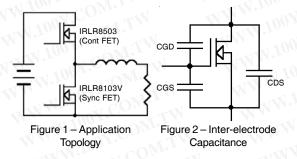

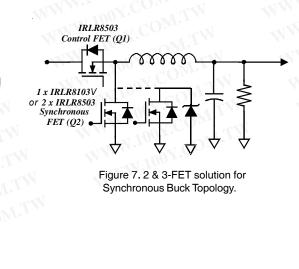

Power MOSFET Optimization for DC-DC Converters While the IRLR8103V and IRLR8503 can and are being used in a variety of applications, they were designed and optimized for low voltage DC-DC conversion in a synchronous buck converter topology, specifically, microprocessor power applications. The IRLR8503 (Figure 1) was optimized for the control FET socket, while the IRLR8103V was optimized for the synchronous FET function.

Because of the inter-electrode capacitance (Figure 2) of the Power MOSFET, specifying the R<sub>DSON</sub> of the device is not enough to ensure good performance. An optimization between R<sub>DSON</sub> and charge must be performed to insure the best performing MOSFET for a given application. Both die size and device architecture must be varied to achieve the minimum possible in-circuit losses. This is independently true for both control FET and synchronous FET. Unfortunately, the capacitances of a FET are non-linear and voltage dependent. Therefore, it is inconvenient to specify and use them effectively in switching power supply power loss estimations. This was well understood years ago and resulted in changing the emphasis from capacitance to gate charge on Power MOSFET data sheets.

| Table 1 – Traditional | Charge | Parameters |

|-----------------------|--------|------------|

|-----------------------|--------|------------|

| Device Capacitance      | Corresponding Charge Parameter |

|-------------------------|--------------------------------|

| C <sub>gs</sub>         | Q <sub>gs</sub>                |

| $C_{_{GS}} + C_{_{GD}}$ | Q <sub>g</sub>                 |

| C <sub>GD</sub>         | Q <sub>GD</sub>                |

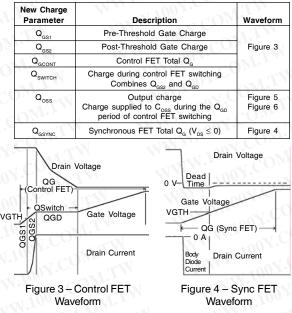

International Rectifier has recently taken the industry a step further by specifying new charge parameters that are even more specific to DC-DC converter design (Table 2). In order to understand these parameters, it is best to start with the in-circuit waveforms in Figure 3 & Figure 4.

#### www.irf.com

### **IRLR8503**

Table 2 - New Charge Parameters

The waveforms are broken into segments corresponding to charge parameters. These, in turn, correspond to discrete time segments of the switching waveform.

Losses may be broken into four categories: conduction loss, gate drive loss, switching loss, and output loss. The following simplified power loss equation is true for both MOSFETs in a synchronous buck converter:

$$P_{LOSS} = P_{CONDUCTION} + P_{GATE DRIVE} + P_{SWITCH} + P_{OUTPUT}$$

For the synchronous FET, the P<sub>SWITCH</sub> term becomes virtually zero and is ignored.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## IRLR8503

International

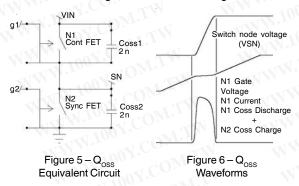

Table 3 and Table 4 describes the event during the various charge segments and shows an approximation of losses during that period.

|                    | Description                                                                                                                                                                                           | Segment Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conduction<br>Loss | Losses associated with MOSFET on time. I <sub>RMS</sub> is a function of load current and duty cycle.                                                                                                 | $P_{COND} = I_{RMS}^{2} \times R_{DS(on)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Gate Drive<br>Loss | Losses associated with charging and discharging the gate of the MOSFET every cycle. Use the control FET $Q_{g}$ .                                                                                     | $\mathbf{P}_{\mathrm{IN}} = \mathbf{V}_{\mathrm{G}} \times \mathbf{Q}_{\mathrm{G}} \times f$                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Switching<br>Loss  | Losses during the drain voltage and drain current transitions for every full cycle. Losses occur during the $Q_{_{GS2}}$ and $Q_{_{GD}}$ time period and can be simplified by using $Q_{_{switch}}$ . | $\begin{split} \mathbf{P}_{\text{QGS}2} &\approx \mathbf{V}_{\text{IN}} \times \mathbf{I}_{\text{L}} \times \frac{\mathbf{Q}_{\text{GS}2}}{\mathbf{I}_{\text{G}}} \times f \\ \mathbf{P}_{\text{QGD}} &\approx \mathbf{V}_{\text{IN}} \times \mathbf{I}_{\text{L}} \times \frac{\mathbf{Q}_{\text{GD}}}{\mathbf{I}_{\text{G}}} \times f \\ \mathbf{P}_{\text{SWITCH}} &\approx \mathbf{V}_{\text{IN}} \times \mathbf{I}_{\text{L}} \frac{\mathbf{Q}_{\text{SW}}}{\mathbf{I}_{\text{G}}} \times f \end{split}$ |

| Output<br>Loss     | Losses associated with the Q <sub>oss</sub> of the device every cycle when the control FET turns on. Losses are caused by both FETs, but are dissipated by the control FET.                           | $P_{\text{OUTPUT}} = \frac{Q_{\text{OSS}}}{2} \times V_{\text{IN}} \times F$                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WW.                | Description                                                                                                                                                                                                                                                            | Segment Losses                                                                               |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Conduction<br>Loss | Losses associated with MOSFET on time. I <sub>RMS</sub> is a function of load current and duty cycle.                                                                                                                                                                  | $\mathbf{P}_{\text{COND}} = \mathbf{I}_{\text{RMS}}^{2} \times \mathbf{R}_{\text{DSon}}$     |

| Gate Drive<br>Loss | Losses associated with charging and discharging the gate of the MOSFET every cycle. Use the Sync FET $\rm Q_{g}.$                                                                                                                                                      | $\mathbf{P}_{\mathrm{IN}} = \mathbf{V}_{\mathrm{G}} \times \mathbf{Q}_{\mathrm{G}} \times f$ |

| Switching<br>Loss  | Generally small enough to ignore except at light loads when the current reverses<br>in the output inductor. Under these conditions various light load power saving<br>techniques are employed by the control IC to maintain switching losses to a<br>negligible level. | P <sub>SWITCH</sub> ≈ 0                                                                      |

| Output<br>Loss     | Losses associated with the $Q_{oss}$ of the device every cycle when the control FET turns on. They are caused by the synchronous FET, but are dissipated in the control FET.                                                                                           | $\mathbf{P}_{OUTPUT} = \frac{\mathbf{Q}_{OSS}}{2} \times \mathbf{V}_{IN} \times f$           |

#### **Typical PC Application**

The IRLR8103V and the IRLR8503 are suitable for Synchronous Buck DC-DC Converters, and are optimized for use in next generation CPU applications. The IRLR8103V is primarily optimized for use as the low side synchronous FET (Q2) with low  $R_{DS(on)}$  and high CdV/dt immunity. The IRLR8503 is primarily optimized for use as the high side control FET (Q2) with low cobmined Qsw and  $R_{DS(on)}$ , but can also be used as a synchronous FET. The IRLR8503 is also tested for Cdv/dt immunity, critical for the low side socket. The typical configuration in which these devices may be used in shown in Figure 7.

# International

### IRLR8503

WWW.100Y.COM.TW WWW.100Y.COM.TW **IRLR8503**

International **IOR**Rectifier

WWW.100Y.COM.TW Figure 14. Clamped Inductive Load test diagram

## International

### **IRLR8503**

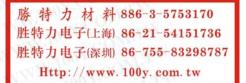

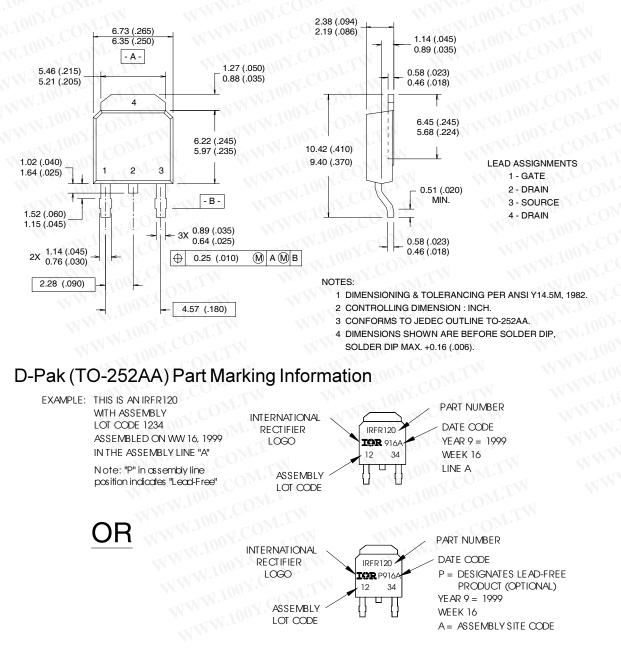

D-Pak (TO-252AA) Package Outline

Dimensions are shown in millimeters (inches)

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### **IRLR8503**

International

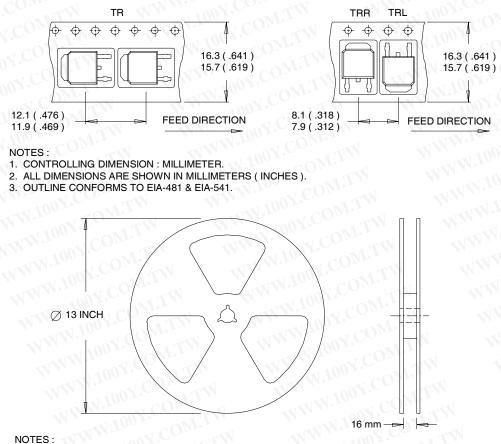

#### Tape & Reel Information

TO-252AA

1. OUTLINE CONFORMS TO EIA-481.

Data and specifications subject to change without notice. This product has been designed and qualified for the commercial market. Qualification Standards can be found on IR's Web site.

## International

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information. 5/05