勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

May 2003

DS90C385/DS90C365 +3.3V Programmable LVDS Transmitter 24-Bit

ink-85 MHz, +3.3V Programmable LVDS

# DS90C385/DS90C365 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link-85 MHz, +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-85 MHz

### **General Description**

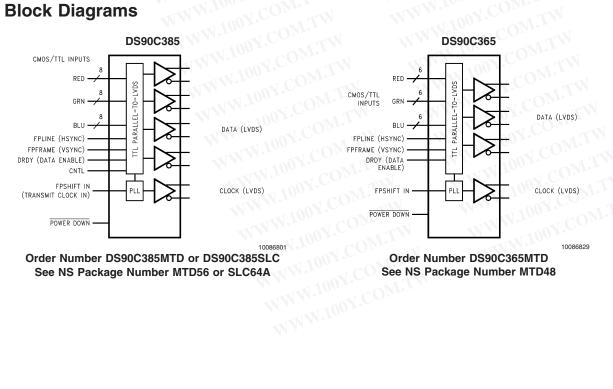

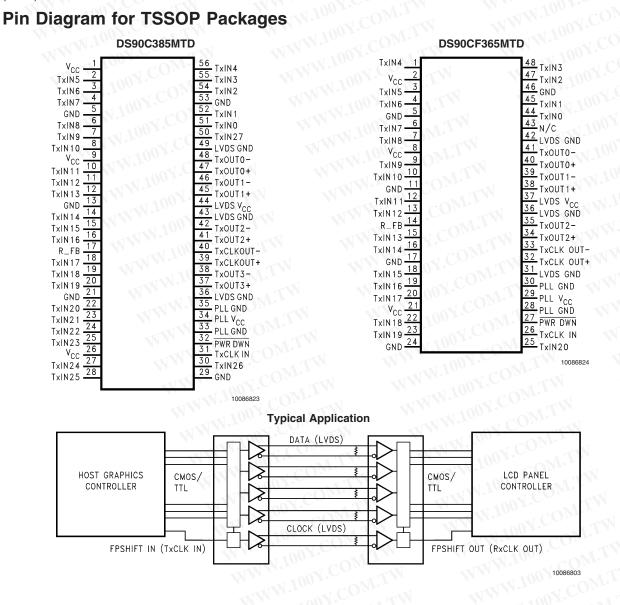

The DS90C385 transmitter converts 28 bits of LVCMOS/ LVTTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 85 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 595 Mbps per LVDS data channel. Using a 85 MHz clock, the data throughput is 297.5 Mbytes/sec. Also available is the DS90C365 that converts 21 bits of LVCMOS/ LVTTL data into three LVDS (Low Voltage Differential Signaling) data streams. Both transmitters can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge or Falling edge strobe transmitter will interoperate with a Falling edge strobe Receiver (DS90CF386/DS90CF366) without any translation logic.

The DS90C385 is also offered in a 64 ball, 0.8mm fine pitch ball grid array (FBGA) package which provides a 44 % reduction in PCB footprint compared to the TSSOP package.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces.

### **Features**

- 20 to 85 MHz shift clock support

- Best-in-Class Set & Hold Times on TxINPUTs

Tx power consumption <130 mW (typ) @85MHz Grayscale

- Tx Power-down mode <200µW (max)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA.

- Narrow bus reduces cable size and cost

- Up to 2.38 Gbps throughput

- Up to 297.5 Megabytes/sec bandwidth

- 345 mV (typ) swing LVDS devices for low EMI

- PLL requires no external components

- Compatible with TIA/EIA-644 LVDS standard

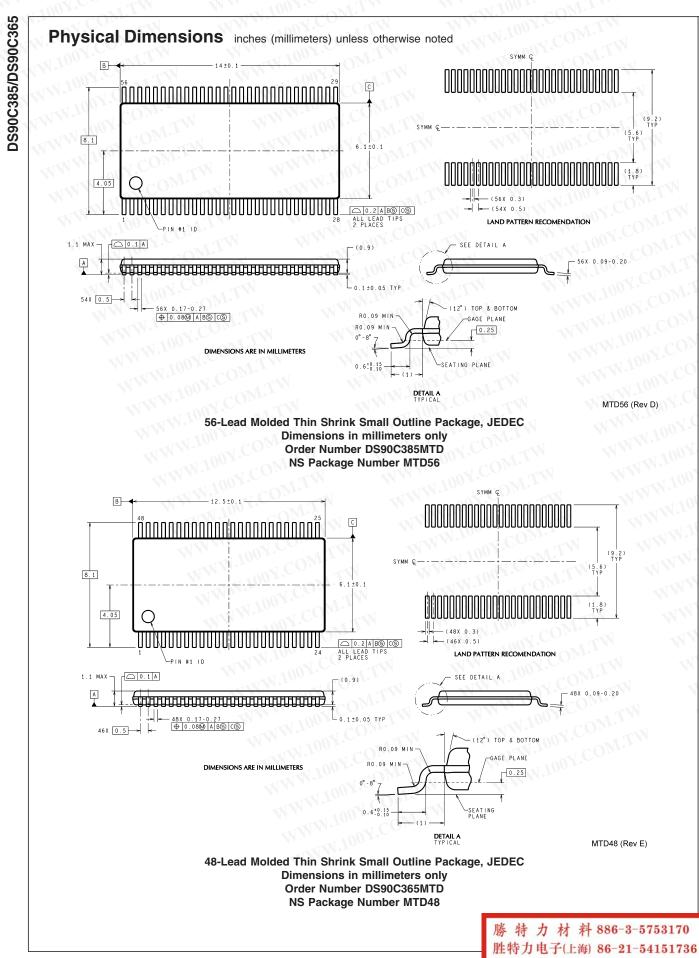

- Low profile 56-lead or 48-lead TSSOP package

- DS90C385 also available in a 64 ball, 0.8mm fine pitch ball grid array (FBGA) package

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) | -0.3V to +4V                      |

|-----------------------------------|-----------------------------------|

| CMOS/TTL Input Voltage            | -0.5V to (V <sub>CC</sub> + 0.3V) |

| LVDS Driver Output Voltage        | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Output Short Circuit         |                                   |

| Duration                          | Continuous                        |

| Junction Temperature              | +150°C                            |

| Storage Temperature               | -65°C to +150°C                   |

| Lead Temperature                  |                                   |

| (Soldering, 4 sec)                | +260°C                            |

| Solder reflow Temperature         |                                   |

| (20 sec for FBGA)                 | +220°C                            |

| Maximum Package Power Diss        | ipation Capacity @ 25°C           |

| MTD56 (TSSOP) Package:            |                                   |

| DS90C385MTD                       | 1.63 W                            |

| MTD48 (TSSOP) Package:            |                                   |

| DS90C365MTD                       | 1.98 W                            |

| SLC64 (FBGA) Package:             |                                   |

|                                   |                                   |

| DS90C385SLC               | 2.0 W                  |

|---------------------------|------------------------|

| Package Derating:         |                        |

| DS90C385MTD               | 12.5 mW/°C above +25°C |

| Package Derating:         |                        |

| DS90C365MTD               | 16 mW/°C above +25°C   |

| DS90C385SLC               | 10.2 mW/°C above +25°C |

| ESD Rating                |                        |

| (HBM, 1.5kΩ, 100pF)       | > 7 kV                 |

| (EIAJ, 0Ω, 200 pF)        | > 500V                 |

| Latch Up Tolerance @ 25°C | > ±300mA               |

|                           |                        |

# Recommended Operating Conditions

| onultions                               |     |     |       |                  |

|-----------------------------------------|-----|-----|-------|------------------|

|                                         | Min | Nom | Max I | Units            |

| Supply Voltage (V <sub>CC</sub> )       | 3.0 | 3.3 | 3.6   | V                |

| Operating Free Air                      |     |     |       |                  |

| Temperature (T <sub>A</sub> )           | -10 | +25 | +70   | °C               |

| Supply Noise Voltage (V <sub>CC</sub> ) |     |     | 100 r | mV <sub>PP</sub> |

| TxCLKIN frequency                       | 20  |     | 85    | MHz              |

|                                         |     |     |       |                  |

|                                         |     |     |       |                  |

|                                         |     |     |       |                  |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                     | Conditions                                  |                  | Min                   | Тур   | Max             | Units |

|------------------|---------------------------------------------------------------|---------------------------------------------|------------------|-----------------------|-------|-----------------|-------|

| LVCMOS           | /LVTTL DC SPECIFICATIONS                                      | I.T.                                        | N.100 CON        |                       |       | - N             | N.10. |

| V <sub>IH</sub>  | High Level Input Voltage                                      | N.T.W. WWW.100X.COM                         |                  | 2.0                   |       | V <sub>cc</sub> | V     |

| V <sub>IL</sub>  | Low Level Input Voltage                                       | TW WWW. 100Y.CO                             |                  | GND                   |       | 0.8             | V     |

| V <sub>CL</sub>  | Input Clamp Voltage                                           | I <sub>CL</sub> = −18 mA                    | WW. POWC         | J.M.                  | -0.79 | -1.5            | V     |

| I <sub>IN</sub>  | Input Current                                                 | $V_{IN} = 0.4V, 2.5V \text{ or } V_{CC}$    |                  | DV.                   | +1.8  | +10             | μA    |

|                  | WW 100Y.                                                      | V <sub>IN</sub> = GND                       | 1007.            | -10                   | 0     |                 | μA    |

| LVDS DO          | SPECIFICATIONS                                                | NT.                                         | YOUT             |                       | WT    | -               | MM    |

| V <sub>OD</sub>  | Differential Output Voltage                                   | $R_{L} = 100\Omega$                         |                  | 250                   | 345   | 450             | mV    |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between complimentary output states |                                             |                  | X.CON                 |       | 35              | mV    |

| V <sub>os</sub>  | Offset Voltage (Note 4)                                       |                                             |                  | 1.125                 | 1.25  | 1.375           | V     |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between complimentary output states | 100X.COM.LTW                                | 100Y.C           | $\mathcal{O}_{M^{*}}$ | 35    | mV              |       |

| l <sub>os</sub>  | Output Short Circuit Current                                  | $V_{OUT} = 0V, R_L = 100\Omega$             | Power Down = 0V, |                       | -3.5  | -5              | mA    |

| l <sub>oz</sub>  | Output TRI-STATE® Current                                     | Power Down= 0V, $V_{OUT}$ = 0V or V $_{CC}$ |                  |                       | C±1   | ±10             | μA    |

| TRANSM           | ITTER SUPPLY CURRENT                                          | 100Y.CO. TW                                 | A.M.             | 100                   | Y.    | VT.M.           |       |

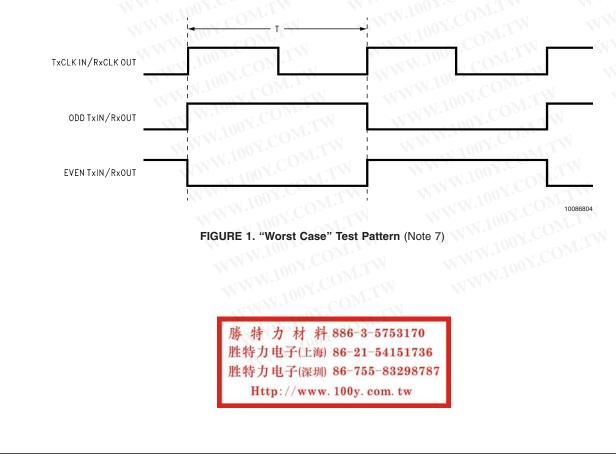

| ICCTW            | Transmitter Supply Current                                    | $R_{L} = 100\Omega,$                        | f = 32.5 MHz     | 14.                   | 31    | 45              | mA    |

|                  | Worst Case                                                    | C <sub>L</sub> = 5 pF,                      | f = 40 MHz       | WW.IV                 | 32    | 50              | mA    |

|                  | DS90C385                                                      | Worst Case Pattern                          | f = 65 MHz       |                       | 37    | 55              | mA    |

|                  | 1                                                             | (Figures 1, 4)                              | f = 85 MHz       |                       | 42    | 60              | mA    |

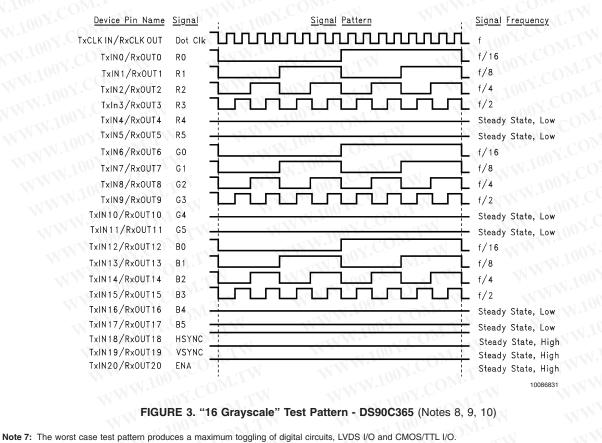

| ICCTG            | Transmitter Supply Current                                    | $R_{L} = 100\Omega,$                        | f = 32.5 MHz     |                       | 29    | 38              | mA    |

|                  | 16 Grayscale                                                  | C <sub>L</sub> = 5 pF,                      | f = 40 MHz       |                       | 30    | 40              | mA    |

|                  | DS90C385                                                      | 16 Grayscale Pattern                        | f = 65 MHz       |                       | 35    | 45              | mA    |

|                  |                                                               | (Figures 2, 4)                              | f = 85 MHz       |                       | 39    | 50              | mA    |

| www.      | nationa | l com   |

|-----------|---------|---------|

| ** ** **. | nationa | 1.00111 |

| ທ        |

|----------|

| Q        |

| Õ        |

| õ        |

| <u>8</u> |

| Ś        |

| Ο        |

| ഗ        |

| õ        |

| 0        |

| <b>O</b> |

| ω        |

| ດ        |

| S        |

|          |

D

Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol       | Parameter                                          | Conditio                                                       | ons          | Min | Тур | Max  | Units |

|--------------|----------------------------------------------------|----------------------------------------------------------------|--------------|-----|-----|------|-------|

| TRANSM       | ITTER SUPPLY CURRENT                               | NWW.IV CO                                                      | Mr.          | WW  | 1.1 | N.CC | JAN.  |

| ICCTW        | Transmitter Supply Current                         | $R_{L} = 100\Omega,$                                           | f = 32.5 MHz |     | 28  | 42   | mA    |

|              | Worst Case                                         | $C_L = 5 \text{ pF},$                                          | f = 40 MHz   | N   | 29  | 47   | mA    |

|              | DS90C365                                           | Worst Case Pattern<br>(Figures 1, 4)                           | f = 65 MHz   | N   | 34  | 52   | mA    |

| WW.100 COM.1 | COM.1                                              |                                                                | f = 85 MHz   | -   | 39  | 57   | mA    |

| ICCTG        | G Transmitter Supply Current $R_{L} = 100\Omega$ , | f = 32.5 MHz                                                   |              | 26  | 35  | mA   |       |

|              | 16 Grayscale                                       | $C_L = 5 \text{ pF},$                                          | f = 40 MHz   |     | 27  | 37   | mA    |

| DS90C365     | DS90C365 16 Grayscale Pattern                      | f = 65 MHz                                                     |              | 32  | 42  | mA   |       |

|              | W.100 COM.1                                        | (Figures 3, 4 )                                                | f = 85 MHz   | 1   | 36  | 47   | mA    |

| ICCTZ        | Transmitter Supply Current<br>Power Down           | Power Down = Low<br>Driver Outputs in TRI-S<br>Power Down Mode | TATE under   | W   | 10  | 55   | μA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and  $T_A$  = +25C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except V\_{OD} and  $\Delta V_{OD}).$

Note 4: V<sub>OS</sub> previously referred as V<sub>CM</sub>.

# **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                           | Min   | Тур  | Max   | Units |

|--------|-------------------------------------|-------|------|-------|-------|

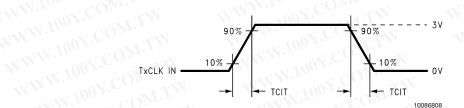

| TCIT   | TxCLK IN Transition Time (Figure 6) | 1.0   |      | 6.0   | ns    |

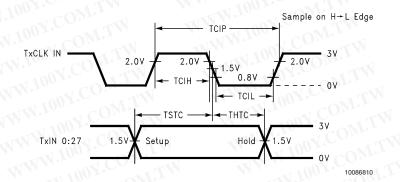

| TCIP   | TxCLK IN Period (Figure 7)          | 11.76 | Ť    | 50    | ns    |

| TCIH   | TxCLK IN High Time (Figure 7)       | 0.35T | 0.5T | 0.65T | ns    |

| TCIL   | TxCLK IN Low Time (Figure 7)        | 0.35T | 0.5T | 0.65T | ns    |

| TXIT   | TxIN Transition Time                | 1.5   | T.M. | 6.0   | ns    |

### **Transmitter Switching Characteristics**

| Symbol | commended operating supply and temperature ranges unless othe<br>Parameter      |            | Min    | Тур   | Max   | Units |

|--------|---------------------------------------------------------------------------------|------------|--------|-------|-------|-------|

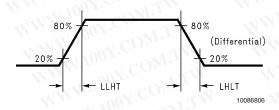

| LLHT   | LVDS Low-to-High Transition Time (Figure 5)                                     | WW W       | . with | 0.75  | 1.5   | ns    |

|        |                                                                                 |            |        |       | 1.5   | ns    |

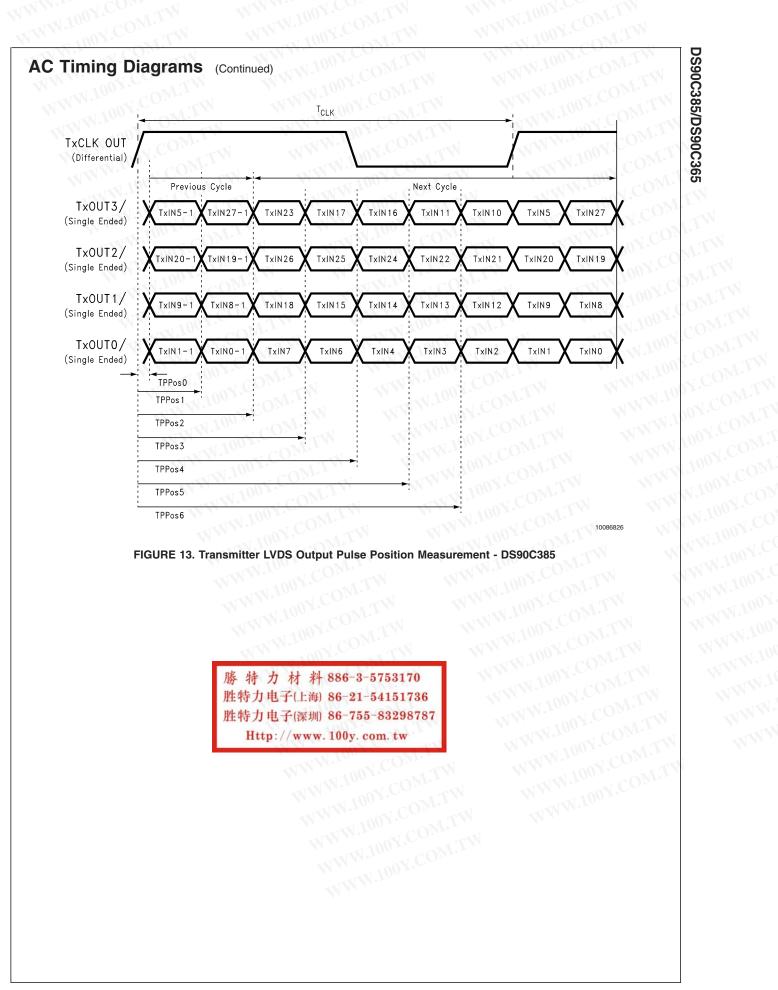

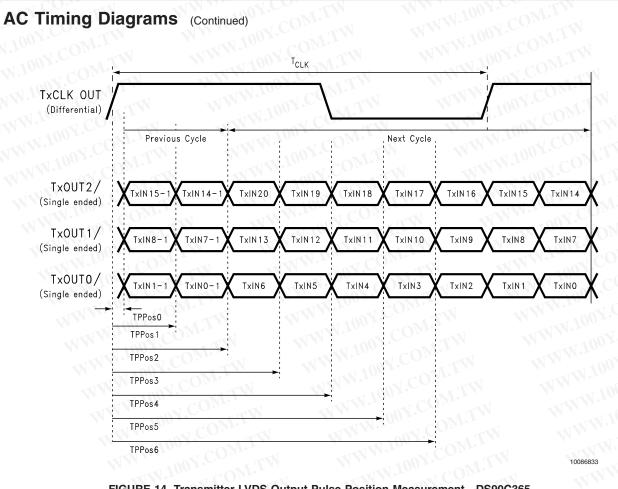

| TPPos0 | Transmitter Output Pulse Position for Bit 0 <i>(Figures 13, 14)</i><br>(Note 5) | f = 40 MHz | -0.25  | 0.75  | 0.25  | ns    |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                                     | V WT       | 3.32   | 3.57  | 3.82  | ns    |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                                     | N N        | 6.89   | 7.14  | 7.39  | ns    |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                                     | MIL        | 10.46  | 10.71 | 10.96 | ns    |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                                     | WT.M.      | 14.04  | 14.29 | 14.54 | ns    |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                                     | WT         | 17.61  | 17.86 | 18.11 | ns    |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                                     | COMPANY    | 21.18  | 21.43 | 21.68 | ns    |

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figures 13, 14) (Note 5)           | f = 65 MHz | -0.20  | 0     | 0.20  | ns    |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                                     | A.COM      | 2.00   | 2.20  | 2.40  | ns    |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                                     |            | 4.20   | 4.40  | 4.60  | ns    |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                                     |            | 6.39   | 6.59  | 6.79  | ns    |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                                     |            | 8.59   | 8.79  | 8.99  | ns    |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                                     |            | 10.79  | 10.99 | 11.19 | ns    |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                                     | 7          | 12.99  | 13.19 | 13.39 | ns    |

3

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

www.national.com

|        | somitter Switching Characteristics (Contin<br>commended operating supply and temperature ranges unless oth |                                    | oy.CC | M.T.   | W     |       |

|--------|------------------------------------------------------------------------------------------------------------|------------------------------------|-------|--------|-------|-------|

| Symbol | Parameter                                                                                                  |                                    | Min   | Тур    | Max   | Units |

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figures 13, 14) (Note 5)                                      | f = 85 MHz                         | -0.20 | 0      | 0.20  | ns    |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                                                                | A MM.                              | 1.48  | 1.68   | 1.88  | ns    |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                                                                | WW ND                              | 3.16  | 3.36   | 3.56  | ns    |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                                                                | Position for Bit 3                 |       | 5.04   | 5.24  | ns    |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                                                                |                                    | 6.52  | 6.72   | 6.92  | ns    |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                                                                | W WILL                             | 8.20  | 8.40   | 8.60  | ns    |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                                                                | V Vn                               | 9.88  | 10.08  | 10.28 | ns    |

| TSTC   | TxIN Setup to TxCLK IN (Figure 7)                                                                          | M                                  | 2.5   | .10-   | CON   | ns    |

| тнтс   | TxIN Hold to TxCLK IN (Figure 7)                                                                           | M.T.Y                              | 0     | V.100, | - c0  | ns    |

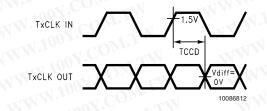

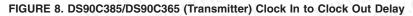

| TCCD   | TxCLK IN to TxCLK OUT Delay (Figure 8)                                                                     | $T_A = 25^{\circ}C, V_{CC} = 3.3V$ | 3.8   | W.100  | 6.3   | ns    |

|        | TxCLK IN to TxCLK OUT Delay (Figure 8)                                                                     | COM                                | 2.8   | N.W.V  | 7.1   | ns    |

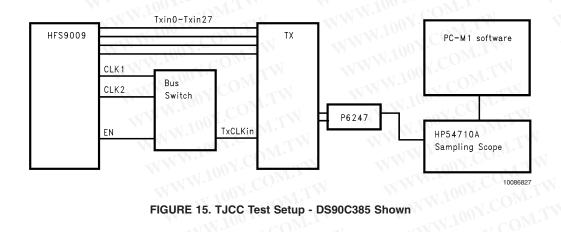

| TJCC   | Transmitter Jitter Cycle-to-Cycle (Figures 15, 16) (Note 6)                                                | f = 85 MHz                         |       | 110    | 150   | ps    |

|        | WWW.L. OOX.COM. TW WWWON                                                                                   | f = 65 MHz                         | V     | 210    | 230   | ps    |

|        | WW.100 CONTRACTION NO. 100                                                                                 | f = 40 MHz                         |       | 350    | 370   | ps    |

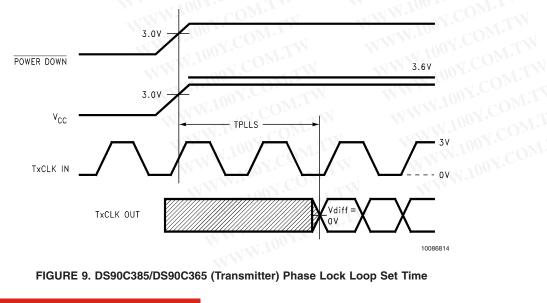

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 9)                                                                 | COMPT                              |       | IN     | 10    | ms    |

| TPDD   | Transmitter Power Down Delay (Figure 12)                                                                   | NTN                                |       | N      | 100   | ns    |

Note 5: The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temperature ranges. This parameter is functionality tested only on Automatic Test Equipment (ATE).

Note 6: The limits are based on bench characterization of the device's jitter response over the power supply voltage range. Output clock jitter is measured with a cycle-to-cycle jitter of +/-3ns applied to the input clock signal while data inputs are switching (See Figures 15 and 16). A jitter event of 3ns, represents worse case jump in the clock edge from most graphics controller VGA chips currently available. This parameter is used when calculating system margin as described in AN-1059.

# **AC Timing Diagrams**

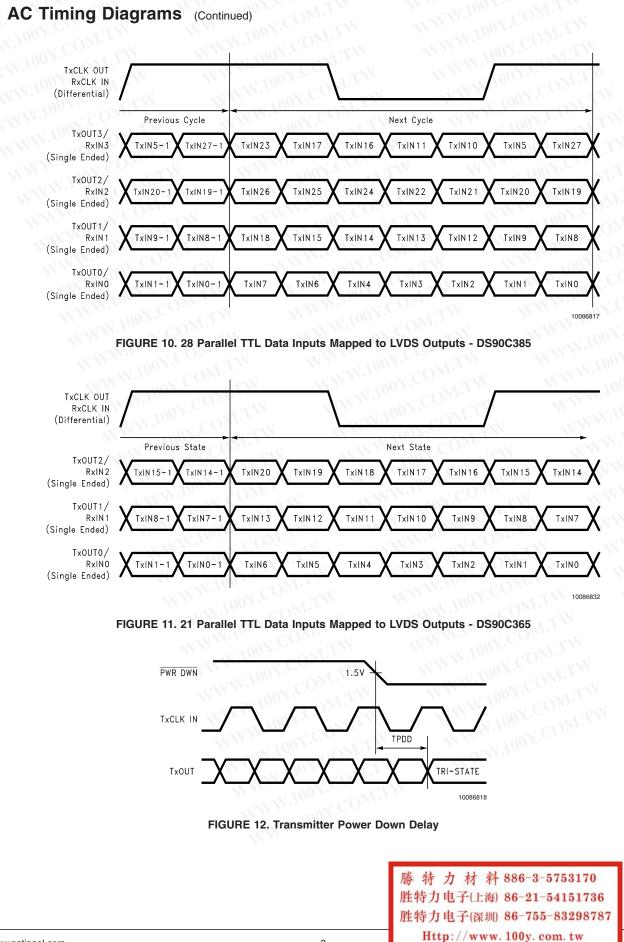

# AC Timing Diagrams (Continued)

100Y.COM.TW

WWW.100X.CO.

| Device Pin Name                  | Signal , | Signal Pattern                | Signal Frequency                            |

|----------------------------------|----------|-------------------------------|---------------------------------------------|

| TxCLK IN/RxCLK OUT               | Dot Clk  | wwwwwwww                      | Signal Frequency<br>f<br>f/16<br>f/8<br>f/4 |

| TxIN0/RxOUT0                     | RO L     | N. Too COM.                   | f/16                                        |

| TxIN1/RxOUT1                     | R1       |                               | f/8                                         |

| TxIN2/RxOUT2                     | R2       |                               | f/4                                         |

| TxIN3/RxOUT3                     | R3 🕇     |                               | f/2                                         |

| TxIN4/RxOUT4                     | R4       | W . 1001. M.I.                | _ Steady State, Low                         |

| TxIN5/RxOUT5                     | R7       | NT WWWWWWWW                   | Steady State, Low                           |

| TxIN6/RxOUT6                     | R5       | STATISTICONI.                 | Steady State, Low                           |

| TxIN7/RxOUT7                     | GO       | N N 100 - M.L                 | Steady State, Low                           |

| TxIN8/RxOUT8                     | G1 T     | CM WW 1001. MI                | f/16                                        |

| TxIN9/RxOUT9                     | G2       | AL AND COM                    | _ f/8                                       |

| TxIN10/RxOUT10                   | G6       |                               | _ f/4                                       |

| TxIN11/RxOUT11                   | G7       |                               | _ f/2                                       |

| TxIN12/RxOUT12                   | G3       | N                             | Steady State, Low                           |

| TxIN13/RxOUT13                   | G4       | NIT W SILOUT                  | Steady State, Low                           |

| TxIN14/RxOUT14                   | G5       | VI WW MAR                     | Steady State, Low                           |

| TxIN15/RxOUT15                   | B0       | OM                            | Steady State, Low                           |

| TxIN16/RxOUT16                   | B6       | M.I.                          | _ f/16                                      |

| TxIN17/RxOUT17                   | В7       | CO. WW 100X.                  | _ f/8                                       |

| TxIN18/RxOUT18                   | B1 L     |                               | _ f/4                                       |

| TxIN19/RxOUT19                   | B2       |                               | _ f/2                                       |

| TxIN20/RxOUT20                   | B3 _     | A CONTRACTOR AND A CONTRACTOR | _ f/2<br>_ Steady State, Low                |

| TxIN21/RxOUT21                   | B4       | CONTRACTOR OF THE OWNER       | - Steady State, Low                         |

| TxIN22/RxOUT22                   | B5       |                               | - Steady State, Low                         |

| TxIN23/RxOUT23                   | RES      |                               | - Steady State, Low                         |

| TxIN24/RxOUT24<br>TxIN25/RxOUT25 | HSYNC    | N COMPANY NIMIT               | - Steady State, High                        |

| TxIN25/Rx00125<br>TxIN26/Rx0UT26 |          | Too OM'N                      | - Steady State, High                        |

| TxIN27/Rx00127                   | R6       | 100X ON THE WAY               | - Steady State, High                        |

| 1,11(2) / 1(20012)               |          | N. L. COMMENT                 | - Steady State, High                        |

|                                  |          |                               | 10086805                                    |

WWW.100X.CC

100Y.COM.TW

WT.IL

W.100Y.COM.TW

WWW.100Y.C

M.TW

FIGURE 2. "16 Grayscale" Test Pattern - DS90C385 (Notes 8, 9, 10) WWW.100Y.COM.TW WWW.100X WWW.100Y.COM.T

WW.100Y.COM.TW 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw WWW.100Y.COM WWW.100

V.COM.TW

## AC Timing Diagrams (Continued)

DS90C385/DS90C365

Note 8: The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

Note 9: Figures 1, 2 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Note 10: Recommended pin to signal mapping. Customer may choose to define differently.

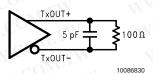

### FIGURE 4. DS90C385/DS90C365 (Transmitter) LVDS Output Load

### FIGURE 5. DS90C385/DS90C365 (Transmitter) LVDS Transition Times

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### AC Timing Diagrams (Continued)

FIGURE 6. DS90C385/DS90C365 (Transmitter) Input Clock Transition Time

FIGURE 7. DS90C385/DS90C365 (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

WWW.100X.CU

00Y.COM.T

# WILDOY.COM.TV DS90C385SLC SLC64A (FBGA) Package Pin Summary — FPD Link Transmitter

100X.COM.

| Pin Name             | I/O        | No. | W 1 1001.0 M.I'                                                                    | Description                                                |  |  |  |

|----------------------|------------|-----|------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| TxIN                 | 1 de       | 28  | TTL level input.                                                                   | WWWWWWWWWWWWWWW                                            |  |  |  |

| TxOUT+               | 0          | 4   | Positive LVDS differential data output.                                            | WWW. COM. TW                                               |  |  |  |

| TxOUT-               | 0          | 4   | Negative LVDS differential data output.                                            | Jegative LVDS differential data output.                    |  |  |  |

| TxCLKIN              | L          | 51  | TL level clock input. The rising edge acts as data strobe. Pin name TxCLK IN.      |                                                            |  |  |  |

| R_FB                 | COm        | 1   | Programmable strobe select. HIGH = rising edge, LOW = falling edge.                |                                                            |  |  |  |

| TxCLK OUT+           | 0          | 1   | ositive LVDS differential clock output.                                            |                                                            |  |  |  |

| TxCLK OUT-           | 0          | 1.1 | legative LVDS differential clock output.                                           |                                                            |  |  |  |

| PWR DOWN             | 4.V<br>0.V | ont | TTL level input. Assertion (low input) TR power down. See Applications Information | RI-STATES the outputs, ensuring low current at on section. |  |  |  |

| V <sub>cc</sub>      | Î          | 3   | Power supply pins for TTL inputs.                                                  | DNL. WWW.L CON                                             |  |  |  |

| GND                  | 001.       | 5   | Ground pins for TTL inputs.                                                        | 味 北 よ よ ** ののの の 5550150                                   |  |  |  |

| PLL V <sub>cc</sub>  |            | .9  | Power supply pin for PLL.                                                          | — 勝特力材料 886-3-5753170                                      |  |  |  |

| PLL GND              | · Y        | 2   | Ground pins for PLL.                                                               | 胜特力电子(上海) 86-21-54151736                                   |  |  |  |

| LVDS V <sub>CC</sub> | N.100      | 2   | Power supply pin for LVDS outputs.                                                 | 胜特力电子(深圳) 86-755-83298787                                  |  |  |  |

| LVDS GND             |            | 4   | Ground pins for LVDS outputs.                                                      | Http://www.100y.com.tw                                     |  |  |  |

| NC                   | 14.        | 6   | Pins not connected.                                                                | X. Marine Marine 100 Fr                                    |  |  |  |

### DS90C385SLC SLC64A (FBGA) Package Pin Description — FPD Link Transmitter WWW.1001 N COM.TW

| COM. I. | By Pin    |     |

|---------|-----------|-----|

| Туре    | Pin Name  | Pin |

| COT TA  | TxIN27    | A1  |

| 0       | TxOUT0-   | A2  |

| 0       | TxOUT0+   | A3  |

| P P     | LVDS VCC  | A4  |

| PON     | LVDS VCC  | A5  |

| 0_0     | TxCLKOUT- | A6  |

| 0 0     | TxCLKOUT+ | A7  |

| 0       | TxOUT3+   | A8  |

| N.1 CO  | TxIN1     | B1  |

| N.100   | TxIN0     | B2  |

| G       | LVDS GND  | B3  |

| G       | LVDS GND  | B4  |

| 0       | TxOUT2-   | B5  |

| 0.100   | TxOUT3-   | B6  |

| G       | LVDS GND  | B7  |

| WWW     | NC        | B8  |

| AVV.14  | TxIN3     | C1  |

|         | NC        | C2  |

| NN      | NC        | C3  |

| 0       | TxOUT1-   | C4  |

| 0       | TxOUT2+   | C5  |

| G       | PLL GND   | C6  |

| P       | PLL VCC   | C7  |

| I       | TxCLKIN   | C8  |

| I       | TxIN4     | D1  |

| I       | TxIN2     | D2  |

| G       | GND       | D3  |

|      | By Pin Type |         |

|------|-------------|---------|

| Pin  | Pin Name    | Туре    |

| D3   | GND         | G       |

| E4   | GND         | G       |

| E8   | GND         | G       |

| G1 0 | GND         | G       |

| G6   | GND         | G       |

| B3   | LVDS GND    | G       |

| B4   | LVDS GND    | G       |

| B7   | LVDS GND    | G       |

| D5   | LVDS GND    | G 📢     |

| C6   | PLL GND     | G       |

| D6   | PLL GND     | G       |

| D7   | PWR DOWN    |         |

| G5   | R_FB        | I W     |

| C8   | TxCLKIN     |         |

| B2   | TxIN0       | 1. T. I |

| B1 🔨 | TxIN1       | WTN     |

| D2   | TxIN2       | 1.12    |

| C1   | TxIN3       | I       |

| D1   | TxIN4       | I       |

| F1   | TxIN5       | I       |

| E2   | TxIN6       |         |

| E3   | TxIN7       | 1       |

| G2   | TxIN8       | 1       |

| H1   | TxIN9       | 1       |

| G3   | TxIN10      | 1       |

| H3   | TxIN11      | I       |

| F4   | TxIN12      | 1       |

N.TW

100X.COM.TW

# DS90C385SLC SLC64A (FBGA) Package Pin Description -FPD Link Transmitter (Continued)

100Y.COM.

| NN. | By Pin   |          |

|-----|----------|----------|

| D4  | TxOUT1+  | 0        |

| D5  | LVDS GND | G        |

| D6  | PLL GND  | G        |

| D7  | PWD DOWN | LA I     |

| D8  | TxIN26   | N I      |

| E1  | VCC      | Р        |

| E2  | TxIN6    |          |

| E3  | TxIN7    | PT       |

| E4  | GND      | G        |

| E5  | TxIN16   | OM       |

| E6  | VCC      | P        |

| E7  | TxIN24   | WT I     |

| E8  | GND      | G        |

| F1  | TxIN5    | COM-     |

| F2  | NC       | OX.      |

| F3  | NC       | N.Com    |

| F4  | TxIN12   | 10M      |

| F5  | TxIN17   | 100 100  |

| F6  | NC       | 1001.    |

| F7  | TxIN22   | U.CO     |

| F8  | TxIN25   | V. P. C  |

| G1  | GND      | G        |

| G2  | TxIN8    | 1107.    |

| G3  | TxIN10   | No. Los  |

| G4  | TxIN13   | I.WW.    |

| G5  | R_FB     | 100      |

| G6  | GND      | G        |

| G7  | TxIN21   | ANN .    |

| G8  | TxIN23   | 1.171    |

| H1  | TxIN9    |          |

| H2  | VCC      | P        |

| H3  | TxIN11   | - AVV    |

| H4  | TxIN14   | I.       |

| H5  | TxIN15   | - Pillin |

| H6  | TxIN18   |          |

| H7  | TxIN19   |          |

| H8  | TxIN20   |          |

| M.T.Y | By Pin Type |          |

|-------|-------------|----------|

| G4    | TxIN13      | Y.C      |

| H4    | TxIN14      | N.C      |

| H5    | TxIN15      | . <1 (   |

| E5    | TxIN16      | 001.     |

| F5    | TxIN17      | 1001     |

| H6    | TxIN18      |          |

| H7    | TxIN19      | N.100    |

| H8    | TxIN20      | W10      |

| G7    | TxIN21      |          |

| F7_0  | TxIN22      | $N_{M'}$ |

| G8    | TxIN23      | W.       |

| E7    | TxIN24      |          |

| F8    | TxIN25      | NNY      |

| D8    | TxIN26      | WIG      |

| A1    | TxIN27      |          |

| A6    | TxCLKOUT-   |          |

| A7    | TxCLKOUT+   |          |

| A2    | TxOUT0-     | (        |

| A3    | TxOUT0+     | (        |

| C4    | TxOUT1-     | (        |

| D4    | TxOUT1+     | (        |

| B5    | TxOUT2-     | (        |

| C5    | TxOUT2+     | (        |

| B6    | TxOUT3-     | N (      |

| A8    | TxOUT3+     |          |

| A4    | LVDS VCC    |          |

| A5    | LVDS VCC    | TM       |

| C7    | PLL VCC     | WT.      |

| E1    | VCC         | 1        |

| E6    | VCC         | M.       |

| H2    | VCC         | T.M      |

| B8    | NC          |          |

| C2    | NC          | OM.      |

| C3    | NC          | CON      |

| F2    | NC          |          |

| F3    | NC          | 1.00     |

| F6    | NC          | -1 C.C   |

O : Output

P : Power NC : No Connect

WWW.100Y.C

WY.COM.T

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

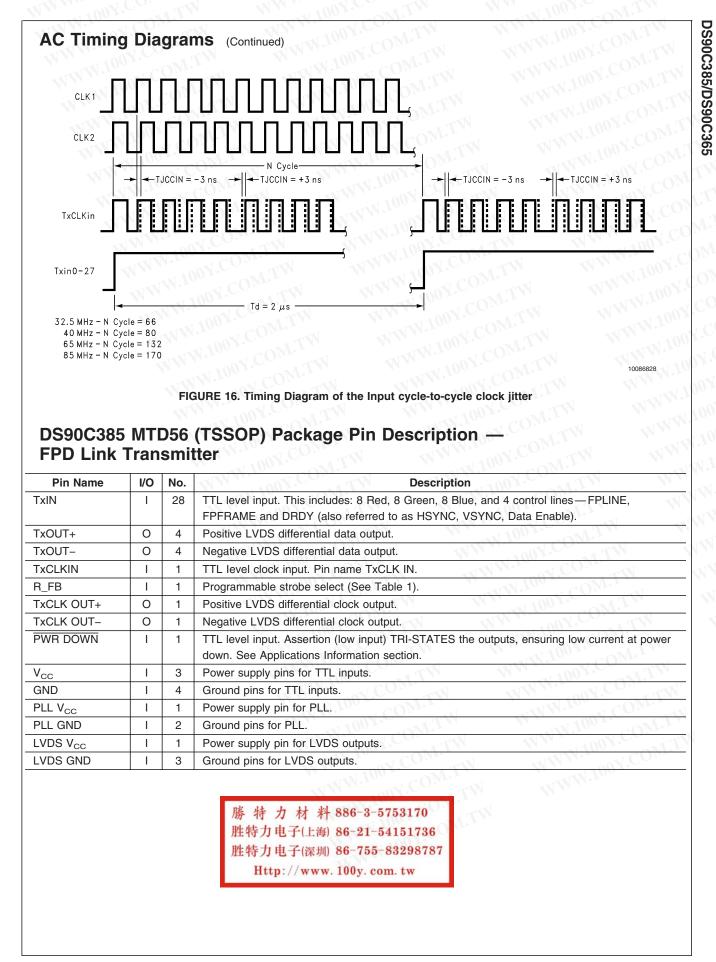

### DS90C365 Pin Description — FPD Link Transmitter

| Pin Name             | I/O       | No.         | Descr                                                                                                                                                 | iption |

|----------------------|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| TxIN                 | MJ        | 21          | TTL level input. This includes: 6 Red, 6 Green, 6 Blue, and 3 control lines—FPLINE, FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable). |        |

| TxOUT+               | 0         | 3           | Positive LVDS differential data output.                                                                                                               |        |

| TxOUT-               | 0         | 3           | Negative LVDS differential data output.                                                                                                               |        |

| TxCLKIN              | $C\Phi_D$ | 1           | TTL level clock input. Pin name TxCLK IN.                                                                                                             |        |

| R_FB                 |           | 1           | Programmable strobe select (See Table 1).                                                                                                             |        |

| TxCLK OUT+           | 0         | 1           | Positive LVDS differential clock output.                                                                                                              |        |

| TxCLK OUT-           | 0         | 1           | Negative LVDS differential clock output.                                                                                                              |        |

| PWR DOWN             | 01.0      |             | TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low current at powe down. See Applications Information section.               |        |

| V <sub>cc</sub>      | 001       | 3           | Power supply pins for TTL inputs.                                                                                                                     |        |

| GND                  | 1.        | 4           | Ground pins for TTL inputs.                                                                                                                           |        |

| PLL V <sub>cc</sub>  | 1         | <b>_1</b> C | Power supply pin for PLL.                                                                                                                             |        |

| PLL GND              | 1.10      | 2           | Ground pins for PLL.                                                                                                                                  |        |

| LVDS V <sub>cc</sub> |           | 01          | Power supply pin for LVDS outputs.                                                                                                                    |        |

| LVDS GND             | 1         | 3           | Ground pins for LVDS outputs.                                                                                                                         |        |

## **Applications Information**

The DS90C385/DS90C365 are backward compatible with the DS90C383/DS90C363, DS90C383A/DS90C363A and the TSSOP versions are a pin-for-pin replacements. The device (DS90C385/DS90C365) utilizes a different PLL architecture employing an internal 7X clock for enhanced pulse position control.

This device (DS90C385/DS90C365) also features reduced variation of the TCCD parameter which is important for dual pixel applications. (See AN-1084) TCCD variation has been measured to be less than 500ps at 85MHz under normal operating conditions.

This device may also be used as a replacement for the DS90CF583/563 (5V, 65MHz) and DS90CF581/561 (5V, 40MHz) FPD-Link Transmitters with certain considerations/ modifications:

- 1. Change 5V power supply to 3.3V. Provide this supply to the V<sub>CC</sub>, LVDS V<sub>CC</sub> and PLL V<sub>CC</sub> of the transmitter.

- 2. The DS90C385/DS90C365 transmitter input and control inputs accept 3.3V LVTTL/LVCMOS levels. They are not 5V tolerant.

- To implement a falling edge device for the DS90C385/ DS90C365, the R\_FB pin may be tied to ground OR left unconnected (an internal pull-down resistor biases this pin low). Biasing this pin to Vcc implements a rising edge device.

### TRANSMITTER CLOCK JITTER CYCLE-TO-CYCLE

Figures 15 and 16 illustrate the timing of the input clock relative to the input data. The input clock (TxCLKin) is intentionally shifted to the left –3ns and +3ns to the right when data (Txin0-27) is high. This 3ns of cycle-to-cycle clock jitter is repeated at a period of 2 $\mu$ s, which is the period of the input data (1 $\mu$ s high, 1 $\mu$ s low). At different operating frequencies the N Cycle is changed to maintain the desired 3ns cycle-to-cycle jitter at 2 $\mu$ s period.

### TRANSMITTER INPUT PINS

The TxIN and control input pins are compatible with LVC-MOS and LVTTL levels. These pins are not 5V tolerant.

### TRANSMITTER INPUT CLOCK

The transmitter input clock must always be present when the device is enabled ( $\overrightarrow{PWR}$  DOWN = HIGH). If the clock is stopped, the  $\overrightarrow{PWR}$  DOWN pin must be used to disable the PLL. The  $\overrightarrow{PWR}$  DOWN pin must be held low until after the input clock signal has been reapplied. This will ensure a proper device reset and PLL lock to occur.

力材料 886-3-5753170

胜特力电子(上海) 86-21-54151736

胜特力电子(深圳) 86-755-83298787

Http://www. 100v. com. tw

特

### POWER SEQUENCING AND POWERDOWN MODE

Outputs of the transmitter remain in TRI-STATE until the power supply reaches 2V. Clock and data outputs will begin to toggle 10 ms after  $V_{\rm CC}$  has reached 3V and the Power-down pin is above 1.5V. Either device may be placed into a powerdown mode at any time by asserting the Powerdown pin (active low). Total power dissipation for each device will decrease to 5  $\mu$ W (typical).

The transmitter input clock may be applied prior to powering up and enabling the transmitter. The transmitter input clock may also be applied after power up; however, the use of the PWR DOWN pin is required as described in the Transmitter Input Clock section. Do not power up and enable ( $\overline{PWR}$ DOWN = HIGH) the transmitter without a valid clock signal applied to the TxCLK IN pin.

The FPD Link chipset is designed to protect itself from accidental loss of power to either the transmitter or receiver. If power to the transmit board is lost, the receiver clocks (input and output) stop. The data outputs (RxOUT) retain the states they were in when the clocks stopped. When the receiver board loses power, the receiver inputs are controlled by a failsafe bias circuitry. The LVDS inputs are High-Z during initial power on and power off conditions. Current is limited (5 mA per input) by the fixed current mode drivers, thus avoiding the potential for latchup when powering the device.

### **RECEIVER FAILSAFE FEATURE**

The FPD Link receivers have input failsafe bias circuitry to guarantee a stable receiver output for floating or terminated receiver inputs. Under these conditions receiver inputs will be pulled to a HIGH state. This is the case if not all data channels are required in the application. Leave the extra

### Applications Information (Continued)

channel's inputs open. This minimizes power dissipation and locks the unused channels outputs into a stable known (HIGH) state.

If a clock signal is present, data outputs will all be HIGH; if the clock input is also floating/terminated, data outputs will remain in the last valid state. A floating/terminated clock input will result in a LOW clock output.

TABLE 1. Programmable Transmitter (DS90C385/DS90C365)

| Pin  | Condition        | Strobe Status       |

|------|------------------|---------------------|

| R_FB | $R_FB = V_{CC}$  | Rising edge strobe  |

| R_FB | R_FB = GND or NC | Falling edge strobe |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.1 A1 BALL PAD CORNER-N 5.6 1.4±0. A1 BALL PAD CORNER М 0.8 TYP 0.36±0.05 -SEATING PLANE $\odot$ $\odot$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 00000000 В 00000000 С 00000000 D 8±0.1 00000000 Ε 00000000 00000000 G 0 0000000 Н 8 64X Ø0.46 Ø0.1500 N LS MS Ф Ø0.08M N

DIMENSIONS ARE IN MILLIMETERS

SLC64A (Rev C

64 ball, 0.8mm fine pitch ball grid array (FBGA) Package Dimensions show in millimeters only Order Number DS90C385SLC NS Package Number SLC64A