### 4-Bit Bidirectional Universal Shift Register

The SN74LS194A is a High Speed 4-Bit Bidirectional Universal Shift Register. As a high speed multifunctional sequential building block, it is useful in a wide variety of applications. It may be used in serial-serial, shift left, shift right, serial-parallel, parallel-serial, and parallel-parallel data register transfers. The LS194A is similar in operation to the LS195A Universal Shift Register, with added features of shift left without external connections and hold (do nothing) modes of operation. It utilizes the Schottky diode clamped process to achieve high speeds and is fully compatible with all ON Semiconductor TTL families.

- Typical Shift Frequency of 36 MHz

- Asynchronous Master Reset

- Hold (Do Nothing) Mode

- Fully Synchronous Serial or Parallel Data Transfers

- Input Clamp Diodes Limit High Speed Termination Effects

### **GUARANTEED OPERATING RANGES**

| Symbol          | Parameter                              | Min  | Тур  | Max  | Unit |

|-----------------|----------------------------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage                         | 4.75 | 5.0  | 5.25 | V    |

| T <sub>A</sub>  | Operating Ambient<br>Temperature Range | 0    | 25   | 70   | √.°C |

| I <sub>OH</sub> | Output Current – High                  |      | AN A | -0.4 | mA   |

| I <sub>OL</sub> | Output Current – Low                   | N    | W    | 8.0  | mA   |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### ON Semiconductor

Formerly a Division of Motorola

http://onsemi.com

LOW

POWER

SCHOTTKY

PLASTIC N SUFFIX CASE 648

SOIC D SUFFIX CASE 751B

### ORDERING INFORMATION

| 7 7 7 1     |            |                  |

|-------------|------------|------------------|

| Device      | Package    | Shipping         |

| SN74LS194AN | 16 Pin DIP | 2000 Units/Box   |

| SN74LS194AD | 16 Pin     | 2500/Tape & Reel |

### .100Y.COM.TW **SN74LS194A**

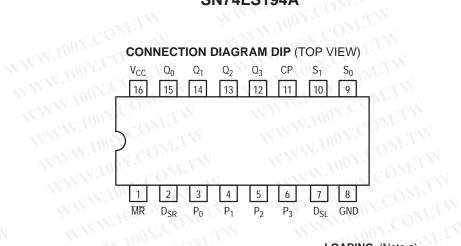

### CONNECTION DIAGRAM DIP (TOP VIEW)

|                                 |                                      | HIGH     | LOW     |

|---------------------------------|--------------------------------------|----------|---------|

| PIN NAMES                       |                                      | - 111011 | 1000    |

| S <sub>0</sub> , S <sub>1</sub> | Mode Control Inputs                  | 0.5 U.L. | 0.25 U. |

| $P_0 - P_3$                     | Parallel Data Inputs                 | 0.5 U.L. | 0.25 U  |

| $D_SR$                          | Serial (Shift Right) Data Input      | 0.5 U.L. | 0.25 U  |

| $D_{SL}$                        | Serial (Shift Left) Data Input       | 0.5 U.L. | 0.25 U  |

| CP                              | Clock (Active HIGH Going Edge) Input | 0.5 U.L. | 0.25 U  |

| MR                              | Master Reset (Active LOW) Input      | 0.5 U.L. | 0.25 U  |

| Q <sub>0</sub> – Q <sub>3</sub> | Parallel Outputs                     | 10 U.L.  | 5 U.L   |

| NOTES:                          |                                      |          |         |

|                                 |                                      |          |         |

100Y.COM.TW

WWW.100Y.

WT.MI

WWW.100Y.COM.TW

# NOTES:

WWW.100Y.COM.TW

a) 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW. WWW.100Y.COM.TW WWW.100X WWW.100Y.COM.T

> 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

N.COM.TW

WWW.100Y.COM.TW

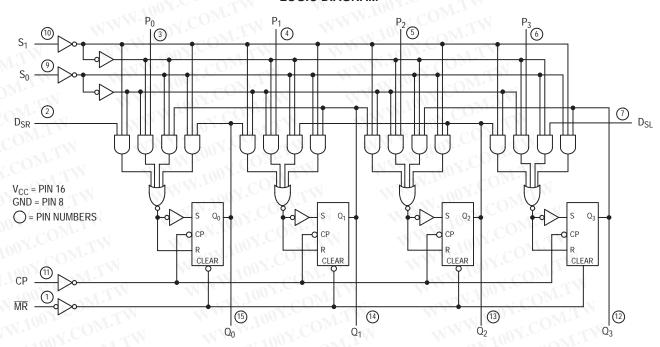

### LOGIC DIAGRAM

### **FUNCTIONAL DESCRIPTION**

The Logic Diagram and Truth Table indicate the functional characteristics of the LS194A 4-Bit Bidirectional Shift Register. The LS194A is similar in operation to the ON Semiconductor LS195A Universal Shift Register when used in serial or parallel data register transfers. Some of the common features of the two devices are described below:

All data and mode control inputs are edge-triggered, responding only to the LOW to HIGH transition of the Clock (CP). The only timing restriction, therefore, is that the mode control and selected data inputs must be stable one set-up time prior to the positive transition of the clock pulse.

The register is fully synchronous, with all operations taking place in less than 15 ns (typical) making the device especially useful for implementing very high speed CPUs, or the memory buffer registers.

The four parallel data inputs  $(P_0, P_1, P_2, P_3)$  are D-type inputs. When both  $S_0$  and  $S_1$  are HIGH, the data appearing on  $P_0$ ,  $P_1$ ,  $P_2$ , and  $P_3$  inputs is transferred to the  $Q_0$ ,  $Q_1$ ,  $Q_2$ , and  $Q_3$  outputs respectively following the next LOW to HIGH transition of the clock.

The asynchronous Master Reset ( $\overline{MR}$ ), when LOW, overrides all other input conditions and forces the Q outputs LOW.

Special logic features of the LS194A design which increase the range of application are described below:

Two mode control inputs  $(S_0, S_1)$  determine the synchronous operation of the device. As shown in the Mode Selection Table, data can be entered and shifted from left to right (shift right,  $Q_0 \rightarrow Q_1$ , etc.) or right to left (shift left,  $Q_3 \rightarrow Q_2$ , etc.), or parallel data can be entered loading all four bits of the register simultaneously. When both  $S_0$  and  $S_1$ , are LOW, the existing data is retained in a "do nothing" mode without restricting the HIGH to LOW clock transition.

D-type serial data inputs ( $D_{SR}$ ,  $D_{SL}$ ) are provided on both the first and last stages to allow multistage shift right or shift left data transfers without interfering with parallel load operation.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

### MODE SELECT — TRUTH TABLE

| ODED ATING MODE | -100             |                | IN             | PUTS            |                 |                | Mr.                              | 0                                | UTPUTS                           |                                  |

|-----------------|------------------|----------------|----------------|-----------------|-----------------|----------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| OPERATING MODE  | MR               | S <sub>1</sub> | S <sub>0</sub> | D <sub>SR</sub> | D <sub>SL</sub> | P <sub>n</sub> | $Q_0$                            | Q <sub>1</sub>                   | Q <sub>2</sub>                   | $Q_3$                            |

| Reset           | OL.              | Х              | Х              | X 🕥             | Х               | X              | L                                | LL                               | L                                | L                                |

| Hold            | H                | Ol             | W              | X               | X               | X              | $q_0$                            | <b>q</b> <sub>1</sub>            | $q_2$                            | q <sub>3</sub>                   |

| Shift Left      | H                | h<br>h         | WE             | X<br>X          | h               | X              | 9 <sub>1</sub><br>9 <sub>1</sub> | q <sub>2</sub><br>q <sub>2</sub> | q <sub>3</sub><br>q <sub>3</sub> | L<br>H                           |

| Shift Right     | H <sub>0</sub> 0 | 7.GO*          | h<br>h         | l<br>h          | X               | X              | H                                | q <sub>0</sub>                   | 91<br>91                         | q <sub>2</sub><br>q <sub>2</sub> |

| Parallel Load   | ~H\0             | h              | h              | Х               | Х               | $P_n$          | Po                               | Pı                               | P2                               | P <sub>3</sub>                   |

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                 | W.I                            | . ≤7 C! | Limits   |      |      | WW.Lo                                                                           |                                                                         |  |

|-----------------|--------------------------------|---------|----------|------|------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Symbol          | Parameter                      | Min     | Тур      | Max  | Unit | Te                                                                              | st Conditions                                                           |  |

| VIH             | Input HIGH Voltage             | 2.0     | $CO_{M}$ | LM   | ٧    | Guaranteed Inp<br>All Inputs                                                    | ut HIGH Voltage for                                                     |  |

| V <sub>IL</sub> | Input LOW Voltage              | 11.100  | (CON     | 0.8  | V    | Guaranteed Input LOW Voltage for All Inputs                                     |                                                                         |  |

| V <sub>IK</sub> | Input Clamp Diode Voltage      | -x1 10  | -0.65    | -1.5 | V    | $V_{CC} = MIN, I_{IN} = -18 \text{ mA}$                                         |                                                                         |  |

| V <sub>OH</sub> | Output HIGH Voltage            | 2.7     | 3.5      | OM.T | N v  | $V_{CC}$ = MIN, $I_{OH}$ = MAX, $V_{IN}$ = $V_{IH}$ or $V_{IL}$ per Truth Table |                                                                         |  |

| WWW.1           | OST CONTRACT                   | WW      | 0.25     | 0.4  | V    | I <sub>OL</sub> = 4.0 mA                                                        | $V_{CC} = V_{CC} MIN,$                                                  |  |

| V <sub>OL</sub> | Output LOW Voltage             |         | 0.35     | 0.5  | V    | I <sub>OL</sub> = 8.0 mA                                                        | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>per Truth Table |  |

| , TXX V         | Input IIICH Current            |         | N.Too    | 20   | μА   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                          | = 2.7 V                                                                 |  |

| ІН Л            | Input HIGH Current             | 14      | W.10     | 0.1  | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                          | = 7.0 V                                                                 |  |

| I <sub>IL</sub> | Input LOW Current              | W       | -1XN,1   | -0.4 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                          | = 0.4 V                                                                 |  |

| los             | Short Circuit Current (Note 1) | -20     | NN T     | -100 | mA   | V <sub>CC</sub> = MAX                                                           | N 1 100 X                                                               |  |

| I <sub>CC</sub> | Power Supply Current           |         | MAL      | 23   | mΑ   | $V_{CC} = MAX$                                                                  | WWW.                                                                    |  |

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

### AC CHARACTERISTICS (T<sub>A</sub> = 25°C)

|                                      | MANN'IS ON COME                       |     | Limits   | 111.5    | V.CC |                                                   |  |  |

|--------------------------------------|---------------------------------------|-----|----------|----------|------|---------------------------------------------------|--|--|

| Symbol                               | Parameter                             | Min | Тур      | Max      | Unit | Test Conditions                                   |  |  |

| f <sub>MAX</sub>                     | Maximum Clock Frequency               | 25  | 36       | WW.      | MHz  | ON. T                                             |  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>Clock to Output | LM  | 14<br>17 | 22<br>26 | ns   | V <sub>CC</sub> = 5.0 V<br>C <sub>L</sub> = 15 pF |  |  |

| t <sub>PHL</sub>                     | Propagation Delay, MR to Output       | TW  | 19       | 30       | ns   | Y.COM.TW WWW.                                     |  |  |

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 WWW.100Y.COM.TW Http://www.100y.com.tw

H = HIGH Voltage Level

H = HIGH Volta

X = Don't Care

I = LOW ····

<sup>. –</sup> LOVV voltage level one set-up time prior to the LOW to HIGH clock transition h = HIGH voltage level one set-up time prior to the LOW to HIGH clock transition  $p_n\left(q_n\right) = \text{Lower case letters indicate the state of the referenced input for$  $p_n(q_n)$  = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to HIGH clock transition.

### AC SETUP REQUIREMENTS $(T_A = 25^{\circ}C)$

|                  | TAW. 100 COM.           | «:  | Limits | M.In  | ~√ C | DIAT. | 1                        |

|------------------|-------------------------|-----|--------|-------|------|-------|--------------------------|

| Symbol           | Parameter               | Min | Тур    | Max   | Unit | OW.I  | Test Conditions          |

| t <sub>W</sub>   | Clock or MR Pulse Width | 20  | 1      | TXN   | ns   | COMIT | A                        |

| ts               | Mode Control Setup Time | 30  |        | A     | ns   | oM.   |                          |

| t <sub>s</sub>   | Data Setup Time         | 20  |        | MAN   | ns   | CON   | $V_{CC} = 5.0 \text{ V}$ |

| t <sub>h</sub>   | Hold time, Any Input    | 0   |        | WW    | ns   | N.COM |                          |

| t <sub>rec</sub> | Recovery Time           | 25  |        | TAI V | ns   | OV.CO |                          |

### **DEFINITIONS OF TERMS**

SETUP  $TIME(t_s)$  —is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from LOW to HIGH in order to be recognized and transferred to the outputs.

HOLD TIME (t<sub>h</sub>) — is defined as the minimum time following the clock transition from LOW to HIGH that the logic level must be maintained at the input in order to ensure

continued recognition. A negative HOLD TIME indicates that the correct logic level may be released prior to the clock transition from LOW to HIGH and still be recognized.

RECOVERY TIME (t<sub>rec</sub>) — is defined as the minimum time required between the end of the reset pulse and the clock transition from LOW to HIGH in order to recognize and transfer HIGH Data to the Q outputs.

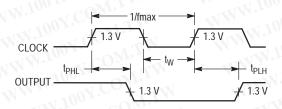

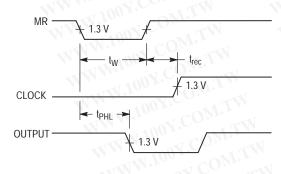

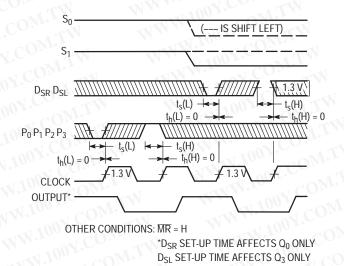

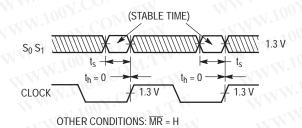

### **AC WAVEFORMS**

The shaded areas indicate when the input is permitted to change for predictable output performance

OTHER CONDITIONS:  $S_1 = L$ ,  $\overline{MR} = H$ ,  $S_0 = H$

Figure 1. Clock to Output Delays Clock Pulse Width and f<sub>max</sub>

OTHER CONDITIONS:  $S_0$ ,  $S_1$  = H  $P_0$  =  $P_1$  =  $P_2$  =  $P_3$  = H

Figure 2. Master Reset Pulse Width, Master Reset to Output Delay and Master Reset to Clock Recovery Time

Figure 3. Setup (t<sub>s</sub>) and Hold (t<sub>h</sub>) Time for Serial Data (D<sub>SR</sub>, D<sub>SL</sub>) and Parallel Data (P<sub>0</sub>, P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub>)

Figure 4. Setup (t<sub>s</sub>) and Hold (t<sub>h</sub>) Time for S Input

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## 100Y.COM.TW

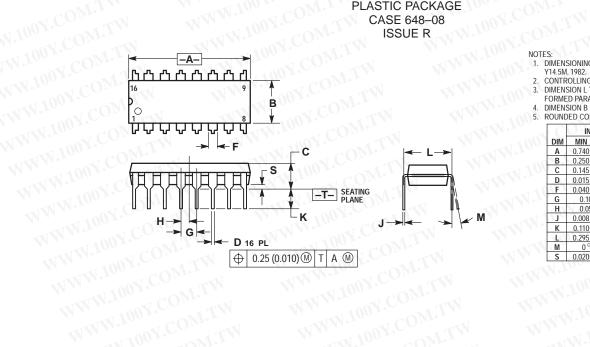

### PACKAGE DIMENSIONS W.100Y.COM.TW PLASTIC PACKAGE CASE 648-08 ISSUE R

WWW.100Y.COM.TW

WWW.100Y.CO.

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. CONTROLLING DIMENSION: INCH.

|  |     |       | OES NOT<br>NERS OP |        | MOLD   |

|--|-----|-------|--------------------|--------|--------|

|  |     | INC   | HES                | MILLIN | IETERS |

|  | DIM | MIN   | MAX                | MIN    | MAX    |

|  | Α   | 0.740 | 0.770              | 18.80  | 19.55  |

|  | В   | 0.250 | 0.270              | 6.35   | 6.85   |

|  | С   | 0.145 | 0.175              | 3.69   | 4.44   |

|  | D   | 0.015 | 0.021              | 0.39   | 0.53   |

|  | F   | 0.040 | 0.70               | 1.02   | 1.77   |

|  | G   | 0.100 | BSC                | 2.54   | BSC    |

|  | -H  | 0.050 | BSC                | 1.27   | BSC    |

|  | J   | 0.008 | 0.015              | 0.21   | 0.38   |

|  | K   | 0.110 | 0.130              | 2.80   | 3.30   |

|  | 4LO | 0.295 | 0.305              | 7.50   | 7.74   |

|  | M   | 0°    | 10°                | 0°     | 10 °   |

|  | S   | 0.020 | 0.040              | 0.51   | 1.01   |

力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

WW.100Y.COM.TW

WWW.100Y.COM.TW

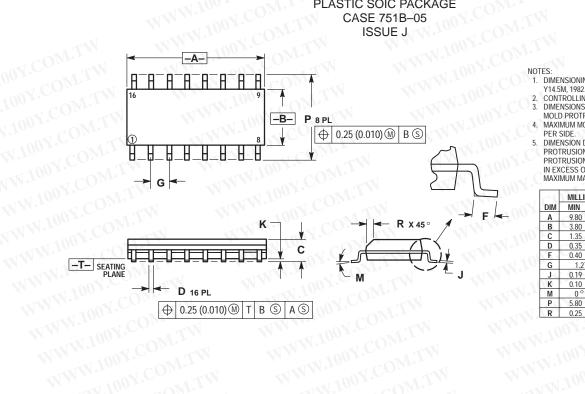

### W.100Y.COM.TW **D SUFFIX** PLASTIC SOIC PACKAGE CASE 751B-05 ISSUE J

WWW.100Y.COM.TW

Y.COM.TW

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

| 40  | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386     | 0.39  |  |

| В   | 3.80   | 4.00   | 0.150     | 0.15  |  |

| С   | 1.35   | 1.75   | 0.054     | 0.06  |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016     | 0.04  |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.19   | 0.25   | 0.008     | 0.00  |  |

| K   | 0.10   | 0.25   | 0.004     | 0.00  |  |

| M   | 0.0    | 7°     | 0 °       | 7     |  |

| Р   | 5.80   | 6.20   | 0.229     | 0.24  |  |

| R   | 0.25   | 0.50   | 0.010     | 0.019 |  |

力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

.100Y.COM.T

Http://www. 100y. com. tw