### SN54276, SN74276 QUADRUPLE J.K FLIP-FLOPS

OCTOBER 1976 - REVISED MARCH 1988

| $\begin{array}{c c} \hline CLR & \begin{bmatrix} 1 & 1 & 20 \\ 1 & 2 & 19 \end{bmatrix} 4J \\ \hline 1LLK & 3 & 18 \end{bmatrix} 4CLK \\ \hline 1K & 4 & 17 \end{bmatrix} 4K \\ \hline 10 & 5 & 16 \end{bmatrix} 4Q \\ 2Q & 6 & 15 \end{bmatrix} 3Q \\ 2K & 7 & 14 \end{bmatrix} 3K \\ 2CLK & 8 & 13 \end{bmatrix} 3CLK \\ 2J & 9 & 12 \end{bmatrix} 3J \\ 2WP & 0 & 11 \end{bmatrix} PPF \\ \hline$ | SN54276 J PACKAGE<br>SN74276 N PACKAGE<br>(TOP VIEW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                      | $ \begin{array}{c} 1J \\ 1J \\ 1CLK \\ 1\overline{K} \\ 1\overline{K} \\ 1\overline{K} \\ 20 \\ 20 \\ 2\overline{K} \\ 1\overline{K} \\ 1\overline{K} \\ 1\overline{K} \\ 10 \\ 20 \\ 2\overline{K} \\ 1\overline{K} \\ 10 \\ 2\overline{K} \\ 10 \\ 1\overline{K} \\ 10 \\ 10 \\ 1\overline{K} \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 1$ |

特力材料 886-3-5753170 勝 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

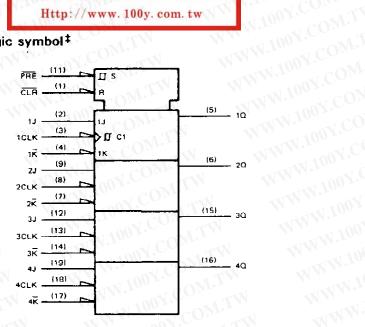

logic symbol<sup>‡</sup>

\*This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### SDLS091

- Four J-K Flip-Flops in a Single Package .... Can Reduce FF Package Count by 50%

- Separate Negative-Edge-Triggered Clocks with Hysteresis . . . Typically 200 mV

- Typical Clock Input Frequency ... 50 MHz ٠

- **Fully Buffered Outputs**

#### description

WWW.100Y.COM.TW

These quadruple TTL J-K flip-flops incorporate a number of third-generation IC features that can simplify system design and reduce flip-flop package count by up to 50%. They feature hysteresis at each clock input, fully buffered outputs, and direct clear capability, and are presettable through a buffer that also features an input hysteresis loop. The negativeedge-triggering clocks are directly compatible with earlier Series 54/74 single and dual pulse-triggered flip-flops. These circuits can be used to emulate D- or T-type flip-flops by hard-wiring the inputs, or to implement asychronous sequential functions.

The SN54276 is characterized for operation over the full military temperature range of -55°C to 125°C; the SN74726 is characterized for operation from 0°C to 70°C.

FUNCTION TABLE (EACH FLIP-FLOP)

| COMMON | INPUTS | INP     | UTS | ~   | OUTPUT         |

|--------|--------|---------|-----|-----|----------------|

| PRE    | CLR    | CLK J K |     | ٩   |                |

| L      | н      | ×       | X   | X   | н              |

| н      | L      | X       | X   | x   | LCO            |

| ι      | L      | x       | x   | x   | HT             |

| н      | н      | 4 <     | L.  | н   | 0 <sub>0</sub> |

| н      | н      | 4       | н   | H   | н              |

| н      | н      | L L     | L   | L   |                |

| н      | Ĥ      | 1       | н   | CL. | TOGGLE         |

| н      | н      | н       | ×   | x   | QÜ             |

<sup>†</sup> This configuration is nonstable; that is, it may not persist when preset and clear return to their inactive (high) level.

PRODUCTION DATA documents centain information current as of publication date. Products conform to specifications per the terms of Texes instruments standard warranty. Production processing daes not necessarily include testing of all parameters.

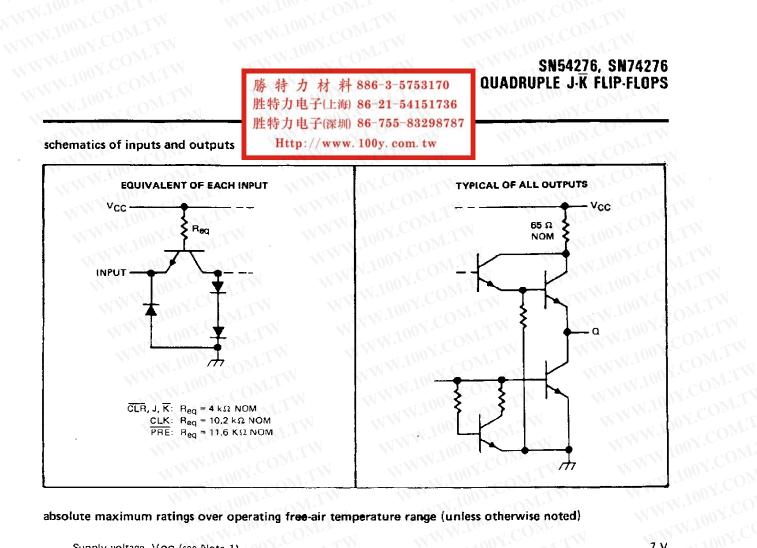

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

WWW.100Y.COM.TW WWW.100Y.COM.TW WWW.100Y.COM.TW

| Supply voltage, VCC (see Note 1)                               | 7V              |

|----------------------------------------------------------------|-----------------|

| Input voltage                                                  |                 |

| Operating free-air temperature range: SN54276                  |                 |

|                                                                | 0° C to 70° C   |

| Storage temperature range                                      | – 65°C to 150°C |

| 1: Voltage values are with respect to network ground terminel. |                 |

|                                                                |                 |

|                                                                |                 |

|                                                                |                 |

NOTE 1: Voltage values are with respect to network ground terminel. WWW.100Y.COM.TW WWW.100Y

. . . . .

# 100Y.COM.T SN54276, SN74276 QUADRUPLE J-K FLIP-FLOPS

# 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

recommended operating conditions

| IN NO.                             |                                 | SN54276 |         |        | SN74276 |      |       |      |  |

|------------------------------------|---------------------------------|---------|---------|--------|---------|------|-------|------|--|

|                                    | CON.I.                          | MIN     | NOM     | MAX    | MIN     | NOM  | MAX   | UNIT |  |

| Supply voltage, VCC                | CO TH WI                        | 4.5     | 5       | 5.5    | 4,75    | 5    | 5.25  | V    |  |

| High-level output curre            | ent, IOH                        | 1111-2  | A CO    | 800    |         | NN.  | -800  | μA   |  |

| Low-level output curre             | nt, IOL                         |         | 10.2    | 16     |         |      | 16    | mA   |  |

| Clock frequency                    | N No.                           | 0       | M.V.    | 35     | 0       | ALV. | 35    | MHz  |  |

| 10                                 | Clock high                      | 13.5    | 100     | .OM    | 13,5    | - TN | 1.10  |      |  |

| Pulse width, tw                    | Clock low                       | 15      | 1001.   | LIC    | 15      | N.   | -1100 | ns   |  |

| WW.L                               | Preset or clear low             | 12      | -       | COR    | 12      |      | 111.  |      |  |

|                                    | J, K inputs                     | 31      | x 100 F | -M.    | 34      |      |       | ns   |  |

| Setup time, t <sub>su</sub>        | Clear and preset inactive state | 104     |         |        | 101     |      | 1     | 1.15 |  |

| Input hold time, th                | .to com.                        | 101     | 1.10    | -1 CON | 104     |      | WW.   | ns   |  |

| Operating free-air temperature, TA |                                 | -55     | a10     | 125    | 0       |      | 70    | °C   |  |

WW.100

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      |                                        | TEST CO                                            | MIN                                                 | TYPI | MAX   | UNIT |    |

|----------------|----------------------------------------|----------------------------------------------------|-----------------------------------------------------|------|-------|------|----|

| √н             | High-level input voltage               |                                                    | NWW. ON.                                            | 2    | W     | NN   | V  |

| VIL            | Low-level input voltage                |                                                    |                                                     | CON  | 1     | 0.8  | V  |

| VIK            | Input clamp voltage                    | VCC = MIN,                                         | 1 <sub>1</sub> = -12 mA                             |      | A.M.  | -1.5 | V  |

| ∨он            | High-level output voltage              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -800 µA | 2.4  | 3.4   | 1    | v  |

| VOL            | Low-level output voltage               | V <sub>CC</sub> = MIN,<br>V <sub>1L</sub> = 0.8 V, | VIH = 2 V,<br>IOL = 16 mA                           | N.CO | 0.2   | 0,4  | V  |

| 4              | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5,5 V                              | 101. | TIM   | 1    | mА |

| <u>-</u><br>Чн | High-level input current               | VCC = MAX,                                         | V1 = 2.4 V                                          | S C  | 0     | 40   | μA |

| ηL             | Low-level input current                | VCC - MAX,                                         | V <sub>1</sub> = 0.4 V                              | 00 - | -M.L  | -1.6 | mA |

| los            | Short-circuit autput current§          | V <sub>CC</sub> = MAX                              | AM.                                                 | -30  | 10 11 |      | mА |

| Icc            | Supply current                         | V <sub>CC</sub> = MAX                              | Var                                                 | 100  | 60    | 81   | mA |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $\ddagger$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. EWW.100Y.COM.

§Not more than one output should be shorted at a time.

# switching characteristics, VCC = 5 V, TA = 25 °C

| ~~~                                  | PARAMETER                                                       | TEST CONDITIONS            | MIN    | TYP  | MAX | UNIT |

|--------------------------------------|-----------------------------------------------------------------|----------------------------|--------|------|-----|------|

| f                                    | Maximum clock frequency                                         |                            | 35     | 50   | 1   | MH2  |

| tmax                                 | Propagation delay time, low-to-high-level output from preset    | C <sub>1</sub> = 15 pF,    | To     | 15   | 25  | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation delay time, high-to-low-level output from clear     | $R_{\rm L} = 400 \Omega$ . | 1100   | 18   | 30  | ns   |

| tPLH                                 | Propagation delay time, low-to-high level output from clock     | See Note 2                 |        | 17   | 30  | ns   |

| <sup>t</sup> PHL                     | Propagation delay time, high-to-low level output from clock     |                            | \$1.70 | 20   | 30  | ns   |

|                                      | : Load circuits and voltage waveforms are shown in Section 1.   | The Mr.                    |        | 001. | Mo  |      |

|                                      | ECISIC CREDITZ AND ADDRAGE MAREIGNING THE STOWN IN OCCURINATION |                            |        |      |     |      |

|                                      |                                                                 |                            |        |      |     |      |

|                                      |                                                                 |                            |        |      |     |      |

NOTE 2: Load circuits and voltage waveforms are shown in Section 1. WWW.100Y.COM.TW WWW.100Y.C

#### IMPORTANT NOTICE

100Y.COM Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other guality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safequards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

> 勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

100Y.COM

WW.100Y.COM.T Copyright © 1996, Texas Instruments Incorporated WWW.100Y.COM.TW

### TEXAS INSTRUMENTS www.ti.com

PACKAGE OPTION ADDENDUM

## 勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

2-Apr-2007

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|-----------------------------|

| SN74276DW        | OBSOLETE              | SOIC            | DW                 | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276DWR       | OBSOLETE              | SOIC            | DW                 | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276DWR       | OBSOLETE              | SOIC            | DW                 | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276N         | OBSOLETE              | V PDIP          | N                  | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276N         | OBSOLETE              | PDIP            | N                  | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276N3        | OBSOLETE              | PDIP            | Ν                  | 20                  | TBD                     | Call TI          | Call TI                     |

| SN74276N3        | OBSOLETE              | PDIP            | N                  | 20                  | TBD                     | Call TI          | Call TI                     |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

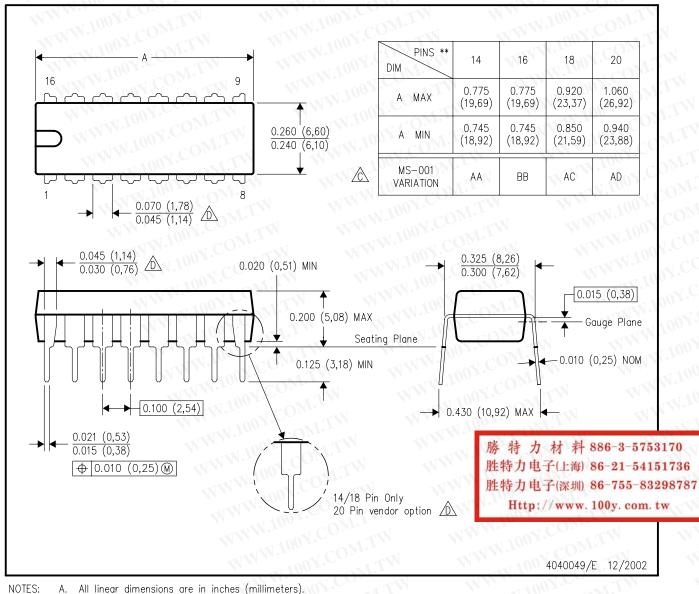

# N (R-PDIP-T\*\*) 16 PINS SHOWN

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\Delta$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

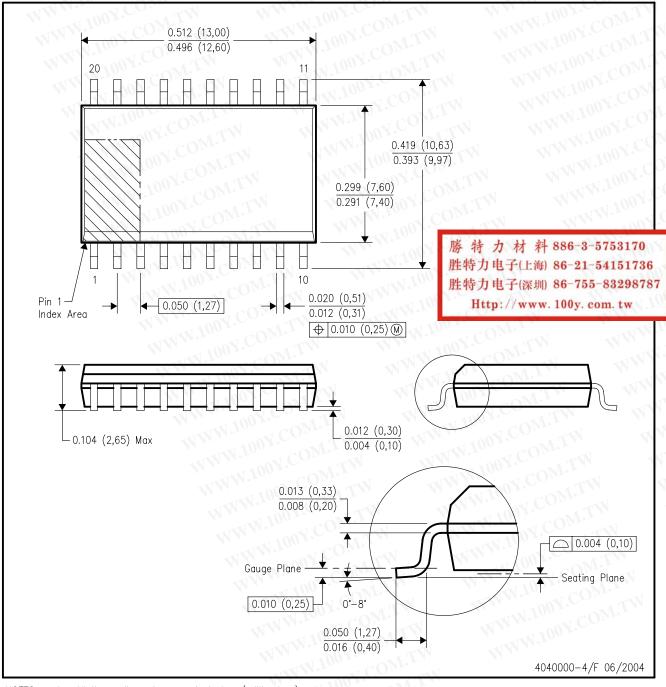

DW (R-PDSO-G20)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AC.