# TL16C451, TL16C452 ASYNCHRONOUS COMMUNICATIONS ELEMENTS

SLLS053C - MAY 1989 - REVISED AUGUST 1999

- Integrates Most Communications Card Functions From the IBM PC/AT™ or Compatibles With Single- or Dual-Channel Serial Ports

- TL16C451 Consists of One TL16C450 Plus Centronix Printer Interface

- TL16C452 Consists of Two TL16C450s Plus a Centronix-Type Printer Interface

- Fully Programmable Serial Interface Characteristics:

- 5-, 6-, 7-, or 8-Bit Characters

- Even-, Odd-, or No-Parity Bit Generation and Detection

- 1-, 1 1/2-, or 2 Stop-Bit Generation

- Programmable Baud Rate (dc to 256 kbit/s)

- Fully Double Buffered for Reliable Asynchronous Operation

# description

The TL16C451 and TL16C452 provide single- and dual-channel (respectively) serial interfaces along with a single Centronix-type parallel-port interface. The serial interfaces provide a serial-to-parallel conversion for data received from a peripheral device or modem and a parallel-to-serial conversion for data transmitted by a CPU. The parallel interface provides a bidirectional parallel data port that fully conforms to the requirements for a Centronix-type printer interface. A CPU can read the status of the asynchronous communications element (ACE) interfaces at any point in the operation. The status includes the state of the modem signals (CTS, DSR, RLSD, and RI) and any changes to these signals that have occurred since the last time they were read, the state of the transmitter and receiver including errors detected on received data, and printer status. The TL16C451 and TL16C452 provide control for modem signals (RTS and DTR), interrupt enables, baud rate programming, and parallel-port control signals.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IBM PC/AT is a trademark of International Business Machines Corporation.

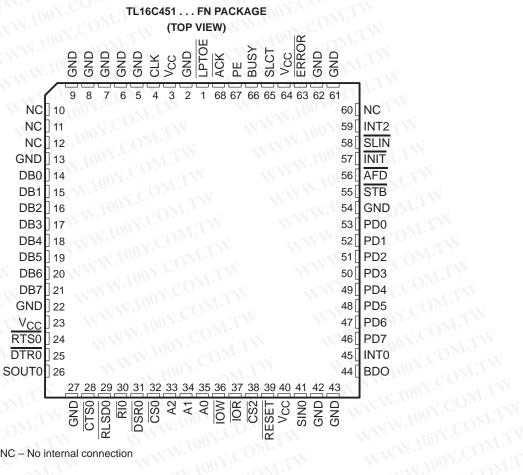

NC - No internal connection

WWW.100Y.COM

胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

WWW.100Y.COM.TW

## TL16C452...FN PACKAGE (TOP VIEW)

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

WWW.100X.COM.

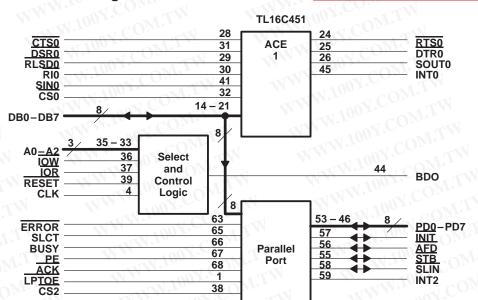

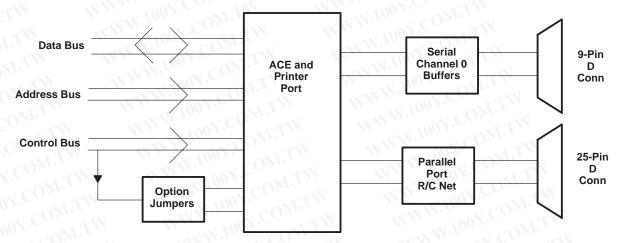

# TL16C451 functional block diagram

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www. 100y. com. tw

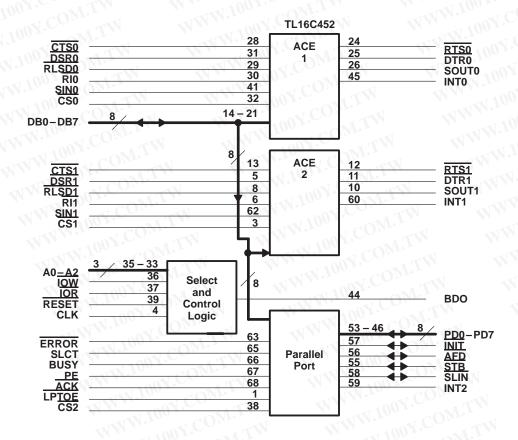

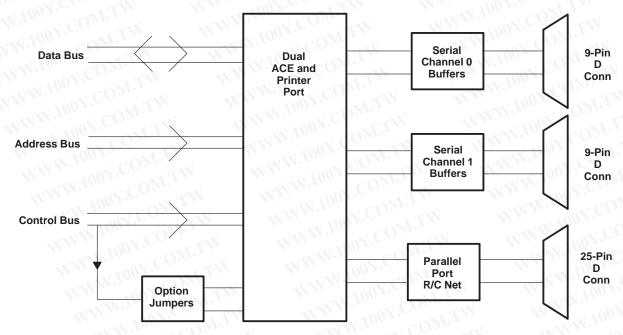

# TL16C452 functional block diagram

## **Terminal Functions**

| TERMIN<br>NAME†                      | NO.            | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0<br>A1<br>A2                       | 35<br>34<br>33 | N.M.) | Register select. A0, A1, and A2 are used during read and write operations to select the register to read from or write to. Refer to Table 1 for register addresses, also refer to the chip select signals (CSO, CS1, CS2).                                                                                                                                                                                                                                      |

| ACK                                  | 68             | WW    | Printer acknowledge. ACK goes low to indicate that a successful data transfer has taken place. It generates a printer port interrupt during its positive transition.                                                                                                                                                                                                                                                                                            |

| ĀFD                                  | 56             | 1/0   | Printer autofeed. AFD is an open-drain line that provides the printer with a low signal when continuous-form paper is to be autofed to the printer. An internal pullup is provided.                                                                                                                                                                                                                                                                             |

| BDO                                  | 44             | 0     | Bus buffer output. BDO is active (high) when the CPU is reading data. When active, this output can disable an external transceiver.                                                                                                                                                                                                                                                                                                                             |

| BUSY                                 | 66             | T     | Printer busy. BUSY is an input line from the printer that goes high when the printer is not ready to accept data.                                                                                                                                                                                                                                                                                                                                               |

| CLK                                  | 4              | I/O   | External clock. CLK connects the ACE to the main timing reference.                                                                                                                                                                                                                                                                                                                                                                                              |

| CS0<br>CS1<br>CS2 [V <sub>CC</sub> ] | 32<br>3<br>38  | I     | Chip selects. Each chip select enables read and write operations to its respective channel. CS0 and CS1 select serial channels 0 and 1, respectively, and CS2 selects the parallel port.                                                                                                                                                                                                                                                                        |

| CTS0<br>CTS1 [GND]                   | 28<br>13       | I     | Clear to send. CTSx is an active-low modem status signal. Its state can be checked by reading bit 4 (CTS) of the modem status register. Bit 0 (DCTS) of the modem status register indicates that this signal has changed states since the last read from the modem status register. If the modem status interrupt is enabled when CTSx changes state, an interrupt is generated.                                                                                |

| DB0 – DB7                            | 14 – 21        | 1/0   | Data bus. Eight 3-state data lines provide a bidirectional path for data, control, and status information between the TL16C451/TL16C452 and the CPU. DB0 is the least significant bit (LSB).                                                                                                                                                                                                                                                                    |

| DSR0<br>DSR1 [GND]                   | 31<br>5        |       | Data set ready. DSRx is an active-low modem status signal. Its state can be checked by reading bit 5 (DSR) of the modem status register. Bit 1 (DDSR) of the modem status register indicates that this signal has changed states since the last read from the modem status register. If the modem status interrupt is enabled when the DSRx changes state, an interrupt is generated.                                                                           |

| DTR0<br>DTR1 [NC]                    | 25<br>11       | M.T   | Data terminal ready. DTRx, when active (low), informs a modem or data set that the ACE is ready to establish communication. DTRx is placed in the active state by setting the DTR bit of the modem control register. DTRx is placed in the inactive state either as a result of a reset or during loop mode operation or clearing bit 0 (DTR) of the modem control register.                                                                                    |

| ERROR                                | 63             | COM   | Printer error. ERROR is an input line from the printer. The printer reports an error by holding this line low during the error condition.                                                                                                                                                                                                                                                                                                                       |

| INIT                                 | 57             | I/O   | Printer initialize. INIT is an open-drain line that provides the printer with a signal that allows the printer initialization routine to be started. An internal pullup is provided.                                                                                                                                                                                                                                                                            |

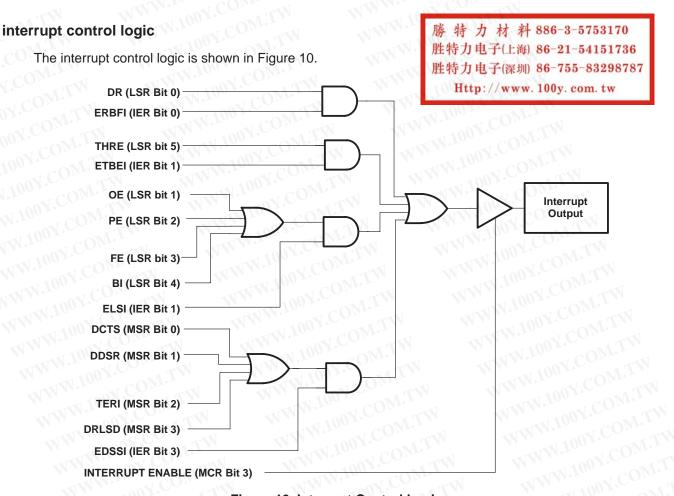

| INT0<br>INT1 [NC]                    | 45<br>60       | VOX.  | Interrupt. INTx is an active-high 3-state output that is enabled by bit 3 of the MCR. When active, INTx informs the CPU that the ACE has an interrupt to be serviced. Four conditions that cause an interrupt to be issued are: a receiver error, received data is available, the transmitter holding register is empty, and an enabled modem status interrupt. The INTx output is reset (low) either when the interrupt is serviced or as a result of a reset. |

| INT2                                 | 59             | 100   | Printer port interrupt. INT2 is an active-high 3-state output generated by the positive transition of ACK. It is enabled by bit 4 of the write control register.                                                                                                                                                                                                                                                                                                |

| ĪOR                                  | 37             | N.100 | Data read strobe. When IOR input is active (low) while the ACE is selected, the CPU is allowed to read status information or data from a selected ACE register.                                                                                                                                                                                                                                                                                                 |

| ĪOW                                  | 36             | W.M   | Data write strobe. When IOW input is active (low) while the ACE is selected, the CPU is allowed to write control words or data into a selected ACE register.                                                                                                                                                                                                                                                                                                    |

| LPTOE                                | 1              |       | Parallel data output enable. When low, LPTOE enables the write data register to the PD0-PD7 lines. A high puts the PD0-PD7 lines in the high-impedance state allowing them to be used as inputs. LPTOE is usually tied low for printer operation.                                                                                                                                                                                                               |

<sup>†</sup> Names shown in brackets are for the TL16C451.

# **Terminal Functions (continued)**

| NAMET                   | IAL<br>NO.                     | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|--------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD0-PD7                 | 53-46                          | I/O              | Parallel data bits (0-7). These eight lines provide a byte-wide input or output port to the system. The eight lines are held in a high-impedance state when LPTOE is high.                                                                                                                                                                                                                                                                  |

| PEON                    | 67                             | MM               | Printer paper empty. This is an input line from the printer that goes high when the printer runs out of paper.                                                                                                                                                                                                                                                                                                                              |

| RESET                   | 39                             | 1                | Reset. When active (low), RESET clears most ACE registers and sets the state of various output signals. Refer to Table 2.                                                                                                                                                                                                                                                                                                                   |

| <u>RI0</u><br>RI1 [GND] | 30<br>6                        | I                | Ring indicator. RIx is an active-low modem status signal. Its state can be checked by reading bit 6 (RI) of the modem status register. Bit 2 (TERI) of the modem status register indicates that the RIx input has transitioned from a low to a high state since the last read from the modem status register. If the modem status interrupt is enabled when this transition occurs, an interrupt is generated.                              |

| RLSD0<br>RLSD1 [GND]    | 29<br>8                        |                  | Receive line signal detect. RLSDx is an active-low modem status signal. Its state can be checked by reading bit 7 of the modem status register. Bit 3 (DRLSD) of the modem status register indicates that this signal has changed states since the last read from the modem status register. If the modem status interrupt is enabled when RLSDx changes state, an interrupt is generated. This bit is low when a data carrier is detected. |

| RTS0<br>RTS1 [NC]       | 24<br>12                       | 11/1             | Request to send. When active (low), RTSx informs the modem or data set that the ACE is ready to transmit data. RTSx is set to its active state by setting the RTS modem control register bit and is set to its inactive (high) state either as a result of a reset or during loop mode operations or by clearing bit 1 (RTS) of the modem control register.                                                                                 |

| SIN0<br>SIN1 [GND]      | 41<br>62                       | 1-1<br>1         | Serial input. SINx is a serial data input from a connected communications device.                                                                                                                                                                                                                                                                                                                                                           |

| SLCT                    | 65                             | N.J              | Printer selected. SLCT is an input line from the printer that goes high when the printer has been selected.                                                                                                                                                                                                                                                                                                                                 |

| SLIN                    | 58                             | I/O              | Printer select. SLIN is an open-drain line that selects the printer when it is active (low). An internal pullup is provided on this line.                                                                                                                                                                                                                                                                                                   |

| SOUT0<br>SOUT1 [NC]     | 26<br>10                       |                  | Serial output. SOUTx is a composite serial data output to a connected communication device. SOUTx is set during a reset.                                                                                                                                                                                                                                                                                                                    |

| STB                     | 55                             | 1/0              | Printer strobe. STB is an open-drain line that provides communication synchronization between the TL16C451/TL16C452 and the printer. When it is active (low), it provides the printer with a signal to latch the data currently on the parallel port. An internal pullup is provided on this line.                                                                                                                                          |

| Vcc V                   | 23,40,<br>64                   | JY.C             | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND                     | 2,7,9<br>22,27,42,<br>43,54,61 | <sup>700</sup> Å | Supply common                                                                                                                                                                                                                                                                                                                                                                                                                               |

<sup>†</sup> Names shown in brackets are for the TL16C451.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 WWW.100Y.COM.TW Http://www. 100y. com. tw WWW.100Y.COM.TW

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see No | ote 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.5 V to 7 V  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Input voltage range at any input, VI          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.5 V to 7 V  |

| Output voltage range, VO                      | Anna COMMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.5 V to 7 V  |

| Continuous total power dissipation            | M.T.Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1100 mW       |

| Operating free-air temperature rang           | ge, T <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0°C to 70°C   |

| Storage temperature range, T <sub>stq</sub> . | To Comment the second s | 65°C to 150°C |

| Case temperature for 10 seconds.              | Text. 2. Year and the same and  | 260°C         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

| 001.00 JULY W. 1001. WILL W. M. 111001.        | MIN  | NOM  | MAX  | UNIT |

|------------------------------------------------|------|------|------|------|

| Supply voltage, V <sub>CC</sub>                | 4.75 | 5    | 5.25 | V    |

| High-level Input voltage, VIH                  | 2    |      | Vcc  | V    |

| Low-level Input voltage, V <sub>IL</sub>       | -0.5 | Mir  | 0.8  | V    |

| Operating free-air temperature, T <sub>A</sub> | 0    | TIME | 70   | °C   |

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| Mari             | PARAMETER                     | TEST CONDITIONS                                                                                                                                                         | MIN TYPT MAX   | UNIT |

|------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| WWw              | CONTRA                        | $I_{OH} = -0.4 \text{ mA on DB0-DB7}$                                                                                                                                   | 100Y.CO        |      |

| Variation        | Lieb lovel output voltage     | $I_{OH} = -2 \text{ mA to } 4 \text{ mA on PD0-PD7}$                                                                                                                    | Name of COMM   | W v  |

| VOH              | High-level output voltage     | $I_{OH} = -0.2$ mA on INIT, AFD, STB, and SLIN                                                                                                                          | 2.4            | V    |

|                  |                               | $I_{OH} = -0.2$ mA on all other outputs                                                                                                                                 | 100 Y. COM     |      |

| VII.             | MM. TO COM                    | I <sub>OL</sub> = 4 mA on DB0-DB7                                                                                                                                       | W 100 X .Co.   | TW   |

|                  |                               | I <sub>OL</sub> = 12 mA on PD0-PD7                                                                                                                                      | MM. TO WY. COM |      |

| VOL              | Low-level output voltage      | $\frac{I_{OL}}{AFD} = \frac{10 \text{ mA on } INIT,}{STB, \text{ and } SLIN \text{ (see Note 2)}}$                                                                      | NWW.1007 0.4   | V    |

|                  |                               | I <sub>OL</sub> = 2 mA on all other outputs                                                                                                                             | WWW. CON.CO    | JN-  |

| l <sub>lkg</sub> | Input leakage current         | $V_{CC} = 5.25 \text{ V},$ $V_{SS} = 0,$ $V_{I} = 0 \text{ to } 5.25 \text{ V},$ All other terminals floating                                                           | ±10            | μА   |

| I <sub>OZ</sub>  | High-impedance output current | $V_{CC}$ = 5.25 V, $V_{SS}$ = 0, $V_{O}$ = 0 to 5.25 V, Chip selected and in write mode, or chip deselected                                                             | ±20            | μΑ   |

| lcc              | Supply current                | V <sub>CC</sub> = 5.25 V, V <sub>SS</sub> = 0, SIN, DSR, RLSD, CTS, and RI at 2 V, All other inputs at 0.8 V, XTAL1 at 4 MHz, No load on outputs, Baud rate = 50 kbit/s | 10             | mA   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 \,^{\circ}\text{C}$ .

# system timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                 | PARAMETER                                                               | FIGURE | MIN MAX | UNIT |

|-----------------|-------------------------------------------------------------------------|--------|---------|------|

| t <sub>cR</sub> | Cycle time, read (t <sub>W7</sub> + t <sub>d8</sub> + t <sub>d9</sub> ) | COM    | 175     | ns   |

NOTE 1: All voltage values are with respect to GND.

NOTE 2: INIT, AFD, STB, and SLIN are open-collector output terminals that each have an internal pullup to V<sub>CC</sub>. This generates a maximum of 2 mA of internal I<sub>OL</sub> per terminal. In addition to this internal current, each terminal sinks at least 10 mA while maintaining the V<sub>OL</sub> specification of 0.4 V maximum.

# TL16C451, TL16C452 ASYNCHRONOUS COMMUNICATIONS ELEMENTS

SLLS053C - MAY 1989 - REVISED AUGUST 1999

| ns |

|----|

| ns |

|    |

# system switching characteristics over recommended ranges of supply voltage and operating free-air temperature

| PARAMETER                                                   | FIGURE                                                                                                                                    | TEST CONDITIONS                                                                                                                                                   | MIN                                                                                                                                                                                                                | MAX                                                                                                                                                                                                                   | UNIT                                                                                                                                                                                                                    |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay time, data (D0 – D7) valid before read (IOR)↑         | 3                                                                                                                                         | C <sub>L</sub> = 100 pF                                                                                                                                           | J.                                                                                                                                                                                                                 | 60                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                      |

| Delay time, floating data (D0 – D7) valid after read (IOR)↑ | 3                                                                                                                                         | C <sub>L</sub> = 100 pF                                                                                                                                           | 0                                                                                                                                                                                                                  | 60                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                      |

| Read to driver disable, <del>IOR</del> ↓ to BD0↓            | 3                                                                                                                                         | C <sub>L</sub> = 100 pF                                                                                                                                           | ~1 C                                                                                                                                                                                                               | 60                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                      |

|                                                             | Delay time, data (D0 – D7) valid before read ( <del>IOR</del> )↑ Delay time, floating data (D0 – D7) valid after read ( <del>IOR</del> )↑ | Delay time, data (D0 – D7) valid before read $(\overline{IOR})^{\uparrow}$ 3 Delay time, floating data (D0 – D7) valid after read $(\overline{IOR})^{\uparrow}$ 3 | Delay time, data (D0 – D7) valid before read $(\overline{IOR})^{\uparrow}$ 3 $C_L = 100 \text{ pF}$<br>Delay time, floating data (D0 – D7) valid after read $(\overline{IOR})^{\uparrow}$ 3 $C_L = 100 \text{ pF}$ | Delay time, data (D0 – D7) valid before read ( $\overline{IOR}$ ) $\uparrow$ 3 $C_L = 100 \text{ pF}$ Delay time, floating data (D0 – D7) valid after read ( $\overline{IOR}$ ) $\uparrow$ 3 $C_L = 100 \text{ pF}$ 0 | Delay time, data (D0 – D7) valid before read $(\overline{IOR})^{\uparrow}$ 3 $C_L = 100 \text{ pF}$ 60 Delay time, floating data (D0 – D7) valid after read $(\overline{IOR})^{\uparrow}$ 3 $C_L = 100 \text{ pF}$ 0 60 |

# receiver switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                 | PARAMETER                                                    | FIGURE | TEST CONDITIONS         | MIN   | MAX | UNIT           |

|-----------------|--------------------------------------------------------------|--------|-------------------------|-------|-----|----------------|

| t <sub>d7</sub> | Delay time, RCLK↑ to sample clock↑                           | 4      |                         | W.Inc | 100 | ns             |

| t <sub>d8</sub> | Delay time, stop (sample clock)↑ to set interrupt (INTRPT)↑  | 400    | TAN M.                  | WW-10 | 1.0 | RCLK<br>cycles |

| t <sub>d9</sub> | Delay time, read RBR/LSR (IOR)↑ to reset interrupt (INTRPT)↓ | 4      | C <sub>L</sub> = 100 pF | WW.   | 140 | ns             |

# transmitter switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                        | FIGURE | TEST CONDITIONS         | MIN | MAX | UNIT              |

|------------------|------------------------------------------------------------------|--------|-------------------------|-----|-----|-------------------|

| <sup>t</sup> d10 | Delay time, initial write THR (IOW)↑ to transmit start (SOUT)↓   | 5      | I.COM.TW                | 8   | 24  | baudout<br>cycles |

| <sup>t</sup> d11 | Delay time, stop (SOUT) low to interrupt (INTRPT)↑               | 5      | M.COW.TW                | 8   | 8   | baudout<br>cycles |

| t <sub>d12</sub> | Delay time, write THR (IOW)↓ to reset interrupt (INTRPT) low     | 5      | C <sub>L</sub> = 100 pF |     | 140 | ns                |

| t <sub>d13</sub> | Delay time, initial write (IOW)↑ to THRE interrupt (INTRPT)↑     | 5      | TOOX:COM:TW             | 16  | 32  | baudout cycles    |

| t <sub>d14</sub> | Delay time, read IIR (IOR)↑ to reset THRE interrupt (INTRPT) low | 5      | C <sub>L</sub> = 100 pF | s1  | 140 | ns                |

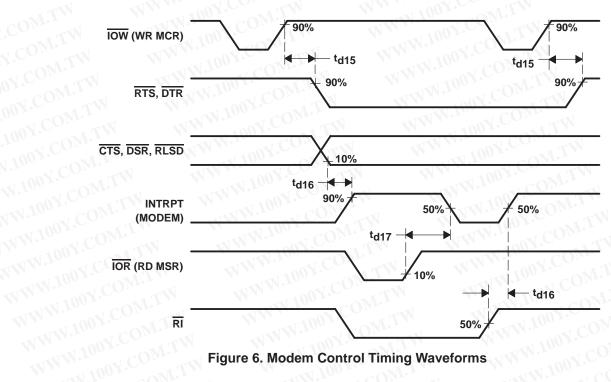

# modem control switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                           | FIGURE | TEST CONDITIONS         | MIN MA | UNIT |

|------------------|-----------------------------------------------------|--------|-------------------------|--------|------|

| t <sub>d15</sub> | Delay time, write MCR (IOW)↑ to output (RTS, DTS)↓↑ | 6      | C <sub>L</sub> = 100 pF | 10     | ) ns |

| <sup>t</sup> d16 | Delay time, modem input (CTS, DSR, RLSD)↑ to set interrupt (INTRPT) high | 6 | C <sub>L</sub> = 100 pF | 170 | ns |

|------------------|--------------------------------------------------------------------------|---|-------------------------|-----|----|

| t <sub>d17</sub> | Delay time, read MSR (IOR)↑ to reset interrupt (INTRPT) low              | 6 | C <sub>L</sub> = 100 pF | 140 | ns |

COM.TW

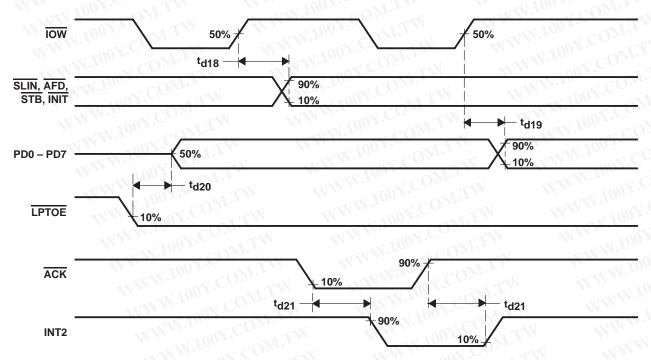

# parallel port switching characteristics over recommended ranges of supply voltage and operating free-air temperature

| $O_{Mr}$         | PARAMETER                                                                                            | FIGURE | TEST CONDITIONS         | MIN MAX | UNIT |

|------------------|------------------------------------------------------------------------------------------------------|--------|-------------------------|---------|------|

| <sup>t</sup> d18 | Delay time, write parallel port control (SLIN, AFD, STB, INIT)↓↑ to output (IOW) high                | 7      | C <sub>L</sub> = 100 pF | 60      | ns   |

| t <sub>d19</sub> | Delay time, write parallel port data $(P0 - P7)\downarrow\uparrow$ to output $(\overline{IOW})$ high | 7      | C <sub>L</sub> = 100 pF | 60      | ns   |

| t <sub>d20</sub> | Delay time, output enable to data, PD0 – PD7 valid after LPTOE↓                                      | 7      | C <sub>L</sub> = 100 pF | 60      | ns   |

| t <sub>d21</sub> | Delay time, ACK↓↑ to INT2↓↑                                                                          | 7      | C <sub>L</sub> = 100 pF | 100     | ns   |

#### PARAMETER MEASUREMENT INFORMATION

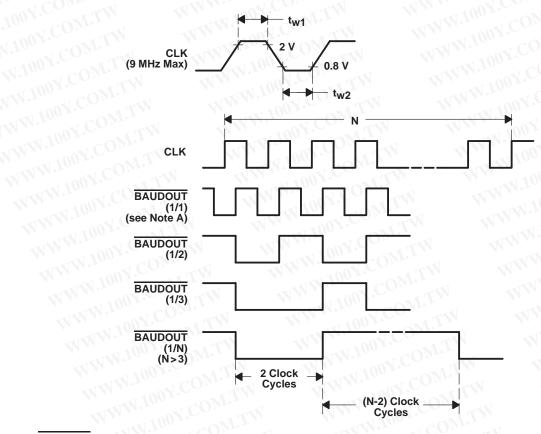

NOTE A: BAUDOUT is an internally generated signal used in the receiver and transmitter circuits to synchronize data.

Figure 1. Baud Generator Timing Waveforms

#### PARAMETER MEASUREMENT INFORMATION

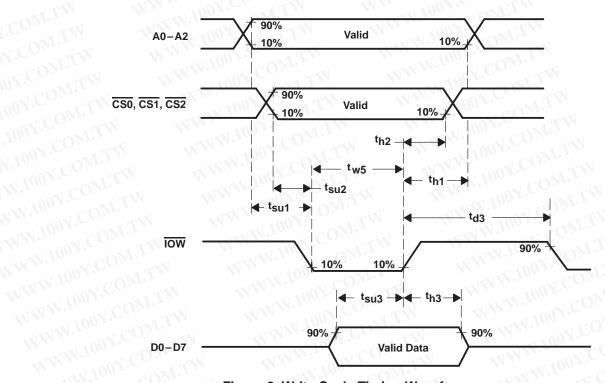

Figure 2. Write Cycle Timing Waveforms

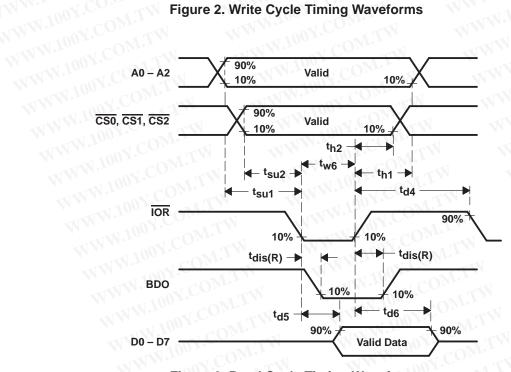

Figure 3. Read Cycle Timing Waveforms

#### PARAMETER MEASUREMENT INFORMATION

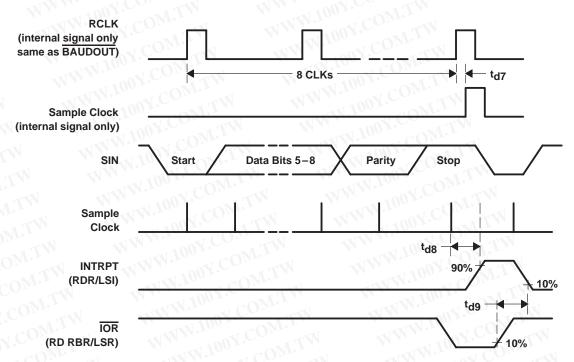

**Figure 4. Receiver Timing Waveforms**

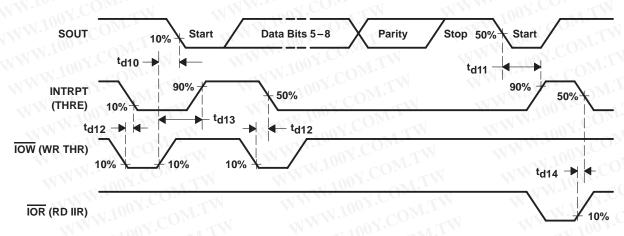

**Figure 5. Transmitter Timing Waveforms**

### PARAMETER MEASUREMENT INFORMATION

**Figure 6. Modem Control Timing Waveforms**

Figure 7. Parallel Port Timing Waveforms

### **APPLICATION INFORMATION**

Figure 8. Basic TL16C451 Test Configuration

Figure 9. Basic TL16C452 Test Configuration

#### PRINCIPLES OF OPERATION

**Table 1. Register Selection**

| DLAB | A2   | A1 (  | A0    | REGISTER                                                     |

|------|------|-------|-------|--------------------------------------------------------------|

| 0    | LIN. | Inh   | CCINI | Receiver buffer (read), transmitter holding register (write) |

| 0    | L    | 100x  | Н     | Interrupt enable register                                    |

| Х    | L    | Hoo   | L     | Interrupt identification register (read only)                |

| Ţ X  | L    | Ĥ     | J.H   | Line control register                                        |

| X    | H    | VI Ja | -,LC( | Modem control register                                       |

| X    | Н    | -L11  | Н     | Line status register                                         |

| X    | H W  | Ĥ     | 000   | Modem status register                                        |

| X    | Н    | Н     | H     | Scratch register                                             |

| 1    | L    | L     | Tor   | Divisor latch (LSB)                                          |

| 1    | L    | N. L  | THU   | Divisor latch (MSB)                                          |

uvisor latch (MSB)

.... uvisor latch access bit (DLAB) is the most significant bit signal is controlled by writing to this bit location (see Table 3). † The divisor latch access bit (DLAB) is the most significant bit of the line control register. The DLAB

Table 2. ACE Reset Functions

| REGISTER/SIGNAL                             | RESET CONTROL               | RESET STATE                                                                  |

|---------------------------------------------|-----------------------------|------------------------------------------------------------------------------|

| Interrupt enable register                   | RESET                       | All bits cleared (0-3 forced and 4-7 permanent)                              |

| Interrupt identification register           | RESET                       | Bit 0 is set, bits 1 and 2 are cleared, and bits 3-7 are permanently cleared |

| Line control register                       | RESET                       | All bits cleared                                                             |

| Modem control register                      | RESET                       | All bits cleared                                                             |

| Line status register                        | RESET                       | Bits 5 and 6 are set, all other bits are cleared                             |

| Modem status register                       | RESET                       | Bits 0-3 are cleared, bits 4-7 are input signals                             |

| SOUT                                        | RESET                       | High                                                                         |

| INTRPT (receiver error flag)                | Read LSR/RESET              | Low                                                                          |

| INTRPT (received data available)            | Read RBR/RESET              | Low                                                                          |

| INTRPT (transmitter holding register empty) | Read IIR/Write<br>THR/RESET | Low COMITY WWW.10                                                            |

| INTRPT (modem status changes)               | Read MSR/RESET              | Low                                                                          |

| OUT2 (interrupt enable)                     | RESET                       | High                                                                         |

| RTS                                         | RESET                       | High COMM                                                                    |

| DTR ONLY                                    | RESET                       | High                                                                         |

| OUT1                                        | RESET                       | High                                                                         |

| Scratch register                            | RESET                       | No effect                                                                    |

| Divisor latch (LSB and MSB) registers       | RESET                       | No effect                                                                    |

| Receiver buffer registers                   | RESET                       | No effect                                                                    |

| Transmitter holding registers               | RESET                       | No effect                                                                    |

#### PRINCIPLES OF OPERATION

# accessible registers

The system programmer, using the CPU, has access to and control over any of the ACE registers that are summarized in Table 3. These registers control ACE operations, receive data, and transmit data. Descriptions of these registers are given in Table 3.

**Table 3. Summary of Accessible Registers**

|            |                                                  | 1/1/1/                                    | 40117.                                                         |                                                   |                                             | TER ADDRE                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V -                                                     |                     |                           |                |

|------------|--------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|---------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------|---------------------------|----------------|

|            | O DLAB = 0                                       | O DLAB = 0                                | 1 DLAB = 0                                                     | 2                                                 | 3                                           | 4                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                       | 7                   | O DLAB = 1                | 1 DLAB = 1     |

| Bit<br>No. | Receiver<br>Buffer<br>Register<br>(Read<br>Only) | Transmitter Holding Register (Write Only) | Interrupt<br>Enable<br>Register                                | Interrupt<br>Ident.<br>Register<br>(Read<br>Only) | Line<br>Control<br>Register                 | Modem<br>Control<br>Register       | Line<br>Status<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Modem<br>Status<br>Register                             | Scratch<br>Register | Divisor<br>Latch<br>(LSB) | Latch<br>(MSB) |

| NV.        | RBR                                              | THR                                       | IER                                                            | IIR                                               | LCR                                         | MCR                                | LSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MSR                                                     | SCR                 | DLL                       | DLM            |

| 100        | Data Bit 0 <sup>†</sup>                          | Data Bit 0                                | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBF) | "0" If<br>Interrupt<br>Pending                    | Word<br>Length<br>Select<br>Bit 0<br>(WLSO) | Data<br>Terminal<br>Ready<br>(DTR) | Data<br>Ready<br>(DR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Delta<br>Clear<br>to Send<br>(DCTS)                     | Bit 0               | Bit 0                     | Bit 8          |

|            | Data Bit 1                                       | Data Bit 1                                | Enable Transmitter Holding Register Empty Interrupt (ETBE)     | Interrupt<br>ID<br>Bit (0)                        | Word<br>Length<br>Select<br>Bit 1<br>(WLS1) | Request<br>to Send<br>(RTS)        | Overrun<br>Error<br>(OE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Delta<br>Data<br>Set<br>Ready<br>(DDSR)                 | Bit 1               | Bit 1                     | Bit 9          |

| 2          | Data Bit 2                                       | Data Bit 2                                | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ELSI)       | Interrupt<br>ID<br>Bit (1)                        | Number of<br>Stop Bits<br>(STB)             | Out 1                              | Parity<br>Error<br>(PE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Trailing<br>Edge Ring<br>Indicator<br>(TERI)            | Bit 2               | Bit 2                     | Bit 10         |

| 3          | Data Bit 3                                       | Data Bit 3                                | Enable<br>Modem<br>Status<br>Interrupt<br>(EDSSI)              | 0                                                 | Parity<br>Enable<br>(PEN)                   | Out 2<br>(Interrupt<br>Enable)     | Framing<br>Error<br>(FE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Delta<br>Receive<br>Line<br>Signal<br>Detect<br>(DRLSD) | Bit 3               | Bit 3                     | Bit 11         |