# TLC5620C, TLC5620I QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS081E - NOVEMBER 1994 - REVISED NOVEMBER 2001

- Four 8-Bit Voltage Output DACs

- 5-V Single-Supply Operation

- Serial Interface

- High-Impedance Reference Inputs

- Programmable 1 or 2 Times Output Range

- Simultaneous Update Facility

- Internal Power-On Reset

- Low-Power Consumption

- Half-Buffered Output

## applications

- Programmable Voltage Sources

- Digitally Controlled Amplifiers/Attenuators

- Mobile Communications

- Automatic Test Equipment

- Process Monitoring and Control

- Signal Synthesis

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## description

The TLC5620C and TLC5620I are quadruple 8-bit voltage output digital-to-analog converters (DACs) with buffered reference inputs (high impedance). The DACs produce an output voltage that ranges between either one or two times the reference voltages and GND, and the DACs are monotonic. The device is simple to use, running from a single supply of 5 V. A power-on reset function is incorporated to ensure repeatable start-up conditions.

Digital control of the TLC5620C and TLC5620I are over a simple three-wire serial bus that is CMOS compatible and easily interfaced to all popular microprocessor and microcontroller devices. The 11-bit command word comprises eight bits of data, two DAC-select bits, and a range bit, the latter allowing selection between the times 1 or times 2 output range. The DAC registers are double buffered, allowing a complete set of new values to be written to the device, then all DAC outputs are updated simultaneously through control of LDAC. The digital inputs feature Schmitt triggers for high noise immunity.

The 14-terminal small-outline (D) package allows digital control of analog functions in space-critical applications. The TLC5620C is characterized for operation from 0°C to 70°C. The TLC5620I is characterized for operation from -40°C to 85°C. The TLC5620C and TLC5620I do not require external trimming.

## **AVAILABLE OPTIONS**

| PACKAGE       |                      |                    |  |  |  |  |  |  |

|---------------|----------------------|--------------------|--|--|--|--|--|--|

| CO TA         | SMALL OUTLINE<br>(D) | PLASTIC DIP<br>(N) |  |  |  |  |  |  |

| 0°C to 70°C   | TLC5620CD            | TLC5620CN          |  |  |  |  |  |  |

| -40°C to 85°C | TLC5620ID            | TLC5620IN          |  |  |  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

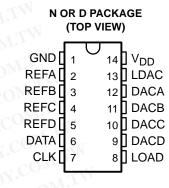

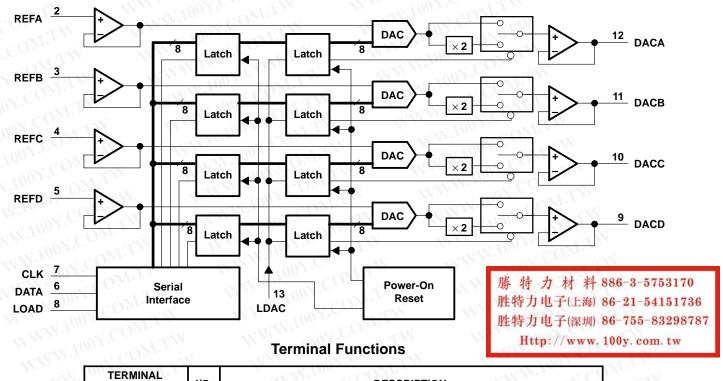

## functional block diagram

| TERMINAL |              | 1/0  | DESCRIPTION                                                                                                                                                                                                   |

|----------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.          |      | W 100 5 BEGONII HON                                                                                                                                                                                           |

| CLK      | 7<br>COM     |      | Serial interface clock. The input digital data is shifted into the serial interface register on the falling edge of the clock applied to the CLK terminal.                                                    |

| DACA     | 12           | 0    | DAC A analog output                                                                                                                                                                                           |

| DACB     | 11           | 0    | DAC B analog output                                                                                                                                                                                           |

| DACC     | 10           | 0    | DAC C analog output                                                                                                                                                                                           |

| DACD     | 9            | 0    | DAC D analog output                                                                                                                                                                                           |

| DATA     | 6<br>100 Y.C |      | Serial interface digital data input. The digital code for the DAC is clocked into the serial interface register serially. Each data bit is clocked into the register on the falling edge of the clock signal. |

| GND      | 101          | Jo   | Ground return and reference terminal                                                                                                                                                                          |

| LDAC     | 13           | N.C  | Load DAC. When the LDAC signal is high, no DAC output updates occur when the input digital data is read into the serial interface. The DAC outputs are only updated when LDAC is taken from high to low.      |

| LOAD     | 8            | 100X | Serial Interface load control. When LDAC is low, the falling edge of the LOAD signal latches the digital data into the output latch and immediately produces the analog voltage at the DAC output terminal.   |

| REFA 🦪   | 2            | 40   | Reference voltage input to DAC A. This voltage defines the output analog range.                                                                                                                               |

| REFB     | 3            | r I  | Reference voltage input to DAC B. This voltage defines the output analog range.                                                                                                                               |

| REFC     | 4            | VYO  | Reference voltage input to DAC C. This voltage defines the output analog range.                                                                                                                               |

| REFD     | 5            | 11   | Reference voltage input to DAC D. This voltage defines the output analog range.                                                                                                                               |

| $V_{DD}$ | 14           | ĬÌ,  | Positive supply voltage                                                                                                                                                                                       |

WWW.100

## detailed description

The TLC5620 is implemented using four resistor-string DACs. The core of each DAC is a single resistor with 256 taps, corresponding to the 256 possible codes listed in Table 1. One end of each resistor string is connected to the GND terminal and the other end is fed from the output of the reference input buffer. Monotonicity is maintained by use of the resistor strings. Linearity depends upon the matching of the resistor elements and upon the performance of the output buffer. Since the inputs are buffered, the DACs always present a high-impedance load to the reference source.

Each DAC output is buffered by a configurable-gain output amplifier that can be programmed to times 1 or times 2 gain.

On power up, the DACs are reset to CODE 0.

Each output voltage is given by:

$$V_O(DACA|B|C|D) = REF \times \frac{CODE}{256} \times (1 + RNG \text{ bit value})$$

where CODE is in the range 0 to 255 and the range (RNG) bit is 0 or 1 within the serial control word.

| D7 | D6  | D5       | D4   | D3     | D2     | D1  | D0   | OUTPUT VOLTAGE          |

|----|-----|----------|------|--------|--------|-----|------|-------------------------|

| 0  | 0   | 0        | 0    | 0      | 0      | 0   | 0    | GND                     |

| 0  | 0   | 0        | 0    | 0      | 0      | 0   | 1    | (1/256) × REF (1+RNG)   |

|    | •   | • "      | •    | 0£ $N$ | 0 7.   | CON |      | , M.100                 |

| TV | •   | •        | W.Y. | 1      | 00-7   | •   | (T.) | W W 100                 |

| 0  | 1   | 1        | 1    | 1      | 1      | .9  | 1    | (127/256) × REF (1+RNG) |

| 1  | 0   | 0        | 0    | 0      | 0      | 0   | 0    | (128/256) × REF (1+RNG) |

| 1. | LA  | •        | •    |        | V.1.0V | •   | 0.1  | •                       |

| •1 | TiV | •        | • 1  | 11,    | ·(()   | 07. | •    | TW . WY                 |

| 1  | 1   | <b>1</b> | 1    | 1      | 1      | 011 | 1    | (255/256) × REF (1+RNG) |

**Table 1. Ideal Output Transfer**

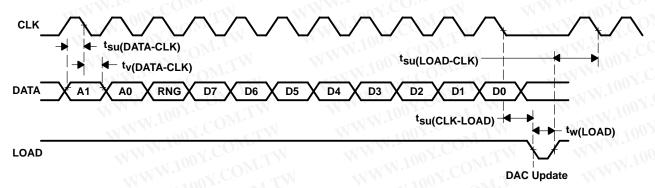

#### data interface

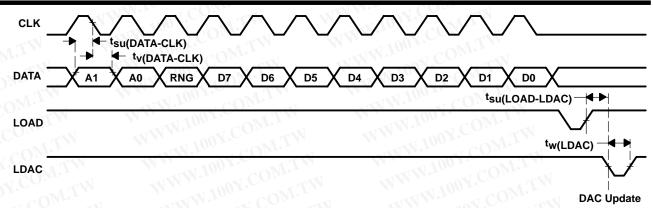

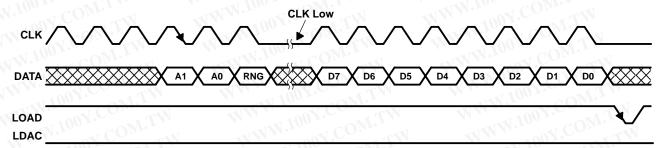

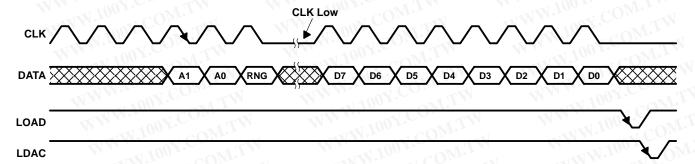

With LOAD high, data is clocked into the DATA terminal on each falling edge of CLK. Once all data bits have been clocked in, LOAD is pulsed low to transfer the data from the serial input register to the selected DAC as shown in Figure 1. When LDAC is low, the selected DAC output voltage is updated when LOAD goes low. When LDAC is high during serial programming, the new value is stored within the device and can be transferred to the DAC output at a later time by pulsing LDAC low as shown in Figure 2. Data is entered most significant bit (MSB) first. Data transfers using two 8-clock cycle periods are shown in Figures 3 and 4.

Figure 1. LOAD-Controlled Update (LDAC = Low)

Figure 2. LDAC-Controlled Update

Figure 3. Load-Controlled Update Using 8-Bit Serial Word (LDAC = Low)

Figure 4. LDAC-Controlled Update Using 8-Bit Serial Word

Table 2 lists the A1 and A0 bits and the selection of the updated DACs. The RNG bit controls the DAC output range. When RNG = low, the output range is between the applied reference voltage and GND, and when RNG = high, the range is between twice the applied reference voltage and GND.

**Table 2. Serial Input Decode**

| A1   | A0  | DAC UPDATED |

|------|-----|-------------|

| 0    | 0   | DACA        |

| 0    | 1   | DACB        |

| 100  | 0   | DACC        |

| )V 1 | 1.1 | DACD        |

## linearity, offset, and gain error using single-end supplies

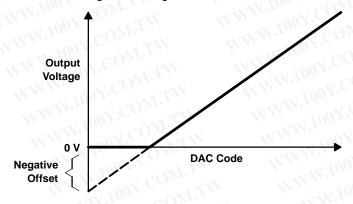

When an amplifier is operated from a single supply, the voltage offset can still be either positive or negative. With a positive offset voltage, the output voltage changes on the first code change. With a negative offset the output voltage may not change with the first code depending on the magnitude of the offset voltage.

The output amplifier attempts to drive the output to a negative voltage. However, because the most negative supply rail is ground, the output cannot drive below ground and clamps the output at 0 V.

The output voltage then remains at zero until the input code value produces a sufficient positive output voltage to overcome the negative offset voltage, resulting in the transfer function shown in Figure 5.

Figure 5. Effect of Negative Offset (Single Supply)

This offset error, not the linearity error, produces this breakpoint. The transfer function would have followed the dotted line if the output buffer could drive below ground.

For a DAC, linearity is measured between zero-input code (all inputs 0) and full-scale code (all inputs 1) after offset and full scale are adjusted out or accounted for in some way. However, single-supply operation does not allow for adjustment when the offset is negative due to the breakpoint in the transfer function. So the linearity is measured between full-scale code and the lowest code that produces a positive output voltage. The code is calculated from the maximum specification for the negative offset voltage.

# TLC5620C, TLC5620I QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS081E - NOVEMBER 1994 - REVISED NOVEMBER 2001

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## equivalent inputs and outputs

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage (V <sub>DD</sub> – GND)                          | 7 V                                             |

|-----------------------------------------------------------------|-------------------------------------------------|

| Digital input voltage range                                     |                                                 |

| Reference input voltage range, V <sub>ID</sub>                  | GND $- 0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating free-air temperature range, T <sub>A</sub> : TLC5620C | 0°C to 70°C                                     |

| TLC5620I                                                        | –40°C to 85°C                                   |

| Storage temperature range, T <sub>stq</sub>                     | –50°C to 150°C                                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                                           |

|                                                                 |                                                 |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

| MAN. CON                                                       | TW WWW. COM T                                 | MIN                 | NOM  | MAX                  | UNIT |

|----------------------------------------------------------------|-----------------------------------------------|---------------------|------|----------------------|------|

| Supply voltage, V <sub>DD</sub>                                | 4.75                                          | WW                  | 5.25 | ( V)                 |      |

| High-level input voltage, VIH                                  | W.I., W. In. COM.                             | 0.8 V <sub>DD</sub> |      | M. Jos               | V (  |

| Low-level input voltage, V <sub>IL</sub>                       | W.TW WW. 100Y.                                | 1.7                 |      | 0.8                  | V    |

| Reference voltage, V <sub>ref</sub> [A B C D]                  | O. TW WWW. 100X.CO.                           |                     | V    | V <sub>DD</sub> -1.5 | V    |

| Analog full-scale output voltage, $R_L = 10 \text{ Hz}$        | $\Omega$                                      | TW                  | 3.5  | MM                   | V.   |

| Load resistance, R <sub>L</sub>                                | COMITY                                        | 10                  |      | TWW.                 | kΩ   |

| Setup time, data input, t <sub>SU(DATA-CLK)</sub> (se          | ee Figures 1 and 2)                           | 50                  |      | 1                    | ns   |

| Valid time, data input valid after CLK $\downarrow$ , $t_{V(}$ | DATA-CLK) (see Figures 1 and 2)               | 50                  |      | M.A.                 | ns   |

| Setup time, CLK eleventh falling edge to L                     | OAD, t <sub>su(CLK-LOAD)</sub> (see Figure 1) | 50                  | N    | MM                   | ns   |

| Setup time, LOAD↑ to CLK↓, t <sub>Su(LOAD-C</sub>              | CLK) (see Figure 1)                           | 50                  | W    | WY                   | ns   |

| Pulse duration, LOAD, tw(LOAD) (see Fig                        | ure 1)                                        | 250                 | -XXI |                      | ns   |

| Pulse duration, LDAC, tw(LDAC) (see Fig                        | ure 2)                                        | 250                 | 1    |                      | ns   |

| Setup time, LOAD↑ to LDAC↓, t <sub>SU(LOAD</sub>               | 0                                             | 1.1.11              |      | ns                   |      |

| CLK frequency                                                  | WW.CO.YO                                      | W.Co.               | TW   | 1                    | MHz  |

| On the first state of the T                                    | TLC5620C                                      | 0.00                | T    | 70                   | °C   |

| Operating free-air temperature, T <sub>A</sub>                 | TLC5620I                                      | -40                 | Dir  | 85                   | °C   |

## electrical characteristics over recommended operating free-air temperature range, $V_{DD}$ = 5 V $\pm$ 5%, $V_{ref} = 2 V_1 \times 1$ gain output range (unless otherwise noted)

| TIN                    | PARAMETER                                |                      | T CONDITIONS           | MIN                       | TYP | MAX  | UNIT  |

|------------------------|------------------------------------------|----------------------|------------------------|---------------------------|-----|------|-------|

| Ин I                   | High-level input current                 | $V_I = V_{DD}$       | $V_I = V_{DD}$         |                           |     | ±10  | μΑ    |

| 111                    | Low-level input current                  | V <sub>I</sub> = 0 V | N.100 COM.             | -<1                       |     | ±10  | μΑ    |

| I <sub>O(sink)</sub>   | Output sink current                      | Each DAC or          | I.Mo. TOOLIN           | 20                        |     |      | μΑ    |

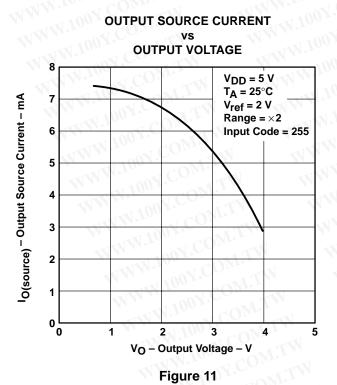

| I <sub>O(source)</sub> | Output source current                    | Each DAC 0           | uthat                  | 2                         |     |      | mA    |

| $co^{M.1}$             | Input capacitance                        | XIX XXIX             | TAMAN TOOK COM         |                           | 15  |      | nE.   |

| Ci                     | Reference input capacitance              | - 1                  |                        |                           | 15  |      | pF    |

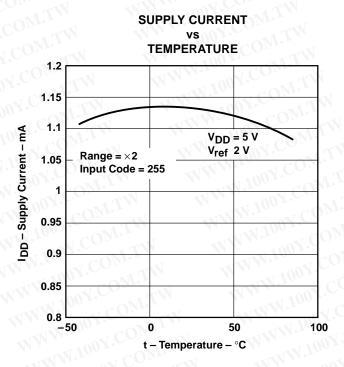

| I <sub>DD</sub>        | Supply current                           | $V_{DD} = 5 V$       | V <sub>DD</sub> = 5 V  |                           |     | 2    | mA    |

| I <sub>ref</sub>       | Reference input current                  | $V_{DD} = 5 V$       | V <sub>ref</sub> = 2 V | TI                        | N   | ±10  | μΑ    |

| EL CON                 | Linearity error (end point corrected)    | $V_{ref} = 2 V$ ,    | ×2 gain (see Note 1)   | 17.                       | W   | ±1   | LSB   |

| ED                     | Differential-linearity error             | $V_{ref} = 2 V$ ,    | ×2 gain (see Note 2)   | $O_{MT}$ .,               | - 1 | ±0.9 | LSB   |

| EZS                    | Zero-scale error                         | $V_{ref} = 2 V$ ,    | ×2 gain (see Note 3)   | 0                         | In  | 30   | mV    |

| OV.CI                  | Zero-scale-error temperature coefficient | $V_{ref} = 2 V$ ,    | ×2 gain (see Note 4)   |                           | 10  |      | μV/°C |

| EFS                    | Full-scale error                         | $V_{ref} = 2 V$ ,    | ×2 gain (see Note 5)   | $^{\circ}CO_{\mathbb{R}}$ | W   | ±60  | mV    |

| $100_{T}$              | Full-scale-error temperature coefficient | $V_{ref} = 2 V$      | ×2 gain (see Note 6)   | <1 CO                     | ±25 | N.   | μV/°C |

| PSRR                   | Power-supply rejection ratio             | See Notes 7          | See Notes 7 and 8      |                           | 0.5 | *    | mV/V  |

- Integral nonlinearity (INL) is the maximum deviation of the output from the line between zero and full scale (excluding the effects of zero code and full-scale errors).

- 2. Differential nonlinearity (DNL) is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code.

- 3. Zero-scale error is the deviation from zero voltage output when the digital input code is zero.

- $\label{eq:ZSETC} \textit{Zero-scale-error temperature coefficient is given by: ZSETC = [ZSE(T_{max}) ZSE(T_{min})]/V_{ref} \times 10^6/(T_{max} T_{min}).$

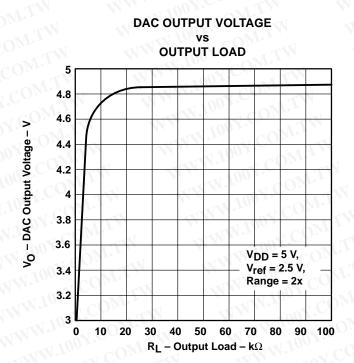

- Full-scale error is the deviation from the ideal full-scale output (V<sub>ref</sub> 1 LSB) with an output load of 10 kΩ.

Full-scale-error temperature coefficient is given by: FSETC = [FSE(T<sub>max</sub>) FSE (T<sub>min</sub>)]/V<sub>ref</sub> × 10<sup>6</sup>/(T<sub>max</sub> T<sub>min</sub>).

- 7. Zero-scale-error rejection ratio (ZSE RR) is measured by varying the VDD from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the zero-code output voltage.

- 8. Full-scale-error rejection ratio (FSE RR) is measured by varying the VDD from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the full-scale output voltage.

# operating characteristics over recommended operating free-air temperature range, $V_{DD}$ = 5 V $\pm$ 5%, $V_{ref} = 2 V_{ref} \times 1$ gain output range (unless otherwise noted)

| WW. 1007.                    | TEST CONDITIONS                                                      | MIN | TYP | MAX   | UNIT |

|------------------------------|----------------------------------------------------------------------|-----|-----|-------|------|

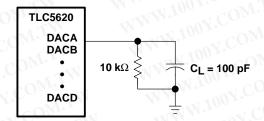

| Output slew rate             | $C_L = 100 \text{ pF},  R_L = 10 \text{ k}\Omega$                    | 41  | 1   | 001.  | V/µs |

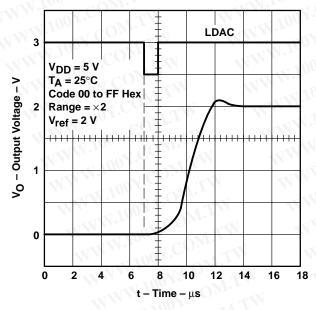

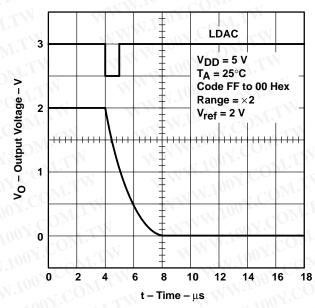

| Output settling time         | To $\pm 0.5$ LSB, $C_L = 100$ pF, $R_L = 10$ k $\Omega$ , See Note 9 | W   | 10  | You.  | μs   |

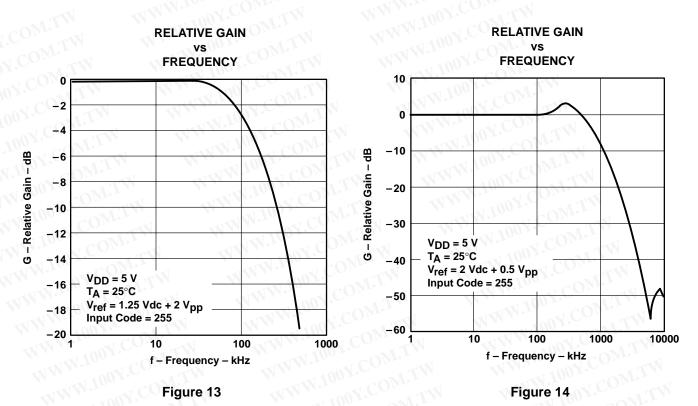

| Large-signal bandwidth       | Measured at −3 dB point                                              |     | 100 | Too   | kHz  |

| Digital crosstalk            | CLK = 1-MHz square wave measured at DACA-DACD                        |     | -50 | 1.100 | dB   |

| Reference feedthrough        | See Note 10                                                          |     | -60 | x1 10 | dB   |

| Channel-to-channel isolation | See Note 11                                                          |     | -60 | 44.   | dB   |

| Reference input bandwidth    | See Note 12                                                          |     | 100 | 111.7 | kHz  |

|                              |                                                                      |     |     |       |      |

- NOTES: 9. Settling time is the time between a LOAD falling edge and the DAC output reaching full scale voltage within +/-0.5 LSB starting from an initial output voltage equal to zero.

- 10. Reference feedthrough is measured at any DAC output with an input code = 00 hex with a V<sub>ref</sub> input = 1 V dc + 1 V<sub>pp</sub> at 10 kHz.

11. Channel-to-channel isolation is measured by setting the input code of one DAC to FF hex and the code of all other DACs to 00 hex with  $V_{ref}$  input = 1 V dc + 1  $V_{pp}$  at 10 kHz.

- 12. Reference bandwidth is the -3 dB bandwidth with an input at V<sub>ref</sub> = 1.25 V dc + 2 V<sub>pp</sub> and with a full-scale digital-input code.

胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

## PARAMETER MEASUREMENT INFORMATION

Figure 6. Slew, Settling Time, and Linearity Measurements

#### TYPICAL CHARACTERISTICS

## **POSITIVE RISE AND SETTLING TIME**

WWW.100Y.COM.TW

#### **NEGATIVE FALL AND SETTLING TIME**

Figure 8

Http://www.100y.com.tw

SLAS081E - NOVEMBER 1994 - REVISED NOVEMBER 2001

## TYPICAL CHARACTERISTICS

**DAC OUTPUT VOLTAGE** vs **OUTPUT LOAD** 3.5 V<sub>O</sub> - DAC Output Voltage - V 3 2.5 2 1.5 1  $V_{DD} = 5 V$  $V_{ref} = 3.5 V,$ 0.5 Range = 1x 10 20 30 50 60 70 80 100 0 40 90  $R_L$  - Output Load -  $k\Omega$

Figure 9

Figure 10

Figure 12

## TYPICAL CHARACTERISTICS

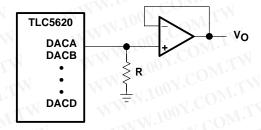

## **APPLICATION INFORMATION**

NOTE A: Resistor R  $\geq$  10 k $\Omega$

Figure 15. Output Buffering Scheme

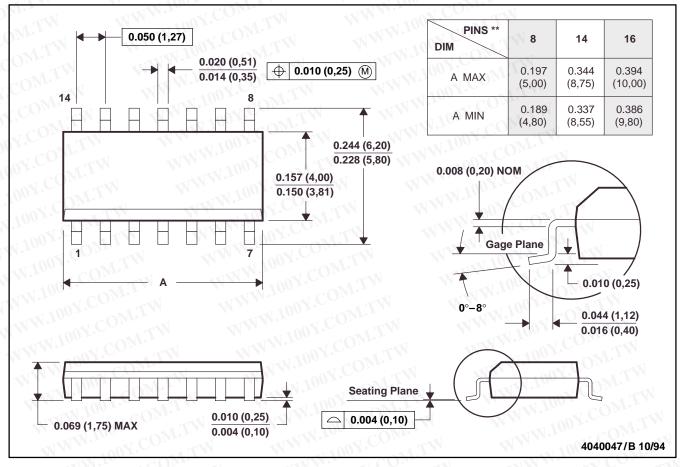

#### **MECHANICAL DATA**

## D (R-PDSO-G\*\*)

#### 14 PIN SHOWN

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Four center pins are connected to die mount pad.

- E. Falls within JEDEC MS-012

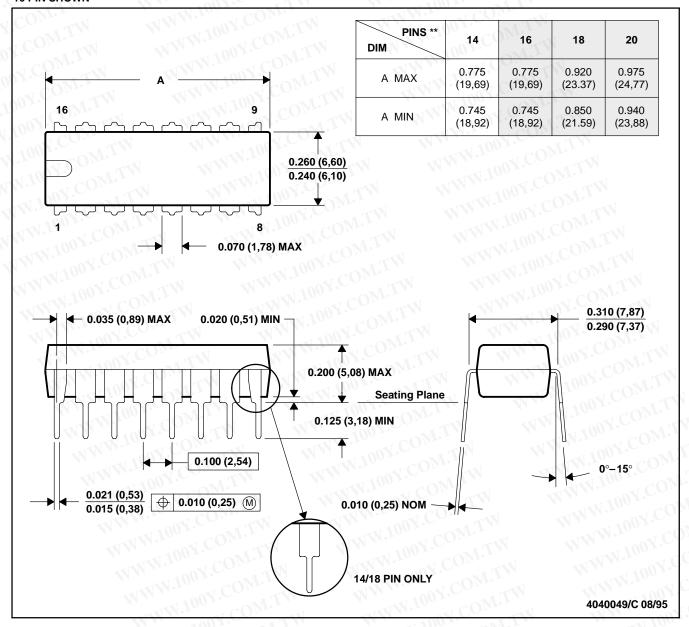

#### **MECHANICAL DATA**

## N (R-PDIP-T\*\*)

### **16 PIN SHOWN**

### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20-pin package is shorter than MS-001)

# PACKAGE OPTION ADDENDUM

com 18-Feb-2005

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Pa | ackage<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup>              |

|------------------|-----------------------|-----------------|--------------------|---------|---------------|-------------------------|------------------|-------------------------------------------|

| TLC5620CD        | ACTIVE                | SOIC            | D                  | 14      | 50            | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLC5620CDR       | ACTIVE                | SOIC            | D                  | 14      | 2500          | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLC5620CN        | ACTIVE                | PDIP            | N                  | 14      | 25            | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-NA-NA-NA                            |

| TLC5620ID        | ACTIVE                | SOIC            | OMD                | 14      | 50            | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLC5620IDR       | ACTIVE                | SOIC            | OD.                | 14      | 2500          | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLC5620IN        | ACTIVE                | PDIP            | CON                | 14      | 25            | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-NA-NA-NA                            |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - May not be currently available - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

None: Not yet available Lead (Pb-Free).

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean "Pb-Free" and in addition, uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787

Http://www.100y.com.tw

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|                        | Applications                                                                           |                                                                                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| amplifier.ti.com       | Audio                                                                                  | www.ti.com/audio                                                                                                                                                                                                             |

| dataconverter.ti.com   | Automotive                                                                             | www.ti.com/automotive                                                                                                                                                                                                        |

| dsp.ti.com             | Broadband                                                                              | www.ti.com/broadband                                                                                                                                                                                                         |

| interface.ti.com       | Digital Control                                                                        | www.ti.com/digitalcontrol                                                                                                                                                                                                    |

| logic.ti.com           | Military                                                                               | www.ti.com/military                                                                                                                                                                                                          |

| power.ti.com           | Optical Networking                                                                     | www.ti.com/opticalnetwork                                                                                                                                                                                                    |

| microcontroller.ti.com | Security                                                                               | www.ti.com/security                                                                                                                                                                                                          |

|                        | Telephony                                                                              | www.ti.com/telephony                                                                                                                                                                                                         |

|                        | Video & Imaging                                                                        | www.ti.com/video                                                                                                                                                                                                             |

|                        | Wireless                                                                               | www.ti.com/wireless                                                                                                                                                                                                          |

|                        | dataconverter.ti.com<br>dsp.ti.com<br>interface.ti.com<br>logic.ti.com<br>power.ti.com | amplifier.ti.com Audio dataconverter.ti.com Automotive dsp.ti.com Broadband interface.ti.com Digital Control logic.ti.com Military power.ti.com Optical Networking microcontroller.ti.com Security Telephony Video & Imaging |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated